改進OR1200 CPU流水線的設計①

曹凱寧,沈興浩,姬夢飛,常玉春

(吉林大學 電子科學與工程學院,長春 130012)

改進OR1200 CPU流水線的設計①

曹凱寧,沈興浩,姬夢飛,常玉春

(吉林大學 電子科學與工程學院,長春 130012)

流水線是制造高性能CPU的關鍵技術,目前被廣泛研究的OR1200是一款帶有四級流水線的免費開源CPU. 為了提高流水線的效率,針對OR1200沒有設計訪存流水段,流水線會暫停等待加載存儲類指令這個問題,在LSU操作即訪存操作模塊,為OR1200增加了訪存流水段,設計了冒險檢測和旁路單元,因此CPU在訪存階段不需要暫停,從而使OR1200變為真正的五級流水線CPU; 另一方面,當需要用加載指令加載數據的時候,會導致加載類數據冒險問題,為了解決此類冒險,設計了數據有效信號Tag,用來控制流水線暫停,對乘法計算、訪存階段以及其他不能在執行階段得到結果的運算作流水線暫停判斷,以等待數據的獲取. 通過實驗仿真證明,Tag信號暫停流水線一個時鐘后會把數據反饋回去,成功解決了必須暫停數據相關問題的暫停判斷問題.

OR1200; 流水線; 數據冒險; 數據旁路

隨著計算機系統和微電子技術的不斷發展,將整個電子應用系統集成在單一的芯片上,構成功能強大的完整片上系統(SoC),是IC產業發展的必然趨勢,也是技術發展的必然要求. 而作為SoC運算核心和控制核心的CPU核,其性能直接影響系統的整體性能,因此設計實現高性能的CPU核已成為SoC最重要的環節.

目前,國內雖然已經有了設計CPU的能力,但大多采用了國際主流CPU系列的兼容指令集與架構,比如“龍芯”和海思公司分別取得了MIPS與ARM的授權,以及去年海光獲得了x86的授權. 其中的一個重要原因是這些主流架構都擁有完整或比較完整的商業生態圈,避免了因指令集不兼容而導致CPU沒有市場的尷尬局面. 近年來,采用ARM授權方式的國內CPU廠商可以借助圍繞ARM架構的生態環境獲得較好的發展,這該模式是以犧牲了巨大的商業利益和產品安全性為代價. 因此,這種方式很大程度上限制了我國自主CPU的設計與發展. 通過對CPU設計發展進行充分的橫向(各研究機構、廠商)及縱向(時間上)研究,我們從頭設計了擁有全新的指令集架構、完善的編譯器/軟件開發環境的高性能、通用性JearCore開源CPU.Jear Core基于在學術界廣泛流行的OpenRISC架構,利用其先進的、開放性的底層架構體系,所具備的完整的開發、編譯工具鏈,從底層做起,重新改寫流水線,徹底優化現有代碼,增添輔助模塊,不斷完善和發展這種應用前景巨大的32位、高性能RISC(精簡指令集計算機)[1,2]CPU設計,并無償提供給企業進行產業化.

本文憑借JearCore CPU設計理念,以Xilinx公司的FPGA為目標器件,用Verilog語言描述了32位 的流水線CPU. CPU流水線技術是一種將指令分解為多步,并讓不同指令的各步操作重疊,從而實現幾條指令并行處理,以加速程序運行過程的技術. 每個子過程對應一個時鐘,稱為流水級或者流水段[3]. 流水線的引入提高了各個流水段的利用率,同時也產生了數據冒險的情形. 此次我們研究的 OR1200 是由 OpenCores 組織[4]開發的一個32位標量RISC. 雖然OR1200手冊[5]聲稱OR1200是五級流水線,但是由于它并沒有設計訪存流水段,因而被認為是四級流水線的CPU. 針對以上問題,我們為OR1200設計的訪存流水段,并且針對增加流水段而引起的數據冒險進行了分析和解決.

1 OR1200 的流水線以及改進

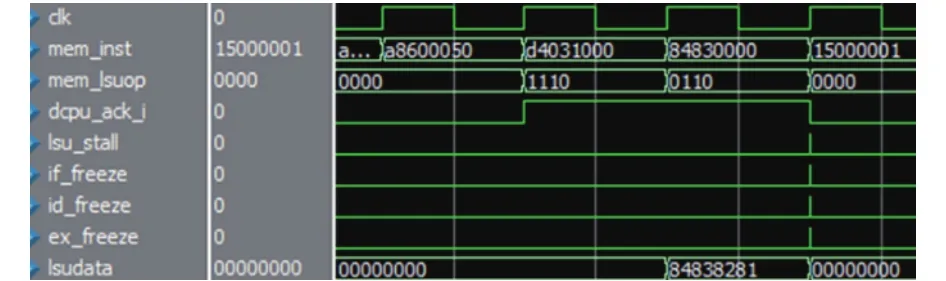

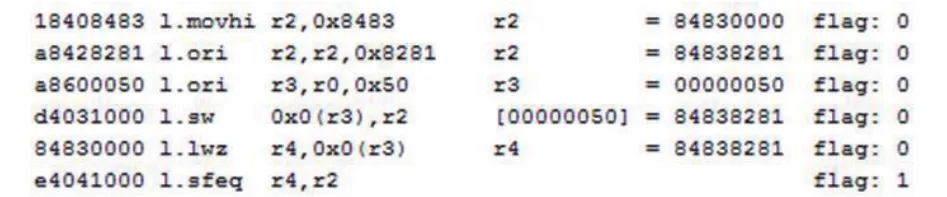

五級流水線[6]的CPU一般分為五步進行,分別是“取指”、“譯碼”、“執行”、“訪存”、“寫回”.OR1200將“執行”階段的計算得到的地址送給總線,而控制訪存階段的控制信號依然用的是執行階段的控制信號,因而造成了在訪存階段必暫停的問題[7,8],如圖1所示. 圖中ex_insn為執行階段的指令,其中“d4031000”為存儲指令 l.sw 0x0(r3),r2 的機器碼,“84830000”為加載指令 l.lwz r4,0x0(r3)的機器碼.OR1200執行訪存指令的時候通過lsu_stall判斷暫停,當總線dcpu_ack_i為1的時候訪存結束繼續執行下一條指令.

圖1 OR1200 訪存操作仿真圖

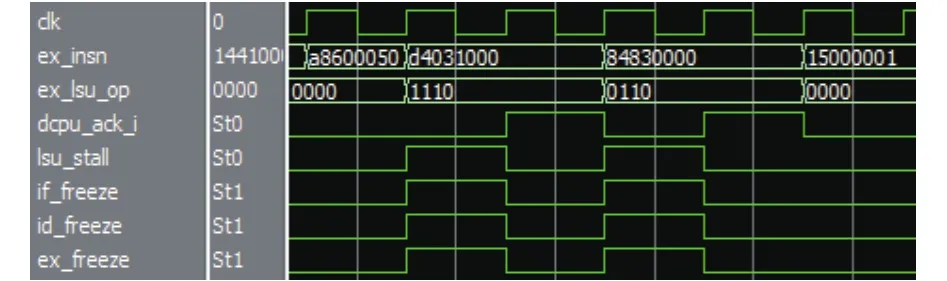

通過對OR1200改進的時候增加了訪存階段的控制信號,使得CPU在訪存階段沒有出現cache miss情形下不需要暫停[9],如圖2所示. 圖中虛線表示流水線之間的寄存器. 我們將OR1200訪存操作從執行流水段中分離出來,來解決OR1200遇到訪存操作暫停的問題. 這樣一方面提高了系統主頻; 另一方面提高了硬件模塊的利用率和吞吐量.

圖2 改進后 CPU 流水線結構圖

向改進后的CPU中輸入圖1中相同的指令,得到的仿真結果如圖3所示. 可知在執行存儲指令l.sw 0x0(r3),r2 和加載指令 l.lwz r4,0x0(r3)流水線均未暫停. lsudata為加載指令的加載結果.

圖3 改進后 CPU 訪存操作的仿真圖

2 數據相關以及旁路技術

引入流水線提高CPU效率的同時,我們會遇到流水線冒險的問題,稱之為流水線相關. 流水線相關分為:結構相關、數據相關和控制相關. 由于OR1200采用的是內部哈佛結構即分開的指令數據緩存,所以不存在結構相關. OR1200在處理分支跳轉的時候,通過暫停等待跳轉信息的到來,所以OR1200已經解決了控制相關的問題. 在增加訪存流水段以后,OR1200對于數據相關的處理電路已經不再適用了,因此我們需要重新考慮.

數據相關主要包括三種: RAW(read after write)、WAW(write after read)和 WAR(write after write). 對于五級流水線CPU而言,只有在流水線回寫階段才會寫寄存器,因此不存在WAW相關. 又因為只能在流水線譯碼階段讀寄存器、回寫階段寫寄存器,不存在WAR相關,所以五級流水線CPU一般只存在RAW相關.RAW相關有以下三種情況:

(1) 相鄰指令健存在數據相關,舉例如下:

l.ori r1,r0,0x1

l.ori r2,r1,0x0

(2) 相隔1條指令的指令間存在數據相關,舉例如下:

l.ori r1,r0,0x1

l.ori r3,r0,0x0

l.ori r2,r1,0x0

(3) 相隔2條指令的指令間存在數據相關,舉例如下:

l.ori r1,r0,0x1

l.ori r3,r0,0x0

l.ori r4,r0,0x0

l.ori r2,r1,0x0

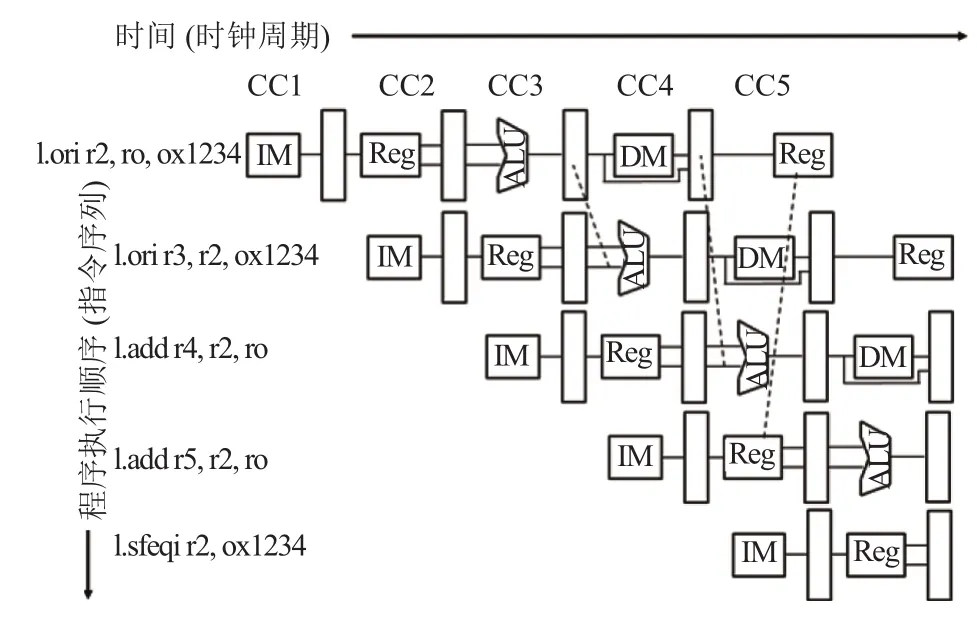

為了解決數據相關[9,10]的問題,我們引入了旁路技術[11]來解決這個問題,如圖4所示. 我們將旁路技術分為兩個部分設計,一是操作數選通器中的設計,二是在寫入寄存器堆之前使寄存器堆完成對數據的前推.

圖中第一條指令的結果需要在CC5這個時鐘寫回到寄存器堆. 而接下來的4條指令都需求這個結果.因此如果此時直接選取寄存器堆里的指令結果一定是不對的,所以在設計的操作數選通器使用旁路技術將結果前推. 這樣第二條指令可以直接從ALU計算得出的結果中得到所需的操作數,而不需要等待CPU將結果寫回寄存器. 而第三條指令則可以從MEM階段的前推數據中獲取. 第四條指令可以從WB階段的前推數據中獲取. 將指令計算的結果通過數據前推給操作數選通器,這樣便解決了RAW的問題.

圖4 旁路技術對數據相關問題的解決

3 數據相關暫停機制設計

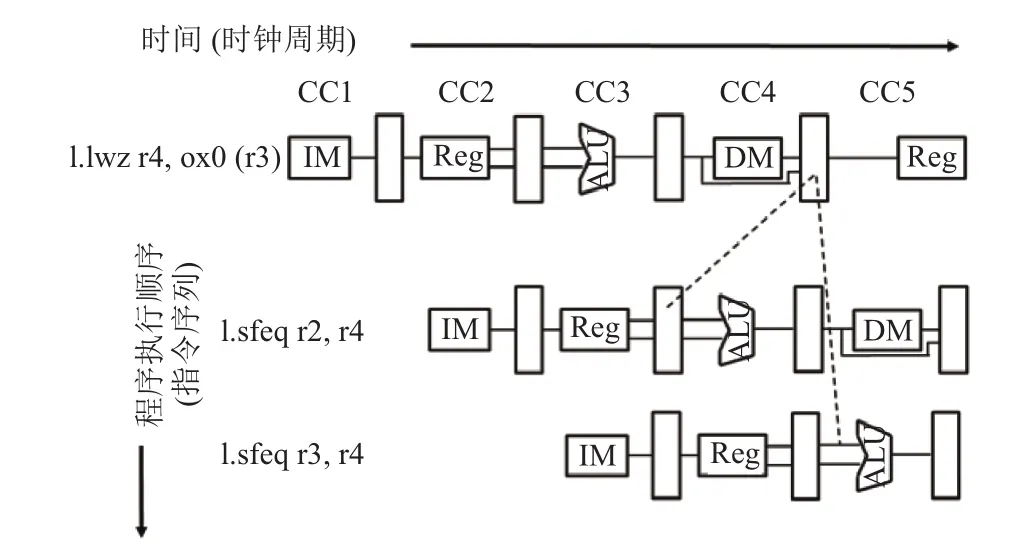

在討論數據相關問題的時候,還得考慮一個問題,就是如果第二條指令需要第一條指令的結果,但是第一條指令是一條加載指令,并不能在執行階段給出結果,必須在訪存階段才會得到結果. 而此時運行在譯碼階段的指令并不能通過將執行階段的結果前推來得到對應的操作數. 如圖5 所示. l.lwz r4,0x0(r3)的結果在CC4才能得出,而在CC3就需要這個結果,所以此時需要暫停流水線[12].

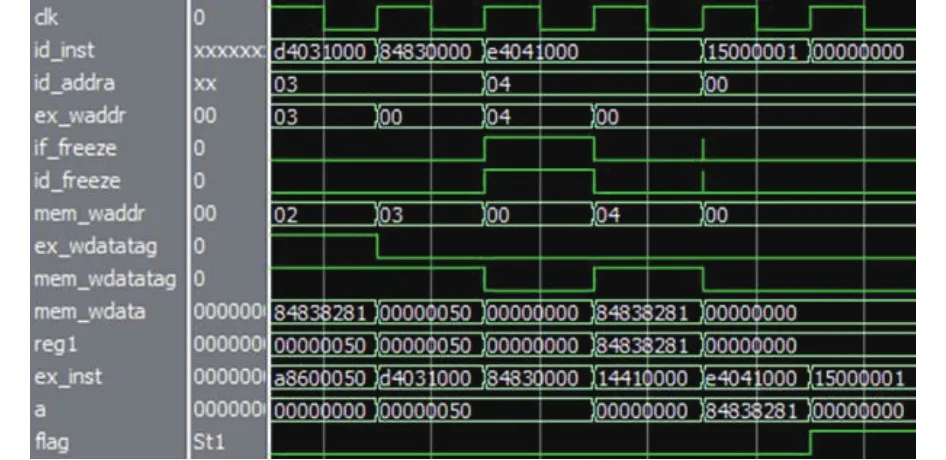

因此設計了數據有效信號tag來解決這個問題. 如圖6 所示. 在 CC3 這個時鐘,指令 l.sfeq r2,r4 的 a 操作數地址和指令l.lwz r4,0x0(r3)寫寄存器地址相同.指令l.sfeq需求指令l.lwz的結果,而此時數據是無效的,所以數據Tag為0,這時就會發出流水線暫停的請求,暫停流水線. 在 CC4 這個時鐘的時候,指令 l.lwz 獲取到了結果,這時Tag變為1,同時將結果送給指令l.sfeq,流水線解除暫停.

為此設計了匯編指令對此進行仿真,匯編指令如下:

l.movhi r2,0x8483

l.ori r2,r2,0x8281

l.ori r3,r0,0x50

l.sw 0x0(r3),r2

l.lwz r4,0x0(r3)

l.sfeq r4,r2

將匯編指令通過OR1200模擬器[13]進行仿真,得到的結果如圖7所示,l.sw將數據“r2=84838281”存儲在地址為0x50的內存地址上,然后通過加載指令l.lwz加載相同內存地址的數據保存到r4中,之后由l.sfeq比較r2和r4的結果是否相等,比較的結果為相等,因此flag信號變成1.

圖5 使用加載指令存在的數據相關

圖6 數據有效信號Tag在暫停判斷中的作用

圖7 OR1200 模擬器仿真結果

將以上指令通過modelsim仿真得到圖8. 由圖可知,指令 l.sfeq r4,r2 在解碼階段操作數 a 的地址為0x4與上一條指令 l.lwz r4,0x0(3)執行階段的地址相同,而此時 ex_wdatatag 為 0,顯示此時指令 l.lwz r4,0x0(3)并未在執行階段得到結果. 所以這時候if_freeze和id_freeze變成1,流水線的取指和解碼工作暫停一個時鐘. 當指令 l.lwz r4,0x0(3)進行到訪存階段,此時mem_wdatatag信號已經為1,表示指令得到了結果.reg1將此時mem_wdata的結果作為輸入傳遞給操作數寄存器a. 再經過一個時鐘比較指令 l.sfeq r4,r2到達訪存階段的時候flag被置為1.

圖8 數據相關暫停機制的modelsim仿真

4 結語

流水線是現代CPU中普遍采用的一種技術,它只需要增加很少的硬件就能使CPU的速度提高很多. 本文通過修改OR1200的流水線解決了OR1200通過暫停等待訪存結束的問題,針對流水線數據相關的問題重新設計了旁路判斷電路. 遇到加載類指令數據相關的時候,我們通過設計的寫寄存器數據有效信號Tag來進行寫數據有效性判斷,Tag變為1的同時將結果送給指令l.sfeq,流水線暫 停會被解除. 最終通過匯編指令對數據相關暫停機制仿真,仿真結果符合設計要求.

1Bhavsar DK. An algorithm for row-column self-repair of RAMs and its implementation in the Alpha 21264. Proc. of the 1999 IEEE International Test Conference. Washington,DC,USA. 1999. 311–318.

2Smith JE,Weiss S. Power PC 601 and Alpha 21064: A tale of two RISCs. Computer,1994,27(6): 46–58. [doi: 10.1109/2.294853]

3Hennessy JL,Patterson DA. 計算機系統結構: 量化研究方法. 鄭緯民譯. 北京: 電子工業出版社,2004.

4OpenCores.org. Home page. http://www.opencores.org.

5OR1200 OpenRISC Processo. http://opencores.org/or1k/OR1200_OpenRISC_Processo.

6王紹坤. 基于FPGA的五級流水線CPU. 計算機系統應用,2015,24(3): 18–23.

7金鵬,楊剛,胡耀. 基于 OR1200 的批處理協處理器設計.微電子學與計算機,2014,(10): 39–42.

8姚永斌. 超標量處理器設計. 北京: 清華大學出版社,2014.

9Patterson DA,Hennessy JL. Computer organization and design: The hardware/software interface. Amsterdam,Boston,USA: Morgan Kaufmann,2005.

10Gautham P,Parthasarathy R,Balasubramanian K. Lowpower pipelined MIPS processor design. Proc. of the 12th International Symposium on Integrated Circuits. Suntec,Singapore. 2009. 462–465.

11張德學,張小軍,郭華. FPGA 現代數字系統設計及應用.北京: 清華大學出版社,2015.

12甄建勇. 深入理解 OpenRISC 體系結構. 北京: 機械工業出版社,2015.

13張望亨. 基于OpenRISC1200 32位CPU的miniSoC系統設計和軟硬件驗證[碩士學位論文]. 成都: 電子科技大學,2013.

Improved Design of Pipeline CPU Based on OR1200

CAO Kai-Ning,SHEN Xing-Hao,JI Meng-Fei,CHANG Yu-Chun

(College of Electronic Science and Engineering,Jilin University,Changchun 130012,China)

The pipeline is the key technology of manufacturing high-performance CPU. The OR1200,which has been widely studied currently,is a 4-stage pipeline CPU with a free open source. Without MEM stage which should be designed in OR1200,the pipeline will be stalled to wait for load or store instruction. In this research,we design a MEM stage for OR1200 in LSU. Hazard detection and data forwarding units have been included for efficient implementation of the pipeline. On the other hand,when a data requested by a load instruction has not yet become available,it leads to loaduse hazards. To resolve this hazard problem,we design a data valid signal Tag to control stalling of pipeline. The pipeline is stalled by the Tag signal for one stage and then continues with the forwarding of data,as the simulation result shows.

OR1200; pipeline; data hazard; data forwarding

常玉春,E-mail: changyc@jlu.edu.cn

曹凱寧,沈興浩,姬夢飛,常玉春.改進 OR1200 CPU 流水線的設計.計算機系統應用,2017,26(12):268–271. http://www.c-s-a.org.cn/1003-3254/5938.html

吉林省省級經濟結構戰略調整引導資金專項項目(2015Y041); 吉林省重點科技攻關項目(20160204042GX)

2016-12-06; 修改時間: 2016-12-19; 采用時間: 2017-01-16