基于MIPI標準下的D-PHY的設計與驗證

,,,

(1.上海大學 機電工程與自動化學院,上海 200072; 2.上海市電站 自動化技術重點實驗室,上海 200072;3.上海大學 微電子研究與開發中心,上海 200072)

基于MIPI標準下的D-PHY的設計與驗證

承文龍1,3,胡越黎1,2,3,楊曄晨3,胡云生3

(1.上海大學機電工程與自動化學院,上海200072; 2.上海市電站自動化技術重點實驗室,上海200072;3.上海大學微電子研究與開發中心,上海200072)

目前大部分移動設備均使用MIPI接口,主要是MIPI接口可以實現高速數據傳輸,同時不會造成功耗的損失過大的功能;為了理解MIPI接口的工作原理,通過對MIPI接口中物理層的設計和研究;闡述MIPI接口實現低功耗模式和高速傳輸數據模式的本質原理;對MIPI接口物理層的設計,采用40 nm的CMOS工藝,實現以500 MHz的速率來傳輸數據,功耗損失僅在0.74 mW左右。

移動產業處理器接口;物理層;高速模式;低功耗模式

0 引言

隨著信息技術的飛速發展,越來越多的智能便攜式設備走入人們的生活。人們對于移動設備設計要求越來越高,不僅要滿足高性能顯示效果的追求,同時也要極大的減少移動設備的功耗損失。因此,在2003年由ARM,Nokia,ST,TI等公司成立MIPI聯盟,把手機內部的多個接口標準化,減少設計的復雜程度和增加設計靈活性。MIPI不僅是一個聯盟也是一套接口協議規范的名稱,它下面有不同的工作組,以滿足移動終端各個子系統的不同需求,比如攝像頭接口CSI、顯示接口DSI、射頻接口Dig RF、麥克風/喇叭接口SLIM bus等[1-2]。而對應的物理層也是MIPI設計的最重要的模塊,其決定MIPI接口能否實現高速數據傳輸和低功耗命令傳輸的電氣特性。

目前,大部分MIPI接口的使用者,只知道MIPI接口包含高速傳輸和低功耗傳輸的功能,而沒有理解MIPI接口如何實現數據傳輸的原理和內部電路,同時國內也很少有相關的文獻詳細介紹MIPI接口中物理層的概念和原理。目前,主要應用的物理層有C-PHY,D-PHY和M-PHY,而D-PHY是應用最廣泛的物理層。所以,本文根據通過對D-PHY的設計和仿真驗證,詳細闡述物理層的工作原理和電路結構。

1 MIPI D-PHY基本原理介紹

1.1 MIPI D-PHY之間的通信

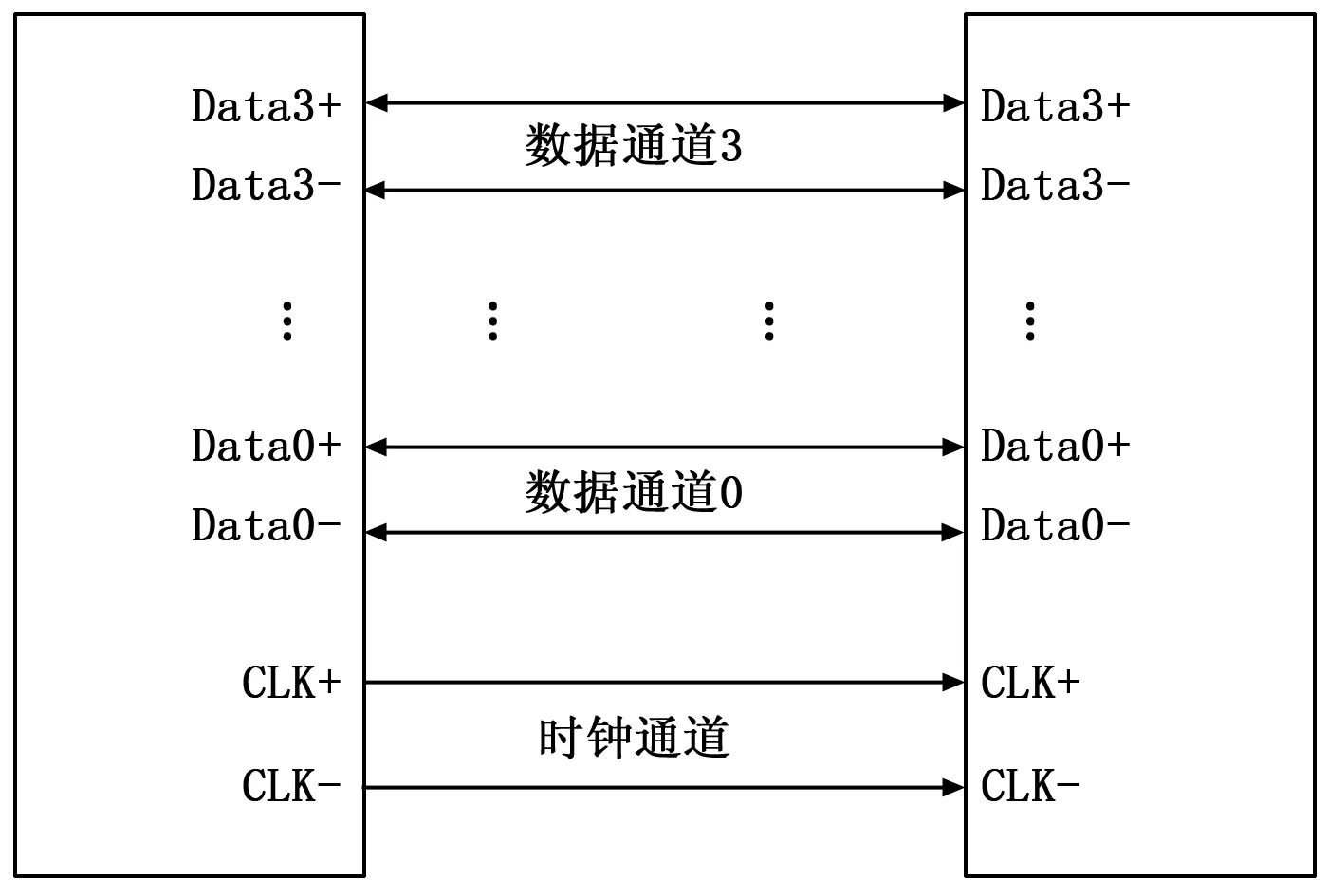

目前,MIPI主要有兩種類別,一種是基于DSI協議用于實現主處理器與顯示器件交互,多用于移動設備的顯示接口[3-4];一種是基于CSI協議用于實現主處理器與攝像器件交互,多用于移動設備的攝像接口[5]。MIPI-DSI和MIPI-CSI都可以共享同一個D-PHY,即它們的物理層是相同的。通常,D-PHY采用一對源同步的時鐘和一到四對差分時鐘數據線來進行數據傳輸,對應的時鐘通道是單向的,數據通道是單向或者雙向的,命令傳遞控制雙向通道的傳輸方向。如圖1是MIPI接口的物理連接圖,其主機和從機通過彼此的物理層相互連接,CLK為時鐘傳輸通道,以DDR的方式進行時鐘的控制,Data0~Data3為數據傳輸通道,當每條通道設置為高速傳輸模式時,傳輸速率可達80 Mbps到1 000 Mbps之間,但實際應用中存在各種外在限制,通常運行速率在500 Mbps左右,用于傳輸有效數據。當每條通道為低功耗傳輸模式時,最大傳輸速率僅為10 Mbps左右,用于傳輸控制命令。D-PHY工作時,最多可以有4個通道同時進行傳輸,可以實現4倍的速率進行數據和命令的傳輸。通過時鐘通道和數據通道,可以實現主機和從機之間的數據和命令的交互,傳遞有效信息。同時,主機和從機都可以作為數據發送端或接受端,但時鐘信號只能由主機提供給從機。

1.2 MIPI D-PHY的電氣特性

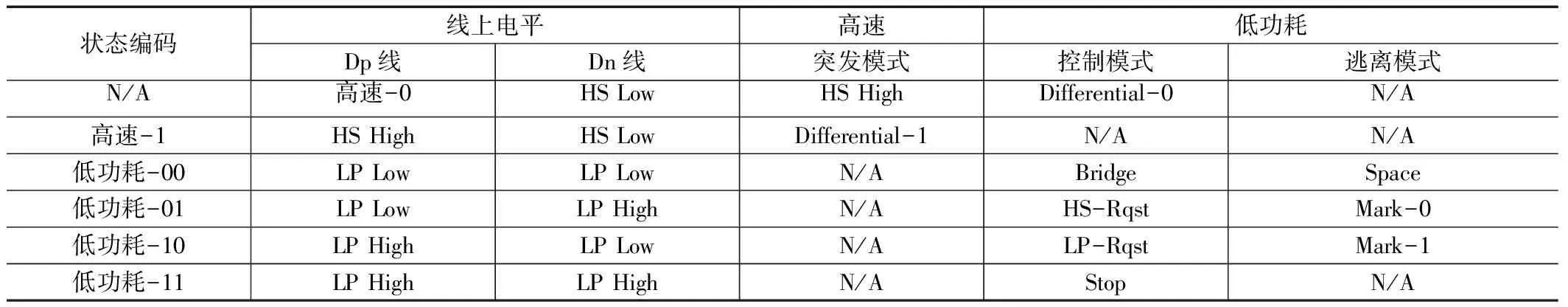

由圖1可知,物理層與物理層之間的數據傳輸是利用數據通道進行,而數據通道中數據傳輸僅由兩根數據線控制。一般定義Dp和Dn構成數據通道的兩根數據線,Dp和Dn數據線上可以傳輸不同的電氣特性。由于MIPI接口包含兩種傳輸模式,對于不同的傳輸模式,傳輸的高低電平的定義也不同。見表1所示,在低功耗傳輸模式下,根據數據通道的Dp和Dn數據線中輸出電平組合不同,可以分為4種輸出格式LP-00,LP-01,LP-10,LP-11,而4種不同的輸出格式也表示不同的指令模式或工作狀態,控制D-PHY運行的工作狀態。對比低功耗模式,高速模式利用Dp和Dn數據線中輸出電平進行差分處理,產生只有兩種輸出格式HS-0和HS-1。當Dp數據線為邏輯高電平,Dn數據線為邏輯低電平時,代表輸出格式為高速傳輸的邏輯高電平;當Dp數據線為邏輯低電平,Dn數據線為邏輯高電平時,代表輸出格式為高速傳輸的邏輯低電平。因此,高速模式下的邏輯“1”和邏輯“0”就可以代表數據傳輸的邏輯電平,避免出現邏輯混亂的問題。一般情況下,低功耗模式的工作電壓大約在0 V到1.2 V之間波動;而高速模式的工作電壓大約在100~300 mV之間波動。

表1 D-PHY通道狀態表

圖1 DSI/CSI物理連接圖

1.3 MIPI D-PHY通道的工作原理

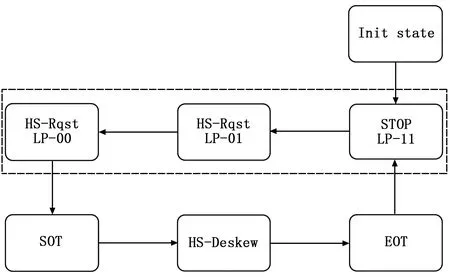

目前,D-PHY支持兩種傳輸模式,高速傳輸模式和低功耗傳輸模式,兩種模式共同工作,實現MIPI接口的協議層中的數據和命令的傳輸。當D-PHY工作在高速傳輸模式時,主要實現有效像素數據的傳輸;當D-PHY工作在低功耗傳輸模式時,主要實現控制信號或命令的傳輸。通過高速傳輸和低功耗傳輸之間的合理切換,可以實現高速傳輸數據的同時減少功耗的損失。通常,D-PHY數據通道包含3種操作模式,分別是逃離模式,高速模式以及控制模式,而從控制模式的停止狀態開始可能發生的事件有多種。如圖2所示,D-PHY中一個最基本的高速模式狀態圖,工作的狀態主要由Init state,STOP,HS-Rqst,HS-Prpr,SOT,HS-Deskew,EOT七個狀態構成。首先,Init state表示D-PHY模塊通道的最初始狀態;狀態STOP,HS-Rqst,HS-Prpr是D-PHY模塊工作在低功耗模式下的狀態,主要負責傳輸不同的命令,進行控制狀態的轉換;狀態SOT和EOT是D-PHY工作在低功耗模式下的狀態,主要負責給有效數據包添加包頭和包尾序列。狀態HS-Deskew是D-PHY工作在高速傳輸模式下的狀態,主要負責傳輸有效的數據包。當SOT接收到00011101指令后,數據通道進入高速有效數據傳輸階段HS-Deskew,HS-Deskew階段的有效數據傳輸結束后,EOT接收到00指令后,數據通道進入STOP狀態等待,指示一次基本完整的數據傳輸結束。

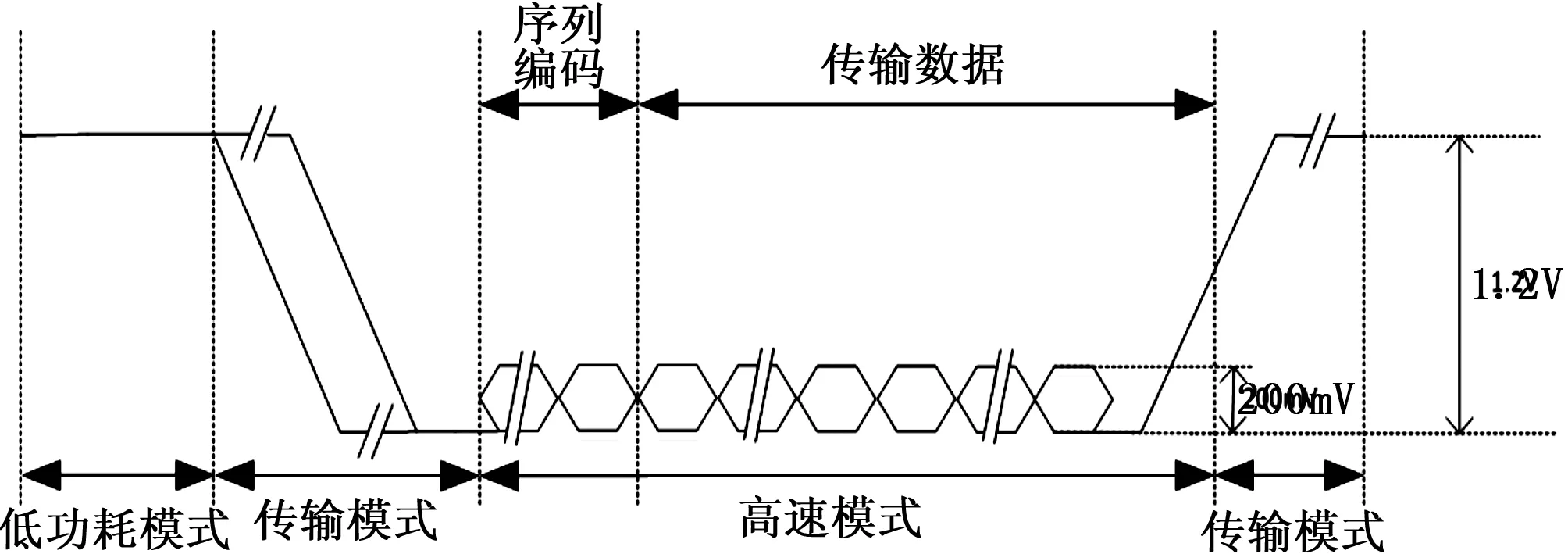

根據圖2的D-PHY工作狀態的表述,D-PHY中一個完整的數據傳輸需要高速傳輸模式和低功耗傳輸模式相互配合構成。在傳輸開始階段D-PHY處于初始狀態,即工作在低功耗模式下,當連續接收到低功耗模式下的傳輸命令LP-11-gt;LP-01-gt;LP-00序列指示后,數據傳輸模式進入高速數據傳輸模式。在高速傳輸模式中,需要給有效的傳輸數據進行打包處理,在有效數據的開始位置和結束位置添加規定序列SOT和EOT,隔離有效數據和命令序列,減少彼此之間的干擾,避免影響最終傳輸數據的正確性。在數據傳輸結束時,接收到低功耗傳輸命令LP-gt;11序列指示后,數據傳輸離開高速數據傳輸模式進入默認狀態的低功耗模式。如圖3 是D-PHY傳輸原理圖,顯示了D-PHY模塊實現一次完整的數據傳輸的波形圖。

圖2 D-PHY高速模式狀態圖

圖3 D-PHY傳輸原理圖

2 MIPI D-PHY模塊設計

2.1 D-PHY通道模塊設計

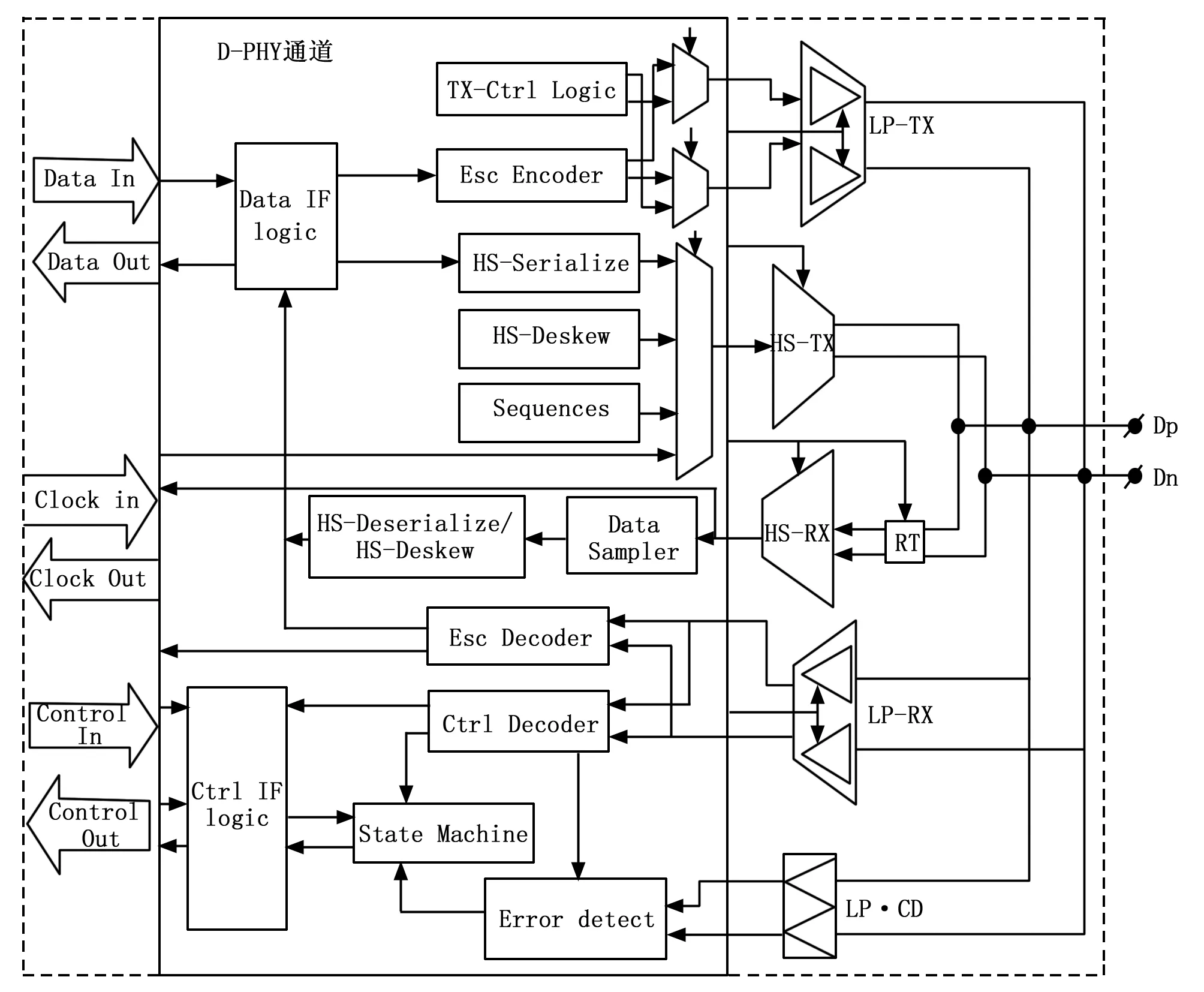

MIPI D-PHY主要由各個通道模塊組成,如時鐘通道或數據通道,每個通道的傳輸是遵循串行傳輸原理,而通道間傳輸是遵循并行傳輸原理,不同通道之間彼此獨立運行,不會出現相互干擾和影響。如圖4所示,一個完整的通道模塊主要由兩大模塊組成,數字模塊和模擬模塊。對于模擬模塊,主要是接收和發送數據到數字模塊,利用低壓差分電路HS-TX和HS-RX,實現數據的高速發送和接收,利用低功耗傳輸電路LP-TX和LP-RX,實現控制命令的發送和接收以及控制通道的工作狀態和數據傳輸方向,利用低功耗沖突檢測器電路LP-CD,避免低功耗傳輸模式下,由于傳輸通道雙向性可能會引起的傳輸沖突現象[6]。數據線Dp和Dn是物理層通道的輸出端口,用于物理層與物理層的數據傳輸,也是主機和從機信息交互的唯一端口,即可傳輸高速數據也可傳輸低功耗命令,但不能兩種模式同時傳輸,只能交替傳輸。因此,物理層中的模擬模塊是實現物理層和物理層之間數據傳輸的重要環節。而物理層數字模塊由多個子模塊組成,一部分數字模塊中的子模塊可以接收來自協議層的數據包,并對接收的數據包進行再處理,對傳輸低功耗命令數據包進行編碼,對傳輸高速有效數據包進行并行轉串行操作,轉換成能被物理層中模擬電路可以接收處理的格式。一部分數字模塊的子模塊可以處理來自物理層模擬模塊傳輸的數據,對接收的低功耗命令數據進行解碼,對傳輸高速有效數據進行串行轉并行操作,轉換成可以被上層協議層接收處理的格式。另一部分數字模塊的子模塊是對低功耗模式下的命令傳輸過程出現的錯誤進行檢測,避免傳輸通道雙向性引起的傳輸沖突問題[7]。因此,D-PHY中的數字模塊主要功能就是對傳輸的數據格式進行處理,解決數據在不同層傳輸過程中,出現數據格式不匹配問題。

2.2 D-PHY中模擬模塊的設計

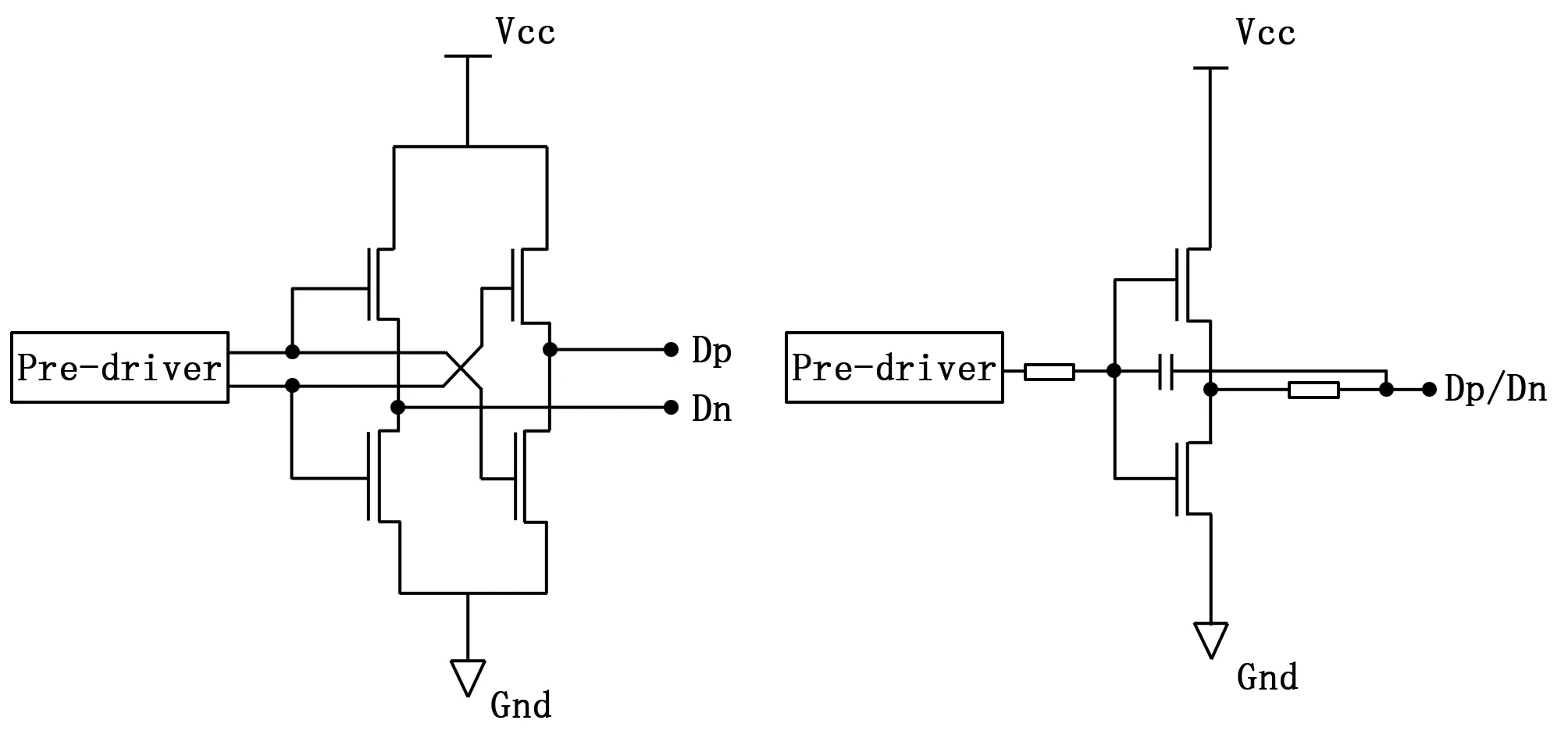

由圖4可知,MIPI D-PHY通道模塊中的模擬模塊分為高速傳輸模式的電路和低功耗傳輸模式的電路。如圖5所示,根據兩種不同的工作模式,物理層中模擬模塊的電路分為兩種模式的電路設計,對應的規定正常傳輸時的有效電平也分為兩類,一類是差分的小擺幅電平,用于高速數據傳輸,另一類是低速的滿擺幅電平,用于低功耗數據傳輸。MIPI的高速數據傳輸原理與LVDS原理很像,屬于低壓差分電路,輸出結果是由數據線Dp和Dn共同控制,所以電路具有高速、差分、低擺幅特點,這些特點有利于抗EMI干擾和降低功耗,適用于大數據量圖像的突發連續傳輸[8]。在高速差分數據傳輸時的共模電平在200 mV左右,電壓擺幅為100~300 mV之間,數據傳輸速率為80~1 000 Mbps之間。對應的低功耗傳輸也可視為低速傳輸,屬于單端輸出電路,可以進行讀寫寄存器等短時間、小數據量操作,使電路在較低的功耗水平運行,一般工作電壓從0~1.2 V,最大數據傳輸速率為10 Mbps。在低功耗傳輸時,電壓擺幅在1.2 V左右,傳輸速率為10 MHz,而在高速傳輸時,電壓擺幅為200 mV,傳輸速率可達500 MHz。因此,對于有效的像素數據利用高速傳輸,對于控制命令利用低功耗傳輸,這樣可實現高速傳輸數據的同時,減小不必要的功耗損失[9]。

圖4 MIPI D-PHY通道模塊原理圖

3 實驗結果分析

3.1 驗證平臺搭建

本文以Verilog HDL硬件語言為基礎,設計D-PHY模塊做為驗證模塊,搭建合理的測試平臺,利用Mentor公司的Modelsim進行軟件仿真,對設計模塊做功能和動態時序的驗證,根據需求添加需要的端口進行波形觀察。當軟件仿真滿足要求后,在利用Lattice公司的CrossLink FPGA進行板級的驗證,并通過特定的示波器進行波形觀察[10-12]。

3.2 軟件驗證結果分析

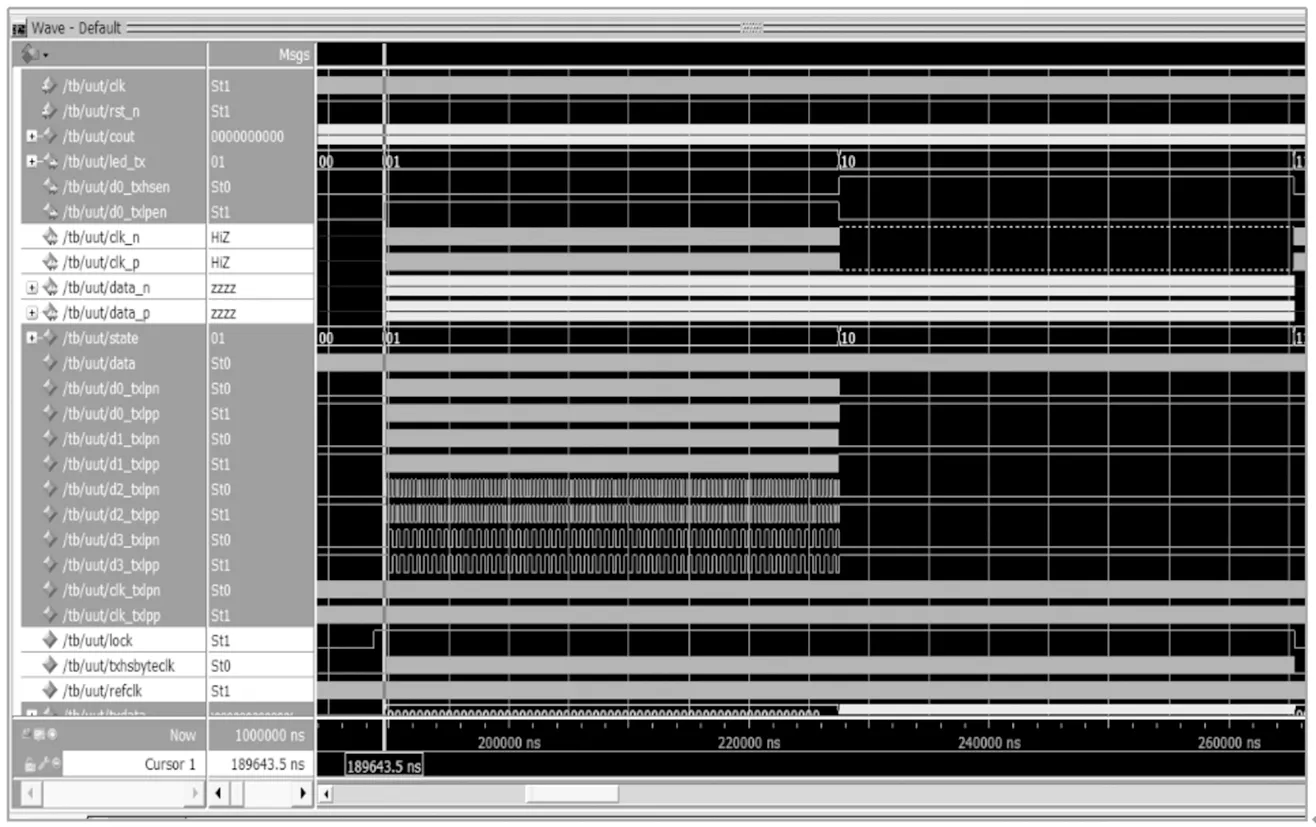

使用Modelsim對D-PHY設計模塊進行功能仿真。如圖5所示,設置state表示D-PHY工作狀態,當state=01表示低功耗數據傳輸波形,state=10表示高速數據傳輸波形,state=00和state=11表示其他空閑狀態,可以不予考慮。clk_n和clk_p是時鐘通道的數據線,用于物理層時鐘的傳輸,data_n和data_p是數據通道的數據線,用于物理層數據的傳輸。可以發現在state=10時,高速數據傳輸的時鐘頻率無法達到要求,所以有效數據無法正常傳輸。

由圖5可知,使用Modelsim軟件仿真所得結果與預期結果一樣,唯一不足是高速傳輸無法顯示波形。由于高速傳輸的電壓擺幅是200 mV左右,在Modelsim軟件仿真中很難顯示高速模式下的數據傳輸波形。

圖5 高速傳輸塊和低功耗傳輸電路

3.3 硬件驗證結果分析

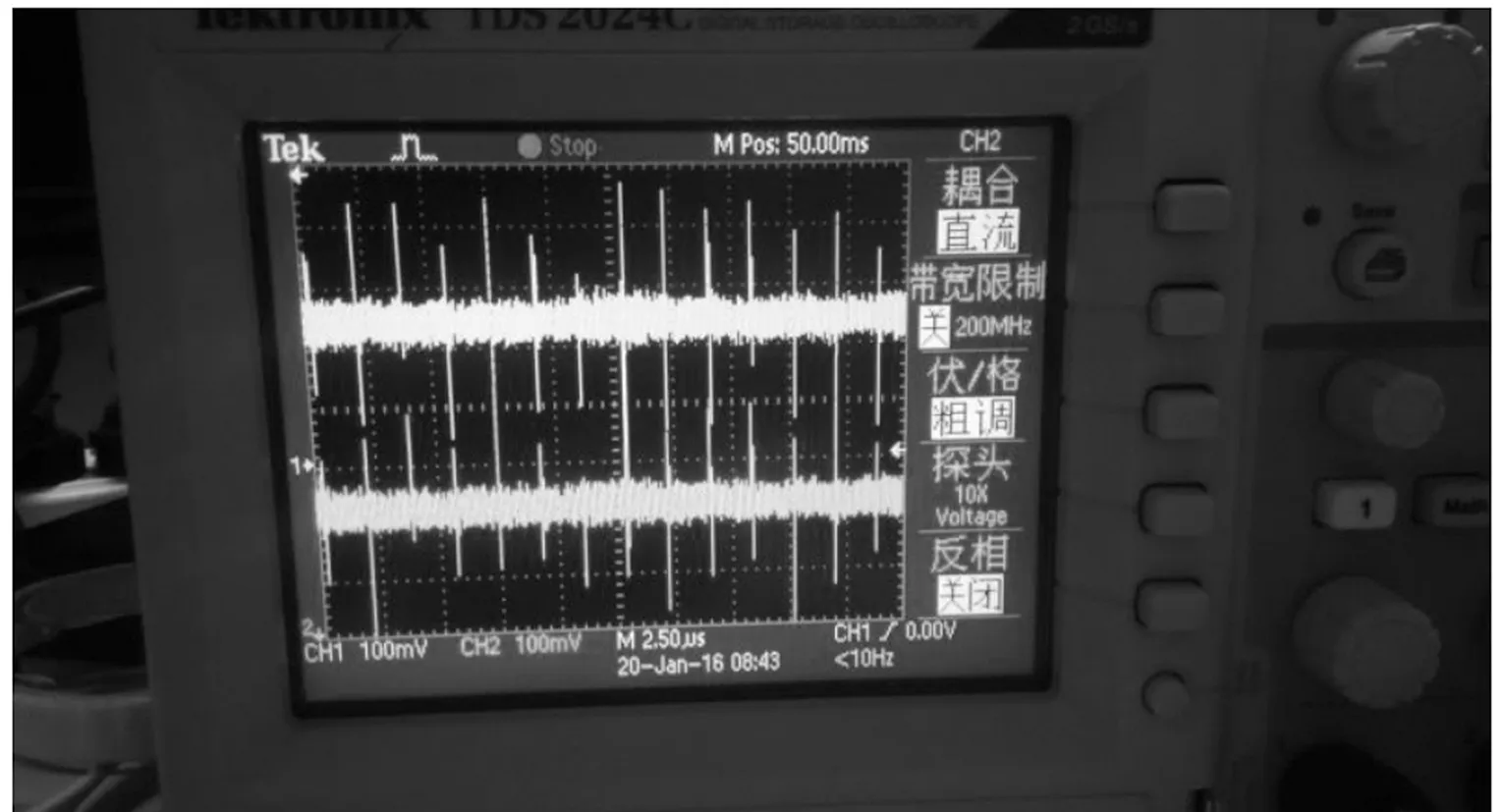

所以,對于高速模式的傳輸測試,需要利用特定的示波器才能仿真出相應的結果。根據不足,本文利用特定的示波器對MIPI D-PHY設計進行高速數據采集的觀察。當D-PHY模塊設計在Modelsim中滿足功能驗證后,利用FPGA的靈活性,將設計好的模塊,配合Lattice的Diamond軟件,將設計模塊燒寫到CrossLink FPGA中。在進行板級調試時,通過引線引出對應的Dp和Dn端口,連接到特定的示波器上,通過調節示波器的電壓擺幅,工作頻率和工作通道,直到出現預期波形。如圖6、7所示,示波器的波形分別由CH1通道和CH2通道輸出,CH1通道的黃色波形為Dp端口的輸出波形,CH2通道的藍色波形為Dn端口的輸出波形,通過示波器可以看出CH1和CH2通道的單位電壓是100 mV,所以高速輸出波形的電壓擺幅符合預期要求。對于高速模式的傳輸就是利用Dp和Dn端口的電壓進行差分傳輸,當Dp端電壓大于Dn端電壓時,輸出為邏輯高電平;當Dn端電壓大于Dp端電壓時,輸出為邏輯低電平。

圖6 D-PHY軟件仿真圖

圖7 D-PHY示波器仿真圖

4 結論

本文MIPI D-PHY的設計支持高速模式和低功耗模式,符合MIPI芯片的標準,設計采用40 nm的CMOS工藝制造,在高速傳輸下,速度達到400 MHz~500 MHz之間,所消耗功耗在0.52 mW~0.74 mW之間。通過本文闡述,體現出MIPI在移動設備的獨特性和重要性,不僅滿足高性能的傳輸效果,同時可以極大的減少移動設備的功耗。

[1] MIPI Alliance Specification for D-PHY version 1.00.00[S]. MIPI Alliance, 2009.

[2] Lawrence R, Richard. High-speed serial interface for mobile displays[Z]. IDW, 2006:2013-2016,

[3] MIPI Alliance Specification for Display Serial Interface version 1.01.00[S]. MIPI Alliance, 2008.

[4] Kyusam Lim, Gye Su Kim, Suki Kim, Senior Member. A Multi-Lane MIPI CSI Receiver for Mobile Camera Applications[Z]. IEEE Consumer Electronics Society, 2010:1185-1190 .

[5] Yueh-Chuan Lu, Zong-Yi Chen, Pao-Chi Chang. Low power multi-lane MIPI CSI-2 receiver design and hardware implementations[A]. International Symposium on Consumer Electronics (ISCE)[C]. 2013:199-200.

[6] MIPI Alliance Standard for Display Serial Interface V1.0[S]. MIPI Alliance, 2006.

[7] Beom-Dam Kim, Sang-Jin Lee. Design of a D-PHY Chip for Mobile Display Interface Supporting MIPI Standard[A]. IEEE International Conference on Consumer Electronics (ICCE)[C]. 2012:660-661.

[8] 董春雷,王康平,陳 威. LVDS技術在LCD數據傳輸中的應用[J].電子技術, 2011,(2):48-49.

[9] W Wei, FT Zhang. The Analysis of the Transmission Signal Measured MIPI D-PHY[J]. Advanced Materials Research, 2014,(7):986-987.

[10] 胡越黎, 周 諶. 基于IP復用的片上級系統的構建與驗證[J]. 計算機測量與控制, 2010,25(3):629-631.

[11] 曹 陽,胡越黎. 基于UVM的存儲控制器功能驗證[J]. 計算機測量與控制, 2015,25(3):834-837.

[12] 虞 超,胡越黎,王龍杰,等. 基于MV10微處理器的在線編程IP核設計與驗證[J]. 電子技術應用, 2012,8(6):126-128.

DesignandVerificationofD-PHYBasedonMIPIStandard

Cheng Wenlong1,3,Hu Yueli1,2,3,Yan Yechen3,Hu Yunsheng3

(1. College of Mechatronic Engineering and Automation, Shanghai University, Shanghai 200072, China; 2. Shanghai Key Laboratory of Power Station Automation Technology, Shanghai 200072, China; 3. Microelectronics Research and Development Center, Shanghai University, Shanghai 200072, China)

Most mobile devices use MIPI interface at present, MIPI interface can realize high speed data transmission, and will not cause high power consumption. In order to understand the working principle of the MIPI interface, through the design and research of physical layer in MIPI interface. MIPI supports low-power mode and high-speed data transmission mode. The design of MIPI interface physical layer using 40nm CMOS process, and can realize transmitting data at a rate of about 500 MHz. The power consumption of transmitting data is only about 0.74 mW.

mobile industry processor interface; physical layer; high speed mode; low power mode

2017-02-27;

2017-03-31。

承文龍(1993-),男,安徽安慶人,碩士研究生,主要從事芯片設計和驗證方向的研究。

胡越黎(1959-),男,上海人,工學博士,教授,博士生導師,主要從事圖像處理、機器視覺、片上系統、芯片設計方向的研究。

1671-4598(2017)09-0295-03

10.16526/j.cnki.11-4762/tp.2017.09.075

TP273

A