數據采集系統ADC接口設計與實現

白晨,邊慶

(中航工業西安航空計算技術研究所,陜西西安,710068)

數據采集系統ADC接口設計與實現

白晨,邊慶

(中航工業西安航空計算技術研究所,陜西西安,710068)

本文提出了基于AD7981的數據采集系統ADC接口設計方案。從硬件設計和軟件開發兩個方面闡述了ADC接口的具體設計和實現方法。ADC接口電路采用模數隔離設計,防止噪聲串擾。模數轉換芯片性能優越,留有較大的性能余量,擴展了系統的使用范圍,前端信號調理電路引起的噪聲和誤差控制得當,使得ADC接口電路具備較高的準確性和可靠性。

數據采集系統;ADC;采樣率;FPGA

0 引言

數據采集系統將自然界中的各種模擬量進行數字量化轉換,給人們認識、理解和分析自然提供了更為直觀的手段。數據采集系統中模數轉換(ADC)接口的性能是保證采集系統結果的準確性和可靠性的重要指標。

1 系統需求分析

硬件設備的設計工作應該從系統的功能需求和性能需求分析開始。數據采集系統需具有較高的數據準確性和可靠性,ADC接口數據準確性和可靠性主要決定因素是ADC前端信號調理電路、ADC的采樣精度和ADC的采樣率。

1.1 ADC接口需求分析

1.1.1 ADC采樣精度

ADC的采樣精度比特數主要取決于系統所需的測量的動態范圍,以及系統整機噪聲水平和量化誤差等因素。作為一個工程應用,系統的動態范圍為超出需求,留有余量即可。

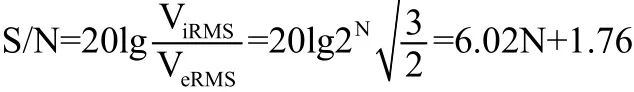

模數轉換器的信號噪聲比(S/N)是在模數轉換器輸出端測得的,信號用基波的均方根幅度表示,噪聲是所有非基波信號的均方根之和。信噪比和量化數(ADC的位數)之間的關系是:

其中,ViRMS為輸入信號基波的峰-峰值均方根,VeRMS為一個周期內誤差信號的均方根。

若選用18bit的ADC,就有6.02*15+1.76=110.12dB的動態范圍。本系統整機的噪聲水平(指ADC前端的噪聲水平)在60dB放大量約為40mV,ADC芯片的滿量程為5V,因此噪聲約占ADC芯片18bit中的,剩下14個bit就有84dB的動態范圍,另外系統檢測閥為22dB,這樣就還有62dB的動態范圍,加上60dB的前級放大,模擬信號采樣前端的動態范圍是122dB。本數據采集系統應用于聲納中聲波信號采集,如果信號衰減只考慮傳播損失,衰減可通過傳播損失方程計算出來:

其中,r為傳播距離,α為聲波在水中傳播吸收衰減系數,取經驗值1dB/km。系統要求最遠作用距離為r=4800m,此時的傳播損失為76dB(<122 dB),所以18bit采樣精度ADC芯片完全滿足系統要求。

1.1.2 ADC的采樣率

至于ADC芯片的采樣率問題,主要是根據接收換能器接收信號頻率以及定位算法的精度的要求。系統采樣信號最高頻點是125KHz,根據奈奎斯特采樣定律,采樣率最小為250KHz,考慮到留有一定的余量,將采樣率設定為500KHz。

2 方案設計與實現

2.1 ADC硬件設計與實現

2.1.1 ADC工作方式和電路結構

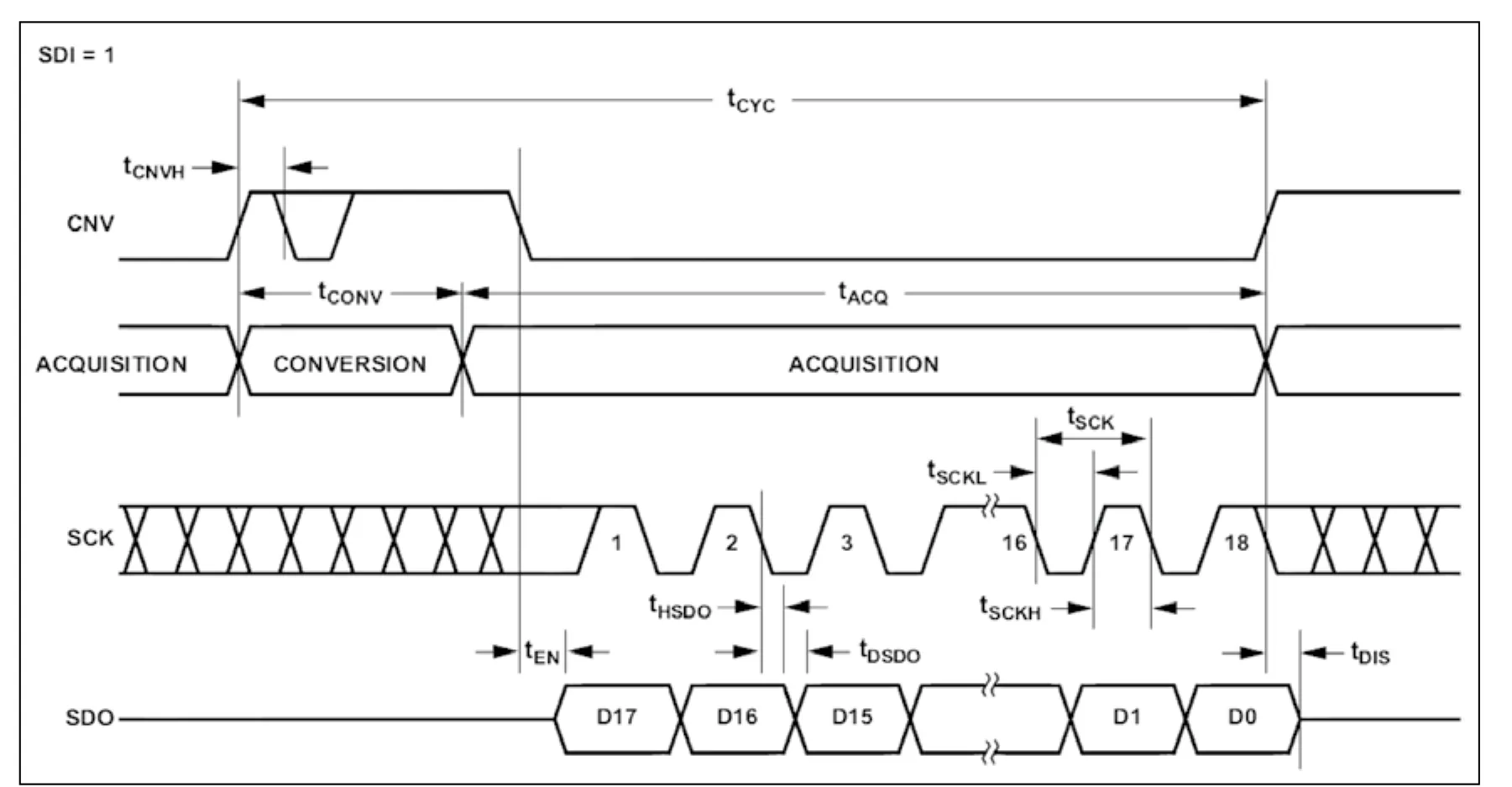

本系統中使用滿足需求的AD7982作為模數轉換芯片,工作方式采用模式的三線式接口。僅使用CNV、SCK和SDO信號,可將線路連接減至最少,在隔離應用中非常有用。此模式時序如圖1所示。

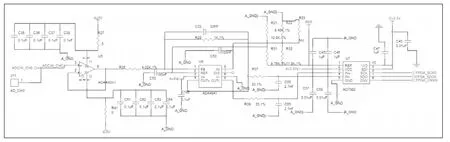

根據工作方式、實際需求和ADC芯片類型設計模數轉換電路結構如圖2所示,其中包括提高輸入阻抗的輸入模擬信號跟隨器,實現輸入信號單端轉差分的轉換器。

圖1 三線模式串行接口時序圖(SDI高電平)

圖2 AD7982模數轉換電路結構

2.1.2 ADC轉換數值與模擬輸入電壓的函數關系

ADC芯片AD7982的差分輸入端IN+和IN-之間的差值電壓為,參考電壓是RDF×2。AD7982是18bit的模數轉換器,實際中只選用高16bit數據。則AD7982數字數據輸出的滿量程為216,AD7982的模擬測量范圍為[-2REF,2REF](因為模擬輸入被驅動器ADA7941衰減成原來的,所以在正電壓的數字輸出滿量程就是32767,負電壓的數字輸出滿量程就是-32768。所以ADC的轉換函數就是:

2.2 FPGA控制ADC接口和管理ADC數據程序設計

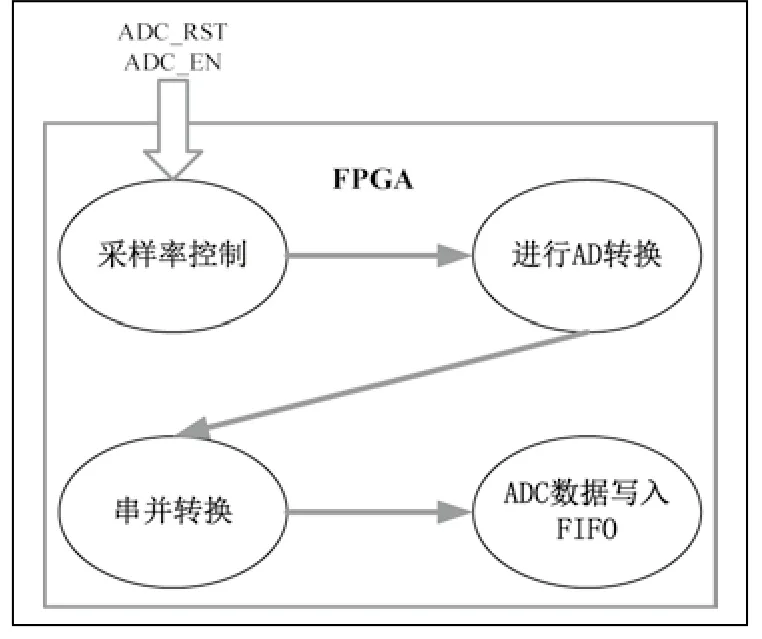

FPGA通過使用One-hot狀態機控制ADC和讀取ADC數據,之后數據緩存在FPGA內部FIFO中。FPGA控制ADC接口和管理ADC數據的程序的狀態如圖3所示。當外部控制信號ADC_RST和ADC_EN都有效時,ADC啟動;根據系統中采樣率的要求,進行轉換率控制,啟動ADC轉換;一次ADC轉換結束之后,將轉換后的數據讀出,同時進行串并轉換;串并轉換完成之后,將數據送入FIFO,FPGA準備啟動下一次模數轉換。

圖3 FPGA控制ADC和管理數據程序狀態圖

AD7982使用芯片內置時鐘,數據輸出使用外部時鐘SCK信號。數據在SCK下降沿輸出,提高數據的輸出速率。使用FPGA給AD7982提供數據輸出時鐘SCK。

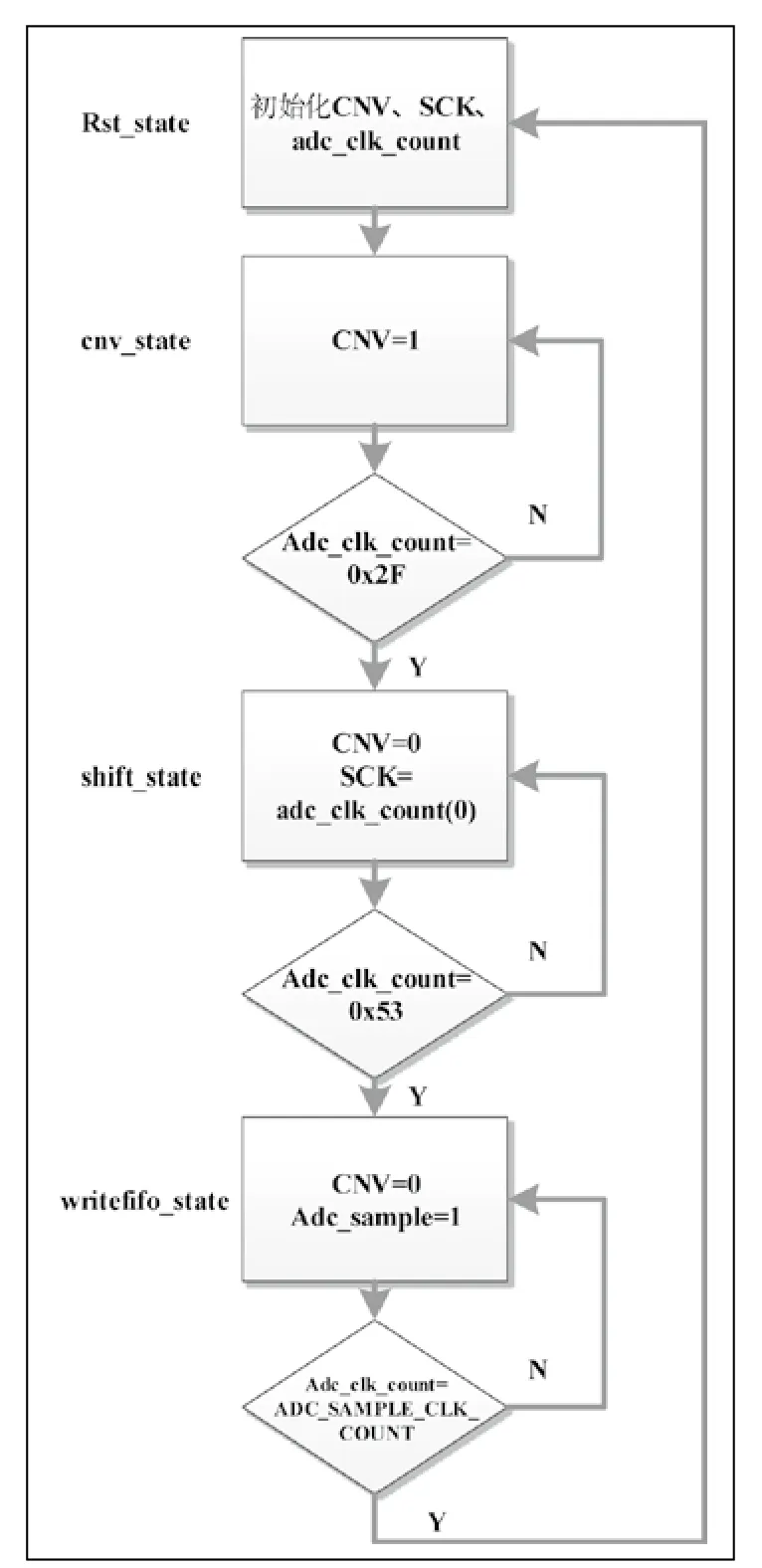

圖4 FPGA控制ADC轉換程序狀態圖

FPGA使用狀態機One-Hot模式控制AD7982。首先進入ADC復位狀態,初始化CNV、SCK和清零時鐘計數clk_count;接下來進入ADC轉換狀態,拉高CNV信號,在這個狀態中等待AD7982完成數據轉換,等待0x2F個clk,即940ns,滿足AD7982轉換時間最大710ns的要求;等待轉換完成進入ADC數據輸出狀態,拉低CNV信號,使用ADC時鐘計數信號clk_count的0位作為SCK信號,則SCK的頻率為clk/2=25MHz,使用SCK下降沿作為FPGA讀取AD7983串行數據的觸發電平,循環執行讀取AD7982數據操作18次,即18個SCK時鐘,完成此次18bits的數據讀取;讀完ADC數據之后進入寫FIFO狀態,置ADC數據讀取完成標志信號sample,等待時鐘計數clk_count等于SAMPLE_CLK_COUNT后進入ADC復位狀態。至此,一次ADC控制和數據讀取操作完成。狀態轉換圖如圖4所示。

根據上述接口時序控制,完成一次ADC數據轉換和數據讀取需要的時間是SAMPLE_CLK_COUNT個adc_clk,可計算出本系統ADC的采樣率是:

這樣就通過SAMPLE_CLK_COUNT的值間接控制了ADC的采樣率。

3 結論

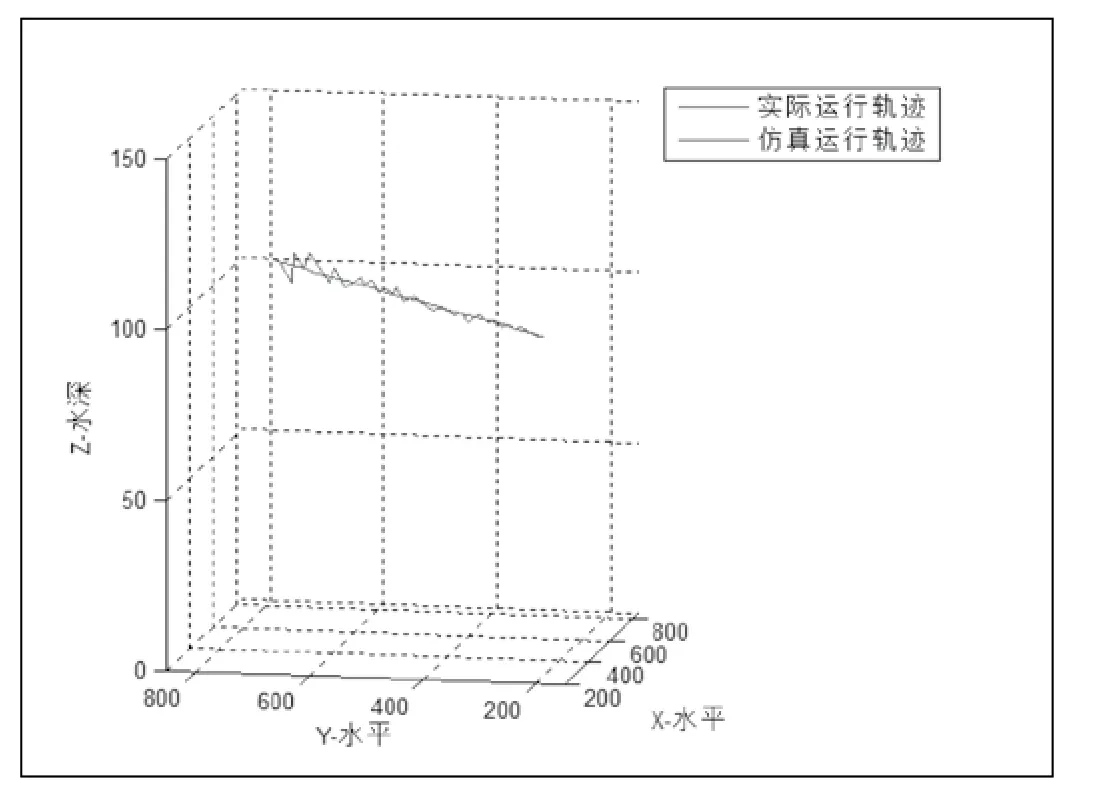

圖5 實航和仿真軌跡圖

本系統應用在某型聲納,用于對目標的三維軌跡進行測量。圖5所示為根據采集數據計算運動軌跡與目標實際航行軌跡的對比,圖中直線為目標實際航行軌跡,非直線為根據采集數據計算的運動軌跡,0.5%的定位誤差滿足設計指標。

[1]席德勛.現代電子技術[M].北京:高等教育出版社,1999.

[2]烏立克(美)洪審 譯.水聲學原理[M].哈爾濱:哈爾濱船舶工程學院出版社,1990.

ADC interface design and implementation in data acquisition system

Bai Chen,Bian Qing

( Xi’an Aeronautic Computing Technique Research Institute, AVIC, Xi’an Shaanxi, 710068)

This paper puts forward the design of system of ADC interface based on AD7981. It describes the ADC interface of the design and implementation from the hardware design and software development aspects.ADC interface circuit using modular isolation design, to prevent noise crosstalk. The ADC chip is superior in performance, extending the range of use of the system, and the noise and error control caused by the front-end signal conditioning circuit, making the ADC interface circuit with high accuracy and reliability.

Data collection; ADC;Sampling rate;SRAM