基于FPGA的DDFS函數(shù)信號(hào)發(fā)生器設(shè)計(jì)

黃 麗

(武漢鐵路職業(yè)技術(shù)學(xué)院,湖北 武漢 430205)

基于FPGA的DDFS函數(shù)信號(hào)發(fā)生器設(shè)計(jì)

黃 麗

(武漢鐵路職業(yè)技術(shù)學(xué)院,湖北 武漢 430205)

FPGA的可編程屬性使得其在通信系統(tǒng)設(shè)計(jì)中使用越來(lái)越頻繁,文章采用DDFS算法技術(shù),以模擬電路為基礎(chǔ)架構(gòu),完成了一個(gè)多種波形輸出、高精度的數(shù)字信號(hào)發(fā)生器設(shè)計(jì)。且設(shè)計(jì)了以單片機(jī)加LCD、按鍵為輸入控制及實(shí)時(shí)顯示的最小系統(tǒng),可以手動(dòng)輸入選擇輸出如方波、正弦波及三角波等任意頻率可變的信號(hào)。

FPGA;單片機(jī);DDFS;函數(shù)信號(hào)發(fā)生器

有線或者無(wú)線通信系統(tǒng)的研究或應(yīng)用領(lǐng)域,高精度、多類型的信號(hào)源必不可少[1]。故信號(hào)發(fā)生器是用來(lái)產(chǎn)生正弦波、鋸齒波、方波、三角波等各種信號(hào)的一種通用儀器,在科學(xué)研究和工程設(shè)計(jì)中廣泛應(yīng)用[2]。成熟的信號(hào)發(fā)生器一般采用集成電路器件設(shè)計(jì)實(shí)現(xiàn),其輸出信號(hào)只能是某種特定的周期性信號(hào)。如果采用現(xiàn)場(chǎng)可編程邏輯門陣列(Field Programmable Gate Array,F(xiàn)PGA)進(jìn)行波形存儲(chǔ)器設(shè)計(jì)之后,將能合成任意波形的信號(hào)[3]。用直接數(shù)字式頻率合成器(Direct Digital Synthesizer,DDS)產(chǎn)生正弦信號(hào)的方法具有輸出頻率信號(hào)穩(wěn)定、相位連續(xù)等特點(diǎn),且很容易通過(guò)數(shù)字的方法實(shí)現(xiàn)調(diào)整。本文采用89C52單片機(jī)為控制核心,結(jié)合FPGA任意可編程功能,采用經(jīng)典的直接頻率數(shù)字頻率合成(Direct Digital Frequency Synthesis,DDFS)技術(shù),輔助以部分放大模擬電路,設(shè)計(jì)出了一個(gè)高精度、可手動(dòng)選擇、波形穩(wěn)定的數(shù)字信號(hào)發(fā)生器,輸出波形可以在正弦波、方波及三角波間切換。

1 系統(tǒng)總體設(shè)計(jì)方案及實(shí)現(xiàn)框

1.1 總體設(shè)計(jì)框

系統(tǒng)總體設(shè)計(jì)框如圖1所示,本系統(tǒng)由單片機(jī)89C52完成系統(tǒng)控制和數(shù)據(jù)運(yùn)算,波形表存儲(chǔ)在FPGA中,由FPGA實(shí)現(xiàn)DDS的地址累加器,在外圍采用D/A及濾波電路完成波形的合成,幅度控制采用雙D/A。第一級(jí)的輸出作為第二級(jí)D/A轉(zhuǎn)換的參考電壓,濾波模塊電路用于濾除由第二級(jí)DAC產(chǎn)生的高頻分量,以及數(shù)字采集樣時(shí)產(chǎn)生的高次諧波分量,從而得到平滑干凈的信號(hào)。

圖1 總體設(shè)計(jì)框

1.2 關(guān)鍵模塊設(shè)計(jì)

本系統(tǒng)的關(guān)鍵模塊主要是基于FPGA DDFS算法設(shè)計(jì)。

1.2.1 FPGA的設(shè)計(jì)

FPGA設(shè)計(jì)的DDFS實(shí)際就是個(gè)相位累加器,設(shè)計(jì)不同的累加步進(jìn),即可得到不同的頻率分辨率,步進(jìn)越小,輸出的波形越平滑。FPGA將累加輸出值送到內(nèi)部存儲(chǔ)好的波形數(shù)字幅度RAM的地址上,讀出數(shù)據(jù)后送到DAC完成數(shù)模轉(zhuǎn)換,最終輸出數(shù)字波形到輔助模擬電路,單片機(jī)完成相關(guān)頻率和步進(jìn)的配置。頻率合成器的核心模塊如圖2所示。

圖2 FPGA中核心DDS模塊

1.2.2 基于單板機(jī)的人機(jī)交互模塊設(shè)計(jì)

人機(jī)交互是由單片機(jī)、LCD和按鍵來(lái)實(shí)現(xiàn)的,單板板選用INTEL公司的89C52,其用于控制LCD顯示和按鍵輸入控制等;同時(shí)還要控制FPGA的輸入,配置其頻率合成所需要的步進(jìn)值、信號(hào)波形類型等。單片機(jī)與FPGA的有基于Intel總線模式的讀寫接口,對(duì)FPGA內(nèi)部實(shí)現(xiàn)配置和選擇,從而讓FPGA內(nèi)部的雙口RAM內(nèi)存儲(chǔ)數(shù)據(jù)的讀出送到DAC上。兩片DAC的控制接口也由單板模擬產(chǎn)生。

本信號(hào)發(fā)生器人機(jī)交互的總體設(shè)計(jì)思想是:?jiǎn)纹瑱C(jī)循環(huán)等待按鍵輸入,默認(rèn)輸出標(biāo)準(zhǔn)的1 kHz方波,用戶可以通過(guò)按下按鍵后選擇實(shí)現(xiàn)各種功能,如實(shí)現(xiàn)方波、正弦波和三角波之間的切換。同時(shí)還可完成頻率控制和幅度控制,這都可以通過(guò)輸入相應(yīng)的數(shù)字完成所需要輸出波形的頻率或幅度輸入。LCD的顯示也由單板在控制掃描輸入,最大支持輸入6位數(shù)字輸入,系統(tǒng)自動(dòng)默認(rèn)為001000。設(shè)置有取消/刪除鍵取消本次輸入或修改之前輸入的參數(shù)。

1.3 輔助模擬電路設(shè)計(jì)

模擬電路主要是完成最終的模擬信號(hào)輸出,選擇了2片DAC和濾波放大模塊共同實(shí)現(xiàn)。DAC器件使用的是DA公司的DA0832,由于DA0832為電流輸出型的轉(zhuǎn)換器,因此要獲得模擬電壓輸出時(shí),需接外加轉(zhuǎn)換電路,本設(shè)計(jì)中采用運(yùn)放電路作為轉(zhuǎn)換電路。

后邊的濾波模塊采用二階巴特沃茲濾低通濾波器進(jìn)行濾波,濾除波形中由D/A產(chǎn)生的高頻分量,使輸出波形平滑不失真。

2 系統(tǒng)測(cè)試結(jié)果

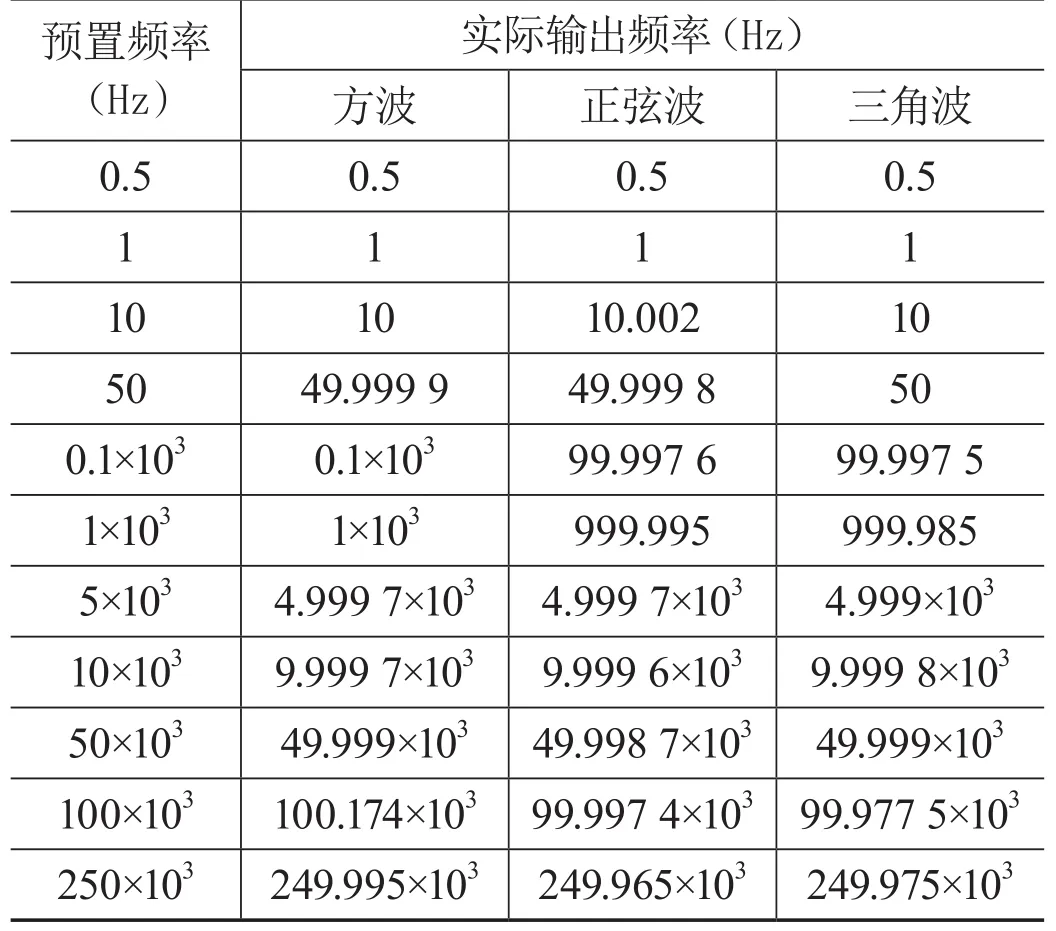

按照上述方案完成系統(tǒng)設(shè)計(jì)后,對(duì)本設(shè)計(jì)進(jìn)行了詳細(xì)的系統(tǒng)測(cè)試,本設(shè)計(jì)的單板、FPGA和模擬電路皆能正常工作,濾波電路也能正常濾波,通過(guò)示波器進(jìn)行觀測(cè),輸出的波形都能夠按照按鍵輸入選擇的模式、頻率和幅度來(lái)輸出。部分相關(guān)測(cè)試數(shù)據(jù)如表1所示。

表1 基本波形的頻率測(cè)量結(jié)果(0.5~250 kHz,步進(jìn)0.5 Hz)

3 結(jié)語(yǔ)

本設(shè)計(jì)采用了FPGA來(lái)實(shí)現(xiàn)DDFS算法,配以INTEL的單片機(jī)89C52來(lái)作為設(shè)計(jì)的控制核心,并配合LCD和按鍵完成人機(jī)交互設(shè)計(jì),從而完成了一個(gè)結(jié)構(gòu)清晰、使用方便且成本低的信號(hào)發(fā)生器設(shè)計(jì),配合以模擬電路,完成高精度、分辨率高的信號(hào)產(chǎn)生[4]。方案的核心是用FPGA設(shè)計(jì)DDFS算法,比采用專用DDS芯片更為靈活方便。通過(guò)CPU重新配置和更新FPGA中的雙端口RAM中的波形數(shù)據(jù),就可以完成任意波形的輸出,具有相當(dāng)大的靈活性[5-6]。FPGA芯片設(shè)計(jì)為PS加載方法,還支持在線升級(jí),既可以將更多的波形設(shè)計(jì)輸入到此系統(tǒng)中,且不會(huì)增加系統(tǒng)的開(kāi)銷,非常靈活多變,這在進(jìn)行教學(xué)研究時(shí)具有很大的實(shí)用價(jià)值。

[1]韓葉祥,朱兆優(yōu),張斌.基于MAX038的程控函數(shù)信號(hào)發(fā)生器的設(shè)計(jì)[J].電子元器件應(yīng)用,2008(5):22-25.

[2]郝小江,羅彪.基于FPGA的函數(shù)信號(hào)發(fā)器[J].電測(cè)與儀表,2008(5):49-51.

[3]易宏,杜志明,吳國(guó)輝,等.基于FPGA的函數(shù)信號(hào)發(fā)生器設(shè)計(jì)[J].電氣電子教學(xué)學(xué)報(bào),2009(6):35-37.

[4]郭振永,鄧云凱,楊松,等.線形調(diào)頻信號(hào)DDS頻率合成源的設(shè)計(jì)與實(shí)現(xiàn)[J].現(xiàn)代雷達(dá),2005(3):56-59.

[5]郭德淳,費(fèi)元春.DDS的雜散分析及頻率擴(kuò)展研究[J].現(xiàn)代雷達(dá),2002(1):63-66.

[6]邱娜靈,楊陽(yáng).一種基于單片機(jī)的函數(shù)信號(hào)發(fā)生器的設(shè)計(jì)與實(shí)現(xiàn)[J].信息通信,2017(5):90-92.

Design of DDFS function signal generator based on FPGA

Huang Li

(Wuhan Railway Vocational College of Technology, Wuhan 430205, China)

The programmable attributes of Field Programmable Gate Array(FPGA)makes it more frequently used in the design of communication system. This paper completes a design with variety of waveform output and high precision digital signal generator uses Direct Digital Frequency Synthesizer(DDFS)algorithm technology and analog circuit as the basic structure. And designs of the smallest system with microcontrollers plus LCD, the key input control and real-time display, which can manually enter the selected output arbitrary frequency variable signal such as square wave, sine wave and triangular wave.

Field Programmable Gate Array; microcontrollers; Direct Digital Frequency Synthesizer; function signal generator

黃麗(1987— ),女,湖北孝感人。