基于FPGA的圖像超分辨率的硬件化實現(xiàn)

鐘雪燕+夏前亮+陳智軍

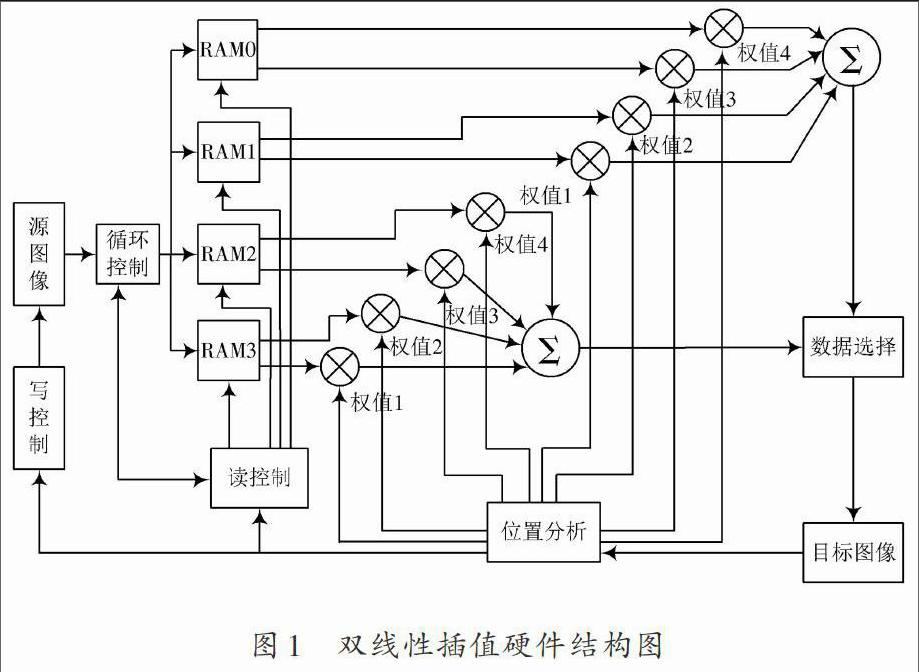

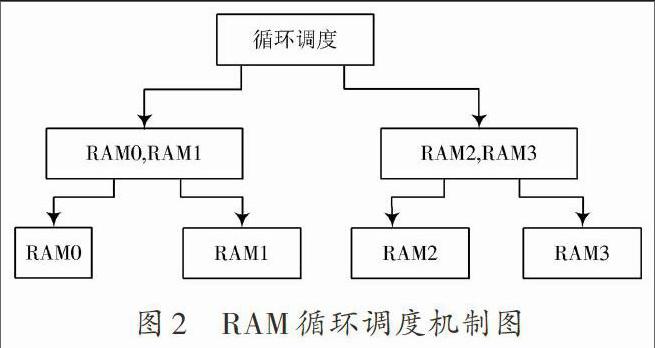

摘 要: 設(shè)計基于FPGA的圖像超分辨率雙線性插值實現(xiàn)方式,提出基于單輸入雙輸出端口RAM緩沖的二級循環(huán)調(diào)度機制,用以實現(xiàn)共享資源分配和并行流水處理。單輸入雙輸出端口的RAM實現(xiàn)讀取相鄰地址的兩個數(shù)據(jù),RAM的深度為源圖像一行的像素點數(shù),寬度為像素數(shù)據(jù)寬度,實現(xiàn)源數(shù)據(jù)相鄰兩行像素的存儲。根據(jù)位置分析模塊得到源圖像的位置,將源圖像的數(shù)據(jù)寫入相應(yīng)RAM中進行加權(quán)運算。為了提高效率使用乒乓算法,設(shè)計了4個RAM,2個RAM為一組,一組RAM在加權(quán)運算時,另一組RAM寫入數(shù)據(jù)。該設(shè)計在Kintex?7開發(fā)板上得到驗證,實現(xiàn)圖像處理速度達到25~30 f/s,同時圖像插值后不僅細節(jié)更加清晰,從直方圖中可以看到圖像得到了均衡化。

關(guān)鍵詞: FPGA; 超分辨率; 雙線性插值; 循環(huán)調(diào)度

中圖分類號: TN911.73?34; TP391 文獻標識碼: A 文章編號: 1004?373X(2017)17?0044?03

FPGA?based hardware implementation of image super?resolution

ZHONG Xueyan1, XIA Qianliang2, CHEN Zhijun3

(1. Nanjing Institute of Railway Technology, Nanjing 210031, China; 2. CETC Deqing Huaying Electronics Co., Ltd., Huzhou 313200, China;

3. Nanjing University of Aeronautics and Astronautics, Nanjing 211106, China)

Abstract: An FPGA?based implementation mode of image super?resolution bilinear interpolation was designed. A two?stage round?robin scheduling mechanism based on RAM with single?input and dual?output port is proposed to realize the shared resource allocation and parallel pipeline processing. RAM with single?input and dual?output port can read two data whose address are adjacent. The quantity of pixels within a row in source image is deemed as the depth of RAM, and the width of pixel data is deemed as that of RAM to store the two rows of pixels adjacent to the source data. The position of source image is gotten according to the position analysis module. The data of source image is written into the corresponding RAM for weighting operation. In order to improve the efficiency, the ping?pong algorithm is adopted to design four RAMs which are divided into two groups (each one includes two RAMs). If one group of RAMs is performed with weighting calculation, another group of RAMs is performed with data write?in. The design was verified on Kintex?7 development board, which can process the image with the speed of 25~30 f/s. The interpolated image has clear detail. The image is equalized, which is shown in histogram.

Keywords: FPGA; super?resolution; bilinear interpolation; round?robin scheduling

0 引 言

通常的圖像顯示設(shè)備具有固定的分辨率,低分辨率的圖像數(shù)據(jù)需要進行超分辨率處理,獲得與顯示設(shè)備相匹配的分辨率才能正常顯示,如High?Definition TV,HDTV,這一過程本質(zhì)上就是一種圖像超分辨處理。

圖像超分辨率技術(shù)在各個領(lǐng)域中得到了廣泛應(yīng)用,如公共安全、醫(yī)學(xué)成像、軍事、地質(zhì)、工業(yè)及消費電子等產(chǎn)業(yè)。通過該技術(shù)盡可能提高圖像的分辨率,達到更好的圖像識別能力和識別精度。

隨著圖像數(shù)據(jù)量的增大,對圖像處理速度提出了更高的要求,利用硬件實現(xiàn)圖像處理已經(jīng)逐漸成為圖形處理領(lǐng)域研究的重要課題。

FPGA由于強悍的數(shù)據(jù)處理能力得到廣泛關(guān)注,其對數(shù)據(jù)采用并行流水式處理方式,加快了數(shù)據(jù)處理速度。用一般軟件對圖像實時處理f/s,F(xiàn)PGA硬件化處理能夠?qū)崟r達到25~30 f/s。因而圖像處理的FPGA硬件化值得研究。endprint

FPGA實現(xiàn)圖像處理算法需要在算法性能和資源使用量之間尋求平衡。傳統(tǒng)的線性插值算法包括最近鄰插值、雙線性插值、四點雙三次插值以及六點雙三次插值,其中最近鄰插值的超分辨圖像效果不理想,高次插值方法復(fù)雜度高不便于硬件實現(xiàn)。本文選擇圖像效果還令人滿意,算法可以硬件實現(xiàn)的雙線性插值算法。

FPGA具有如下兩個對立的性能:

(1) 具有并行處理和流水線技術(shù),能夠達到高性能處理,但倍的性能要耗費倍邏輯;

(2) 具有復(fù)用技術(shù),能夠減少邏輯,但控制復(fù)雜度上升。基于FPGA的功能特性,提出基于單輸入雙輸出端口RAM緩沖的二級循環(huán)調(diào)度機制實現(xiàn)共享資源分配和并行流水處理。同時Xilinx的FPGA基于LUT結(jié)構(gòu),可以實現(xiàn)浮點運算以及乘法運算,但會造成資源的嚴重浪費。本文將所有浮點數(shù)都整數(shù)化,在整數(shù)領(lǐng)域進行數(shù)據(jù)運算。

1 雙線性插值硬件化運算分析

雙線性插值通過四點確定一個平面,是個過約束問題,所以在一個矩形柵格上的一階插值需要用到雙線性函數(shù)。令為兩個變量的函數(shù),定義為四點形成的正方形內(nèi)的任意值,令雙線性方程:

(1)

定義一個雙曲拋物面與已知點擬合。

圖像雙線性插值算法的實現(xiàn)經(jīng)過采樣、水平和垂直線性插值三步來完成。設(shè)分別為源圖像在上的尺寸,分別為目標圖像在上的尺寸,定義兩者的縮放因子則水平方向、垂直方向的縮放因子分別為:

(2)

(3)

定義源圖像水平方向采樣的像素點位置集合:

(4)

定義目標圖像水平方向采樣的像素點位置集合:

(5)

定義兩者圖像像素點之間的映射關(guān)系為,則根據(jù)式(2)可得:

(6)

由此可得目標圖像水平方向第點位置映射到源圖像的像素點位置為:

(7)

得到的是實數(shù),該目標圖像水平方向第點像素插值在源圖像和之間,同時,和對應(yīng)于目標圖像第點與源圖像第點和第點之間相對距離的歸一化值。

令:

(8)

令目標圖像像素值為,源圖像像素值為,則: (9)

同理,在垂直方向的插值為:

(10)

將式(9)代入式(10)得到:

可以發(fā)現(xiàn)式(11)和式(1)是類似的。

2 單輸入雙輸出端口RAM緩沖的二級循環(huán)調(diào)

度機制

由運算分析可知,目標圖像某一點的像素值由源圖像相鄰兩行的相鄰兩點決定,為此設(shè)計了單輸入雙輸出端口RAM,實現(xiàn)讀取相鄰地址的兩個數(shù)據(jù)。定義該RAM的深度為源圖像一行的像素點數(shù),寬度為像素數(shù)據(jù)寬度,實現(xiàn)源數(shù)據(jù)相鄰兩行像素的存儲。

根據(jù)目標圖像存儲像素的位置經(jīng)位置分析模塊得到與此像素點相關(guān)的源圖像的位置以及相應(yīng)位置點的權(quán)值和。寫控制模塊根據(jù)位置分析模塊得到源圖像的位置,控制源圖像的模塊寫入相應(yīng)RAM中。

如圖1所示,在雙線性插值硬件結(jié)構(gòu)圖中定義了4個單輸入雙輸出端口的RAM。其中RAM0,RAM1加權(quán)運算對應(yīng)目標圖像的插值像素值時,RAM2,RAM3寫入目標圖像下一行運算所需的源圖像的像素值;RAM0,RAM1運算結(jié)束后,RAM2,RAM3進行加權(quán)運算,RAM0,RAM1開始寫入源圖像像素值,在時間上實現(xiàn)數(shù)據(jù)連續(xù)運算輸出,空間上實現(xiàn)RAM空間的并行復(fù)用,提高運算效率。

循環(huán)控制模塊控制4個RAM模塊的循環(huán)調(diào)度實現(xiàn)數(shù)據(jù)寫入,如圖2所示,循環(huán)調(diào)度分為兩級:分別為RAM0,RAM1和RAM2,RAM3之間以及RAM0和RAM1之間,RAM2和RAM3之間。RAM0,RAM1和RAM2,RAM3之間在運算目標圖像像素值和寫入源圖像像素值功能間循環(huán)切換;RAM0和RAM1之間,RAM2和RAM3之間實現(xiàn)源圖像像素值循環(huán)寫入。這樣的結(jié)構(gòu)設(shè)計充分利用了FPGA并行流水復(fù)用的特征,既保證了數(shù)據(jù)帶寬的充分利用,又節(jié)省了FPGA的空間資源。

根據(jù)運算分析可知,由位置分析模塊得到的4個權(quán)值是歸一化的小數(shù),F(xiàn)PGA雖然能夠支持浮點數(shù)運算,但需要大量邏輯和布線資源,性能比較差,不利于FPGA的運算,因此將權(quán)值映射到整數(shù)范圍內(nèi)運算。整個運算過程中,是浮點數(shù),權(quán)值基于運算得到,將整數(shù)化,即可將運算都整數(shù)化。浮點數(shù)的整數(shù)化是將對應(yīng)的浮點數(shù)左移相應(yīng)的位數(shù),在乘法運算結(jié)束后右移相應(yīng)的位數(shù)。

3 測試分析及結(jié)論

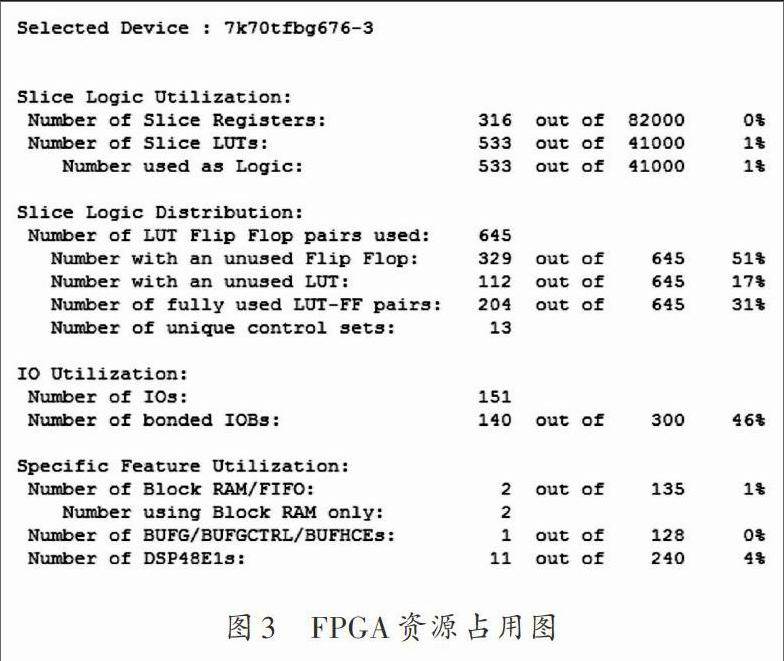

本文在Xilinx公司的Kintex?7開發(fā)板上進行實驗驗證,如圖3所示是該算法占用的FPGA資源,包括645個觸發(fā)器、2個RAM以及11個DSP等,資源占用率不高。

如圖4所示是雙線性插值硬件化實現(xiàn)的建立保持時間圖,從圖4中可以看出,數(shù)據(jù)最少只要保持傳輸即可,意味著時鐘頻率可以達到190 MHz,插值到1 024×1 024像素的時間是5.5 ms,實際使用過程中不采用理想最高頻率,選擇低些的頻率來避免數(shù)據(jù)丟失或錯亂。一般選擇實現(xiàn)25~30 f/s即可。

如圖5所示是插值前后的Lena圖,源圖像的分辨率為512×512,插值后分辨率為1 024×1 024,可以大致看到圖5(b)比圖5(a)細節(jié)方面更加清晰。

圖6是插值前后Lena圖的直方圖比較,從直方圖中可以更直觀地分析圖像的細節(jié)連續(xù)性問題。比較圖6(a)和圖6(b)可以看到,插值后的Lena直方圖比插值前更平滑,說明圖像的連續(xù)過渡性更好,實現(xiàn)了直方圖的均衡化。

4 結(jié) 語

本文基于FPGA的圖像超分辨率雙線性插值實現(xiàn)方式,提出基于單輸入雙輸出端口RAM緩沖的二級循環(huán)調(diào)度機制。通過在kintex?7開發(fā)板上進行實驗驗證,實現(xiàn)了圖像處理速度達到25~30 f/s,在圖像插值后不僅細節(jié)更加清晰,而且從直方圖中可以看到圖像得到了均衡化。

參考文獻

[1] XIAO J P, ZOU X C, LIU Z L, et al. Adaptive interpolation algorithm for real?time image resizing [C]// Proceedings of 2006 IEEE International Conference on Innovative Computing, Information and Control. Beijing, China: IEEE, 2006: 221?224.

[2] WANG Jianzhuang, CHEN Youping, XIE Jingming, et al. Model?based lane detection and lane following for intelligent vehicles [C]// Proceedings of 2010 the 2nd International Confe? rence on Intelligent Human?Machine Systems and Cybernetics. Washington, DC: IEEE, 2010: 170? 175.

[3] 肖建平.圖像超分辨率算法與硬件實現(xiàn)研究[D].武漢:華中科技大學(xué),2006.

[4] 王建莊.基于FPGA的高速圖像處理算法研究及系統(tǒng)實現(xiàn)[D].武漢:華中科技大學(xué),2011.

[5] 馬思博.基于Scaling算法的FPGA驗證[D].北京:北京交通大學(xué),2013.

[6] 盧德貞,范松濤,王新偉,等.距離選通超分辨率三維成像同步控制的研究[J].計算機仿真,2016,33(2):22?26.endprint