基于互補型SET的通用閾值邏輯門設計

應時彥, 孔偉名, 肖林榮, 王倫耀

(1.浙江工業大學 信息工程學院, 浙江 杭州 310023; 2.嘉興學院 電子信息工程系, 浙江 嘉興 314001;3.寧波大學 信息科學與工程學院,浙江 寧波 315211)

基于互補型SET的通用閾值邏輯門設計

應時彥1, 孔偉名1, 肖林榮2*, 王倫耀3

(1.浙江工業大學 信息工程學院, 浙江 杭州 310023; 2.嘉興學院 電子信息工程系, 浙江 嘉興 314001;3.寧波大學 信息科學與工程學院,浙江 寧波 315211)

與MOS管相比,單電子晶體管(SET) 具有超低功耗、超高集成度等優點,被認為是可能取代MOS管的新一代量子器件的主要競爭者.在簡要介紹SET特性及通用閾值邏輯門(UTLG)的基礎上,沿用CMOS邏輯電路的設計思想,提出了功能強大的基于互補型SET的三變量UTLG實現方案.利用一個UTLG輔之少量門電路就可實現全部256個三變量邏輯函數.通過實例說明了利用查表設計進行UTLG綜合的過程.對所設計的SET電路進行了Pspice仿真,結果表明,基于SET的UTLG以及用UTLG實現的全比較器均具有正確的邏輯功能.

單電子晶體管;通用閾值邏輯門;SET電路;電路設計

半導體集成電路技術不斷突破工藝瓶頸向高集成度、高速度、低功耗方向發展.但隨著特征尺寸的不斷縮減,作為主流CMOS技術中的MOSFET器件尺寸將達到其物理極限,且量子效應的顯現可能導致器件失效.因此,科研工作者一方面通過創新半導體制造工藝使CMOS技術得以延續;另一方面也提出了各種可能取代MOSFET的新型電子器件,諸如單電子晶體管(single-electron transistor, SET)、共振隧穿二極管(resonant tunneling diode, RTD)、量子細胞自動機(quantum-dot cellular automata, QCA)等[1-3].其中,SET工作時僅需一個或幾個電子,具有極低的功耗.而且該器件目前與CMOS工藝結合最為緊密,被認為是制造新一代超低功耗、超高密度集成電路最具競爭力的新型納米電子器件之一.因此,SET在數字邏輯電路方面的應用受到了廣泛關注[1,4-6].

閾值邏輯最初作為人工神經網絡的基本單元——神經元而提出.閾值邏輯門因具有獨特的優點而被廣泛應用于神經網絡、圖形處理等領域.在邏輯函數分類和邏輯綜合方面也有其獨特的應用:一個閾值邏輯門可實現任意的線性可分離邏輯函數;用多個閾值邏輯門則可實現任意邏輯函數.但要實現不同的閾值函數(所有三變量邏輯函數中共有104個閾值函數)需設計大量不同結構的閾值邏輯門,這勢必限制了閾值邏輯門在邏輯綜合中的推廣應用.相對而言,通用閾值邏輯門(universal threshold logic gate, UTLG)的功能則更為強大.尤其是三變量UTLG適合作為大規模集成電路的單元電路,而且用一個三變量UTLG以及少量的傳統邏輯門可以實現任意三變量邏輯函數[7-10].文獻[8-10] 分別提出了閾值邏輯門硬件電路的CMOS、RTD、QCA實現方案.本文提出基于SET的三變量UTLG實現方案及其應用,為完善SET單元電路庫并拓展其應用奠定基礎.

1 基礎知識

1.1 SET的特性及互補型SET邏輯門

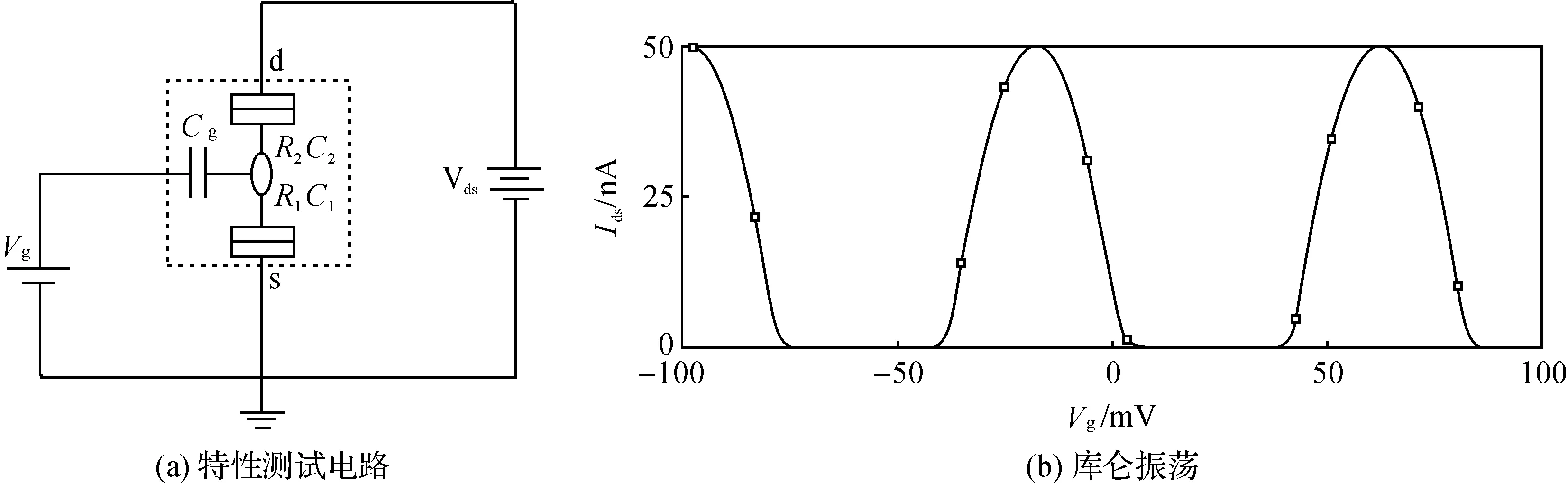

典型的SET是由1個量子點(庫侖島)、2個串聯的隧道結構組成的三端器件,圖1(a)虛線框內為SET的電路符號(橢圓代表庫侖島,帶橫線的矩形框表示隧道結).其中參數Cg為柵極g的耦合電容;與源極s相連的隧道結的電特性用隧穿電阻R1和隧穿電容C1表征;類似地,R2、C2分別代表與漏極d相連的隧道結的隧穿電阻和隧穿電容.值得注意的是:盡管管腳名稱與MOS管相同,但其工作機理卻截然不同,SET是基于庫侖阻塞、單電子隧穿等量子現象的.當漏源極外加合適的電壓Vds時,施加在柵極上的電壓Vg通過耦合電容Cg向量子點感生電荷并操縱單個電子經由器件內的隧道結—量子點—隧道結輸運,從而形成漏源電流Ids.利用圖1(a)可測試SET端口的電特性.圖1(b)所示的庫侖振蕩現象是SET特有的性質之一,即固定偏壓Vds、SET的Ids將隨偏壓Vg的變化周期性振蕩.利用SET的通斷特性可設計構造各種功能的SET邏輯電路,如全加器、觸發器等[1,5-6].相移特性是SET的另一重要特性,即庫侖振蕩特性曲線隨背景電荷Q0的變化沿橫軸Vg方向發生橫向移動.當Q0>0時曲線左移,Q0<0時,則曲線右移.若Q0取值恰當,可使2個SET的庫侖振蕩曲線相位差180°,從而使它們工作在互補的通斷狀態.比照CMOS相關概念,相應的SET分別稱為NSET和PSET.

圖1 SET特性測試電路及庫侖振蕩Fig.1 SET characteristic test circuit and Coulomb blockade oscillations

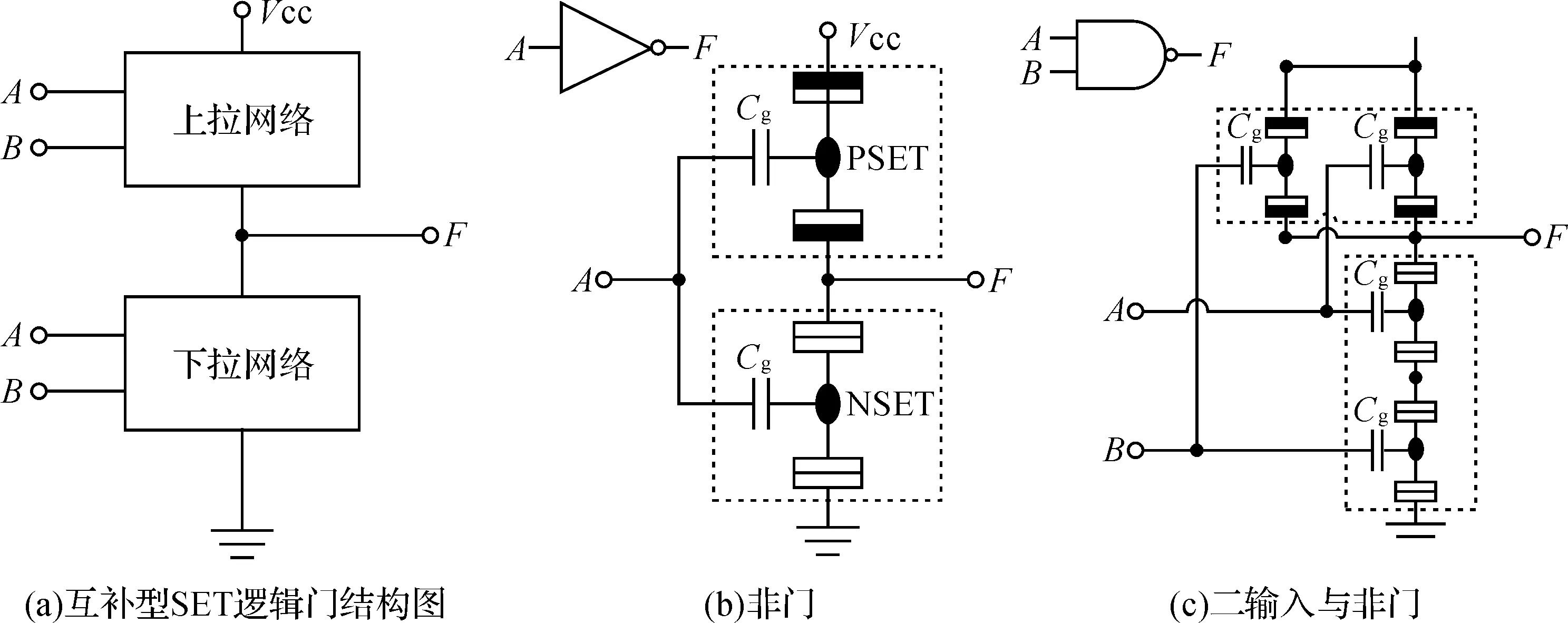

利用NSET和PSET,基于SET邏輯電路設計可方便地沿用CMOS邏輯電路的設計思想.類似地,互補型SET邏輯門可由2個網絡組成,即由PSET構成的上拉網絡和由NSET構成的下拉網絡(如圖2(a)所示).在構造SET基本邏輯門(如非門、與非門、或非門等)時,對下拉網絡中的NSET而言是“串與并或”,而對于上拉網絡中的PSET則為“并與串或”.圖2(b)為互補型SET非門電路;圖2(c)為互補型SET二輸入與非門電路,其上拉網絡中是2個并聯PSET,而下拉網絡中是2個串聯NSET.圖2中SET符號與圖1中的區別在于代表庫侖島的橢圓中填充了黑色(代表Q0不為0),而NSET和PSET的區別在于PSET矩形框的一半被填充了黑色.文中對SET仿真時采用Lientschnig的SET-SPICE模型,PSET和NSET的參數設置除背景電荷外分別為Q0=+0.15 e/-0.15 e外,其余參數取值相同:C1=C2=1 aF,Cg=2 aF,C0=0,R1=R2=105Ω,仿真溫度T=4.2 K[11].

圖2 互補型SET邏輯門及SET基本邏輯門結構圖Fig.2 Representation of complementary SET logic gate and basic SET gates

1.2 閾值邏輯及通用閾值邏輯門

傳統的邏輯電路設計均基于與或非邏輯,對于線性可分離的邏輯函數而言,也可表示為閾值函數.n變量閾值邏輯函數f(x1~xn) =〈w1·x1+w2·x2+···+wn·xn〉t的定義為

(1)

式(1)中wi、t分別稱為權、閾值,輸入變量xi∈{0,1}.須注意的是,式(1)中的·和+分別表示算術運算的乘法及求和,而不是邏輯代數中的或運算及與運算.實現式(1)運算的邏輯門稱為閾值邏輯門(見圖3), 在神經網絡中又稱為感知器神經元.

圖3 閾值邏輯門Fig.3 Symbol of threshold logic gate

2 通用閾值邏輯門的SET電路實現及其綜合

2.1 三變量SET通用閾值邏輯門的電路實現

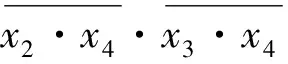

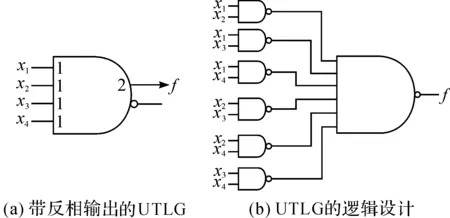

根據閾值邏輯函數的定義,直接利用SET加法器及乘法器電路實現通用閾值邏輯門的電路結構十分復雜.由式(1)及三變量UTLG的定義可列出其真值表,化簡得其函數表達式為f=x1·x2+x1·x3+x1·x4+x2·x3+x2·x4+

(2)

式(2)中的+和·是傳統邏輯代數中的或運算及與運算.圖4(a)給出了帶反相輸出的三變量UTLG的符號,圖4(b)是實現該UTLG的門級邏輯設計,即可由6個二輸入SET與非門、1個六輸入SET與非門構成(f的反相輸出可再經一個非門得到).限于篇幅,文中不再給出具體的SET電路.

圖4 帶反相輸出的三變量UTLG符號及邏輯設計Fig.4 Symbol and its logic design of three-variable UTLG with a complementary output

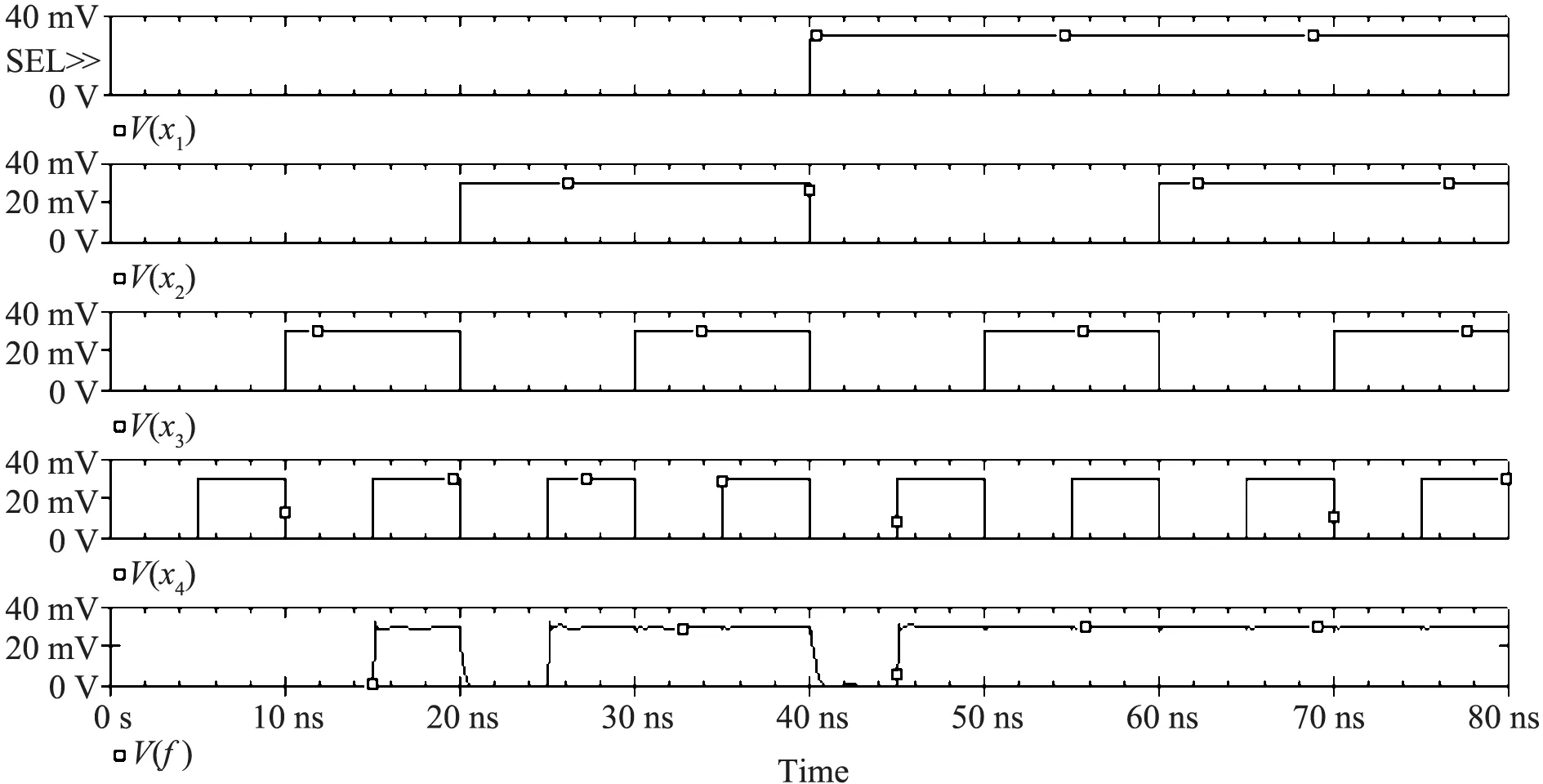

利用Pspice對三變量UTLG的SET電路進行仿真,可得如圖5所示的輸入輸出波形(信號的高低電平分別為30和0 mV),反映所設計的SET UTLG邏輯功能正確.

圖5 基于SET的UTLG的仿真波形Fig.5 Simulation waveforms of UTLG based on SET

2.2 基于SET通用閾值邏輯門的邏輯綜合

利用UTLG進行邏輯綜合有多種方法:如直接按定義的綜合、譜技術綜合等.但對于三變量邏輯函數,最簡便且便于用計算機編程實現的是查表設計法[7].由文獻[7],用SET的UTLG實現任意三變量邏輯函數的步驟如下:

(1)由給定的邏輯函數寫出對應的8進制代碼,查文獻[7]之P分類表得到其P分類代碼.

(2)按P分類代碼中的數字查文獻[7]之P分類代表函數接線表,得對應的接線方案.

(3)按P分類代碼中的英文字母查文獻[7]之接線順序表,確定最終輸入、輸出端接法.

設計實例證明了此綜合方法的有效性.限于篇幅,僅舉一例說明.

圖6 基于UTLG的全比較器邏輯設計Fig.6 Logic structure of full comparator based on UTLG

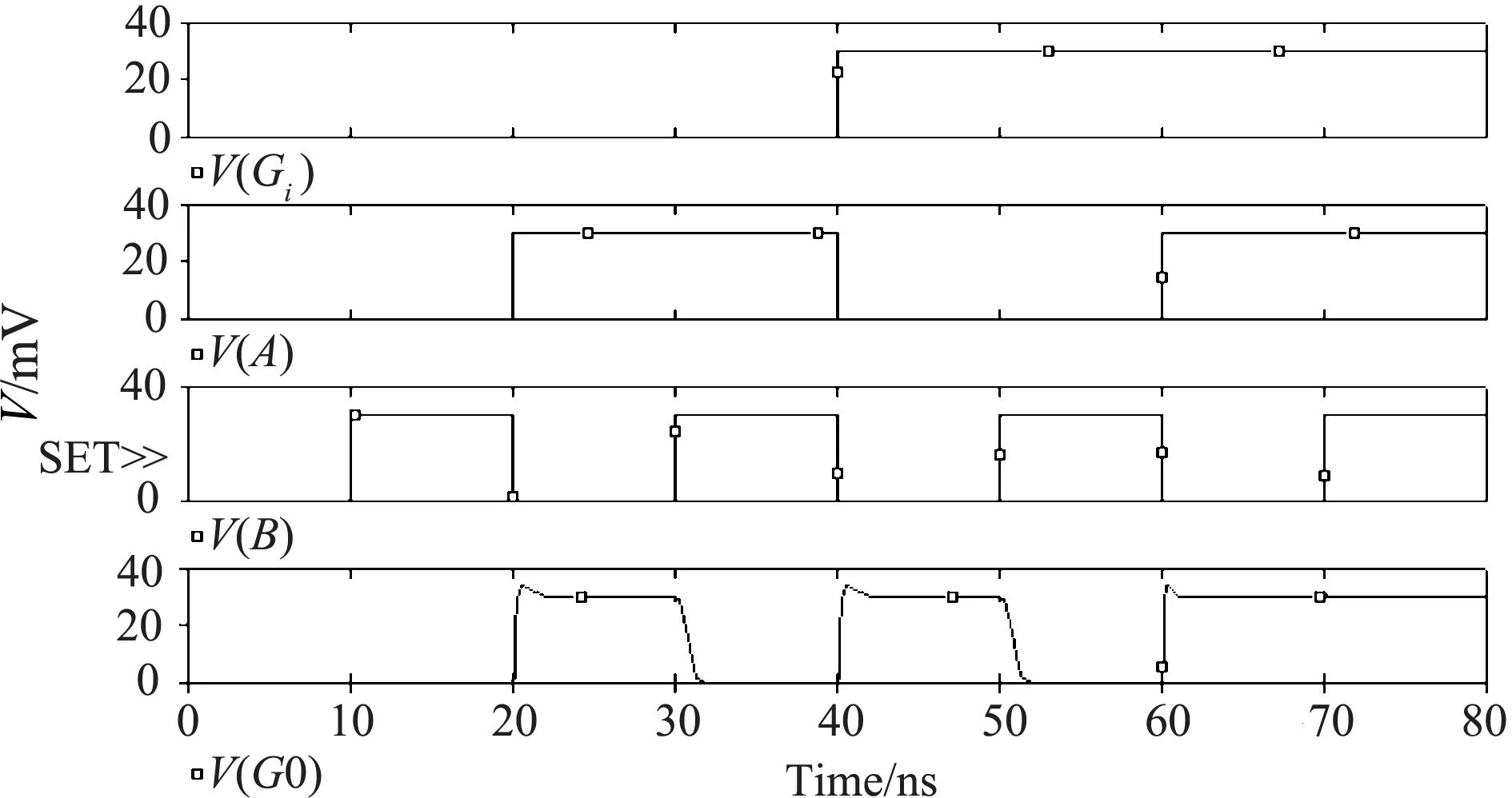

用Pspice 對圖6相應的SET電路進行模擬,所得波形如圖7所示.仿真結果反映了所設計的全比較器邏輯功能完全正確.

圖7 基于SET的UTLG全比較器電路仿真波形Fig. 7 Simulation waveforms of SET based UTLG full comparator

3 結 語

SET作為一種新型量子器件,將來可能取代MOSFET.基于SET獨特的優點以及具有類似互補MOSFET的NSET和PSET結構,沿用CMOS邏輯電路的設計思想,提出用互補型SET邏輯門實現雙輸出UTLG.該邏輯門功能強大,利用一個UTLG及少量的門電路就可實現全部256個三變量邏輯函數.通過實例說明了利用查表設計法進行UTLG綜合的過程.用Pspice 對所設計SET的UTLG以及基于該UTLG的全比較器電路進行模擬仿真,驗證了該設計的正確性.如前所述,UTLG亦可作為感知器神經元,但其在神經網絡等領域中的應用尚待進一步研究.

[1] LIKHAREV K K. Single-electron devices and their application[J]. Proceedings of the IEEE,1999,87(4):606-632.

[2] CHOI S, JEONG Y, LEE J, et al. A novel high-speed multiplexing IC based on resonant tunneling diodes[J]. IEEE Transactions on Nanotechnology,2009,8(4):482-486.

[3] LENT C S, TOUGAW P D, BERNSTEIN G H, et al. Quantum cellular automata[J]. Nanotechnology,1993,4(1):49-57.

[4] MAHAPATRA S, VAISH V, WASSHUBER C, et al. Analytical modeling of single electron transistor for hybrid CMOS-SET analog IC design[J]. IEEE Transactions on Electron Devices,2004,51(11):1772-1782.

[5] 孫鐵署,蔡理.一種基于互補型單電子晶體管的全加器電路設計[J].電子器件,2005,28(2):365-369. SUN T S, CAI L. A full adder realization with complementary single-electrontransistors [J]. Chinese Journal of Electron Devices,2005,28(2):365-369.

[6] 章專,魏齊良,申屠粟民.基于R-SET結構的邏輯門電路和觸發器設計[J].浙江大學學報:理學版,2013,40(3):272-275. ZHANG Z,WEI Q L,SHENTU S M. Design of logic gate and flip-flop based on resistance single-electron transistor structure[J]. Journal of Zhejiang University:Science Edition,2013,40(3):272-275.

[7] 肖林榮,陳冠軍,歷曉華,等.基于三變量雙輸出通用閾值邏輯門的邏輯函數查表綜合[J].科技通報,2005,21(6):746-751. XIAO L R, CHEN G J, LI X H, et al. Tabular design based on three-variable universal-threshold-logic gates with a complementary output[J]. Bulletin of Science and Technology,2005,21(6):746-751.

[8] 胡昌興,陳楷雄,王大能.基于電流型CMOS電路的閾值邏輯門[J].杭州大學學報:自然科學版,1997,24(2):133-137 HU C X, CHEN X X, WANG D N. Threshold logic gates based on current-mode CMOS circuits [J]. Journal of Hangzhou University:Natural Science Edition,1997,24(2):133-137.

[9] YI W, SHEN J Z. Novel universal threshold logic gate based on RTD and its application[J]. Microelectronics Journal,2011,42(6):851-854.

[10] 肖林榮,陳偕雄,應時彥.基于量子細胞自動機的三變量通用閾值邏輯門電路實現[J].浙江大學學報:理學版,2010,37(5):546-550. XIAO L R, CHEN X X, YING S Y. Implementation of three-variable universal-threshold-logic gates using quantum-dot cellular automata[J]. Journal of Zhejiang University :Science Edition,2010,37(5):546-550.

[11] 許翔,應時彥,肖林榮.基于PSpice的單電子器件模型創建及其應用[J].半導體技術,2015,40(4):284-288. XU X,YING S Y, XIAO L R. Creation and application of single electron transistor model based on PSpice[J]. Semiconductor Technology,2015,40(4):284-288.

Design of universal threshold logic gate based on complementary SET.

YING Shiyan1, KONG Weiming1, XIAO Linrong2, WANG Lunyao3

(1.CollegeofInformationEngineering,ZhejiangUniversityofTechnology,Hangzhou310023,China;2.DepartmentofElectronicInformationEngineering,JiaxingUniversity,Jiaxing314001,ZhejiangProvince,China; 3.FacultyofInformationScienceandEngineering,NingboUniversity,Ningbo315211,ZhejiangProvince,China)

Compared with MOSFET, single electron transistor (SET) has the advantages of ultra-low power consumption and ultra-high integration level, which make it the major candidate for the next generation nano quantum devices. Based on the introduction of SET characteristics and concepts of CMOS logic circuits, a three-variable complementary SET universal threshold logic gate(UTLG)is proposed. All of 256 three-variable logic functions can be realized with a UTLG and only a few logic gates. A full comparator, as an example, is also presented to demonstrate the tabular design procedure of three-variable logic function using a UTLG. The proposed UTLG and SET full comparator are simulated with Pspice and their logic functions are confirmed.

single-electron transistor; universal threshold logic gates; SET circuits ; circuit design

2016-02-03.

國家自然科學基金資助項目(62471211);浙江省自然科學基金資助項目(Y1110808).

應時彥(1964-),ORCID:http://orcid.org/0000-0002-1892-3810, 男,博士,教授,主要從事電子信息技術及計算機應用研究,E-mail:ysy@zjut.edu.cn.

*通信作者,ORCID:http://orcid.org/0000-0002-0589-3966,E-mail:xiaolr@126.com.

10.3785/j.issn.1008-9497.2017.04.007

TP 331

A

1008-9497(2017)04-424-05

Journal of Zhejiang University(Science Edition), 2017,44(4):424-428