基于FPGA的納秒量級脈沖寬度精確測量研究

于龍洋,劉曄,孫培欽,張耀勻

(西安交通大學電氣工程學院,陜西 西安 710049)

基于FPGA的納秒量級脈沖寬度精確測量研究

于龍洋,劉曄,孫培欽,張耀勻

(西安交通大學電氣工程學院,陜西 西安 710049)

為使測量光電開關發出的數字脈沖寬度的精度達到1ns和掌握光電開關的實時工作狀態。該文通過基于FPGA精確測量法的直接計數法和移相計數法進行測量,得出移相計數法的測量誤差在1ns左右,并驗證其設計的正確性和有效性。設計通信系統和上位機軟件進行實時監控,通信系統采用成熟的串口RS232通信方式,用PFGA設計串口通信模塊,實現將數據傳輸到工控機;再用LabVIEW編寫上位機軟件,便于工作人員直觀觀察數據并存儲數據到Excel,實驗結果證明測量系統可靠、有效。

納秒量級;FPGA;串口通信;LabVIEW

0 引言

隨著控制技術的發展,精確監控光電開關的工作狀態是工程實際急需解決的問題,其測量精度達到納秒量級也是工業自動化技術發展到一定階段的需求。文獻[1]提出的基于DSP結合混沌算法實現的精度測量算法雖然有著廣泛的應用前景,但是其系統非常復雜,且成本高。文獻[2]提到利用鈮酸鋰晶體的電光效應,其研制可用于測量納秒量級脈沖電壓的傳感器,但是其誤差范圍在5~7ns,達不到1ns的誤差要求。文獻[3]基于移相技術的脈沖寬度測量方法能實現納秒量級測量,且提供了測量數字脈沖的思路,但所需晶振頻率達到250MHz,且FPGA芯片價格昂貴,因此本文在此基礎上進一步改進其移相技術算法來降低倍頻時鐘信號,實現低成本的可靠測量系統。論文在脈沖寬度測量方面采用了直接計數法和移相技術法兩種算法,并且設計了FPGA與上位機之間的通信。通信系統采用成熟的串口RS232通信方式,LabVIEW在測量領域內是比較普遍的應用軟件,與C++等編程語言相比,其圖形化語言易理解,存在一定優勢。

1 測量原理

1.1 直接計數法

利用FPGA內部鎖相環(PLL)模塊將外部輸入晶振頻率倍頻到1GHz,使得周期變為1 ns,將其時鐘作為計數器時鐘對外部脈沖進行計數,這樣其計數誤差最大不會超過1ns。因此,使用FPGA內部計數器對鎖相環(PLL)倍頻的1GHz進行計數從而達到納秒量級的精度,再等待光電開關產生的外部脈沖信號進入[4-6]。以光電開關產生的正脈沖為例,設置計數器上升沿觸發開始以PLL模塊產生的1GHz進行計數,以外部脈沖的下降沿為結束。計數結果為外部脈沖寬度,其誤差在1ns左右。時鐘為1GHz,一旦外部脈沖產生其上升沿將觸發計數器開始計數,等待外部脈沖下降沿到來停止計數器工作,最終計數器累計數值為測得外部脈沖寬度。算法整體框圖如圖1所示。

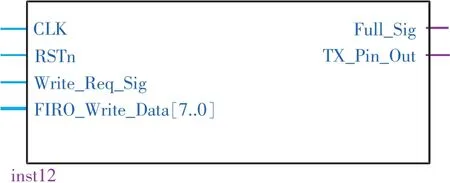

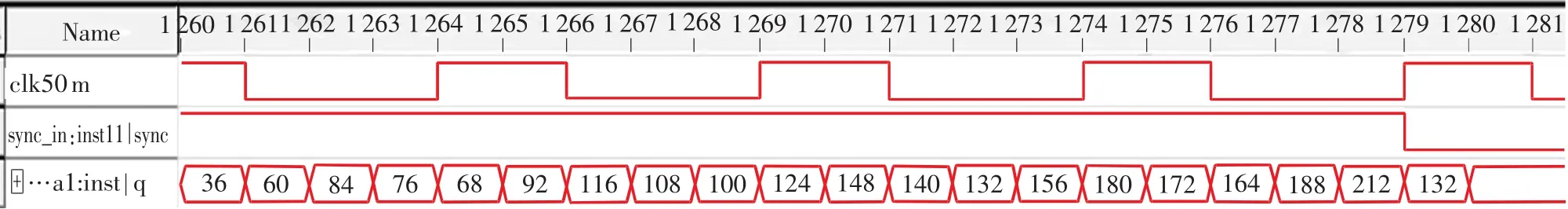

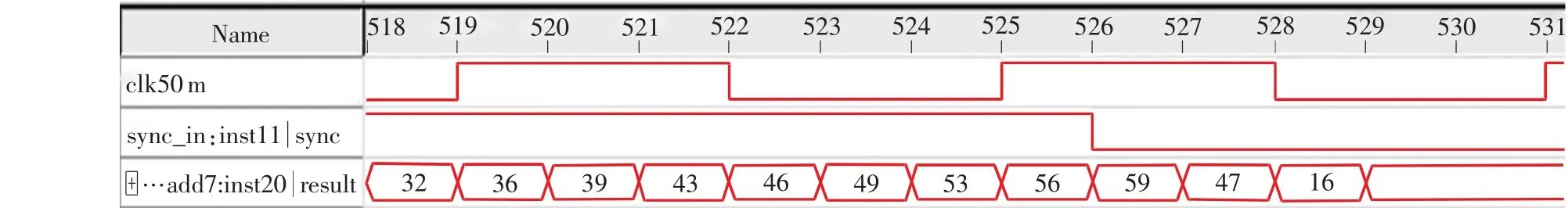

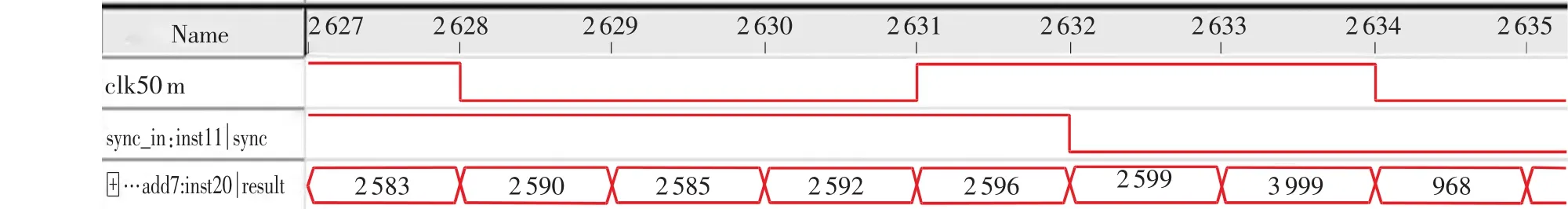

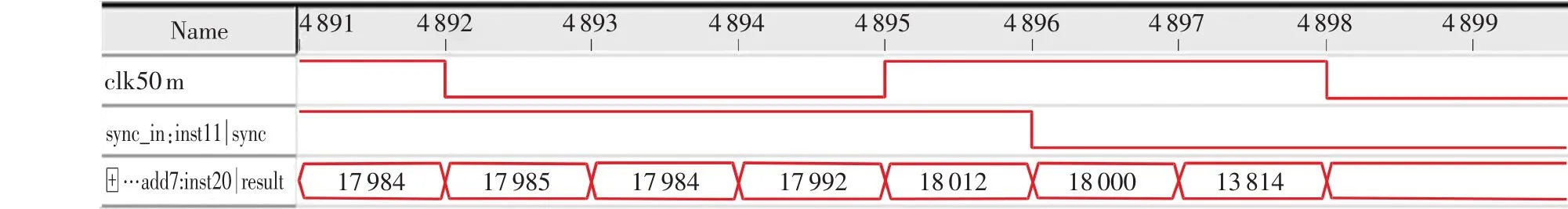

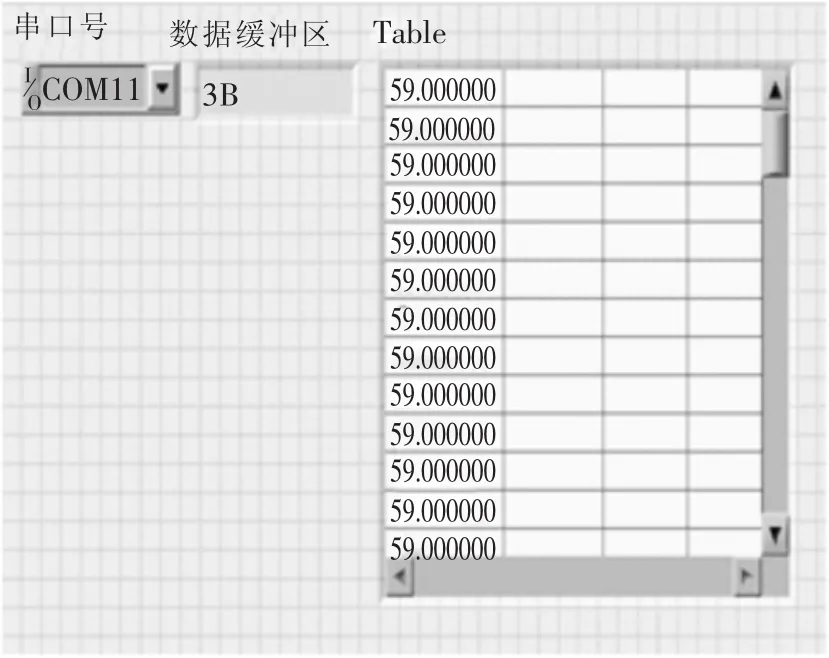

圖1 直接計數法

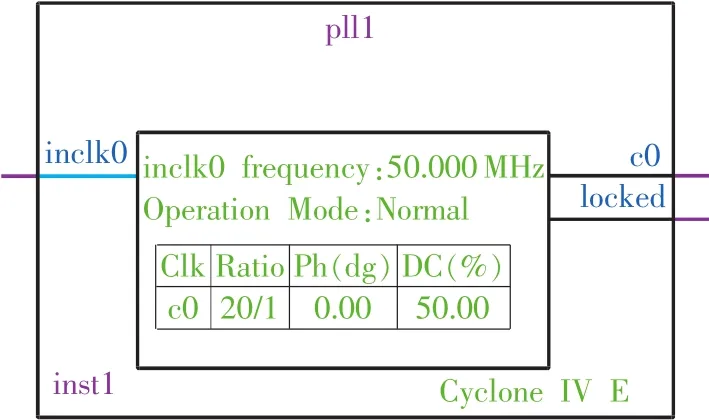

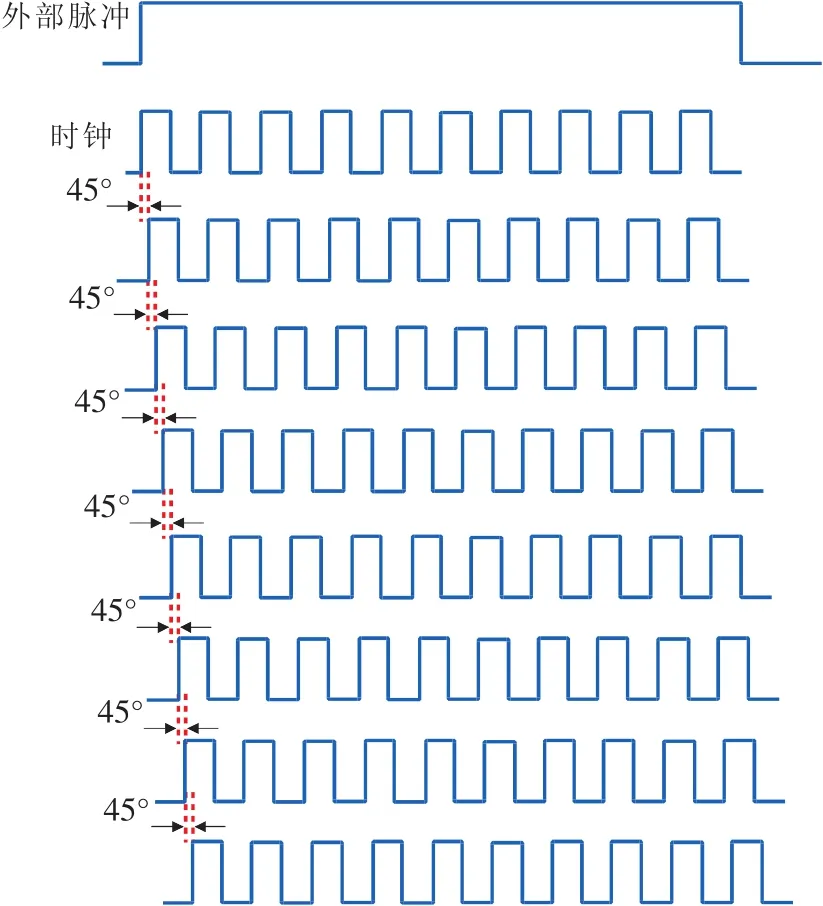

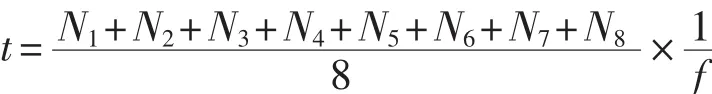

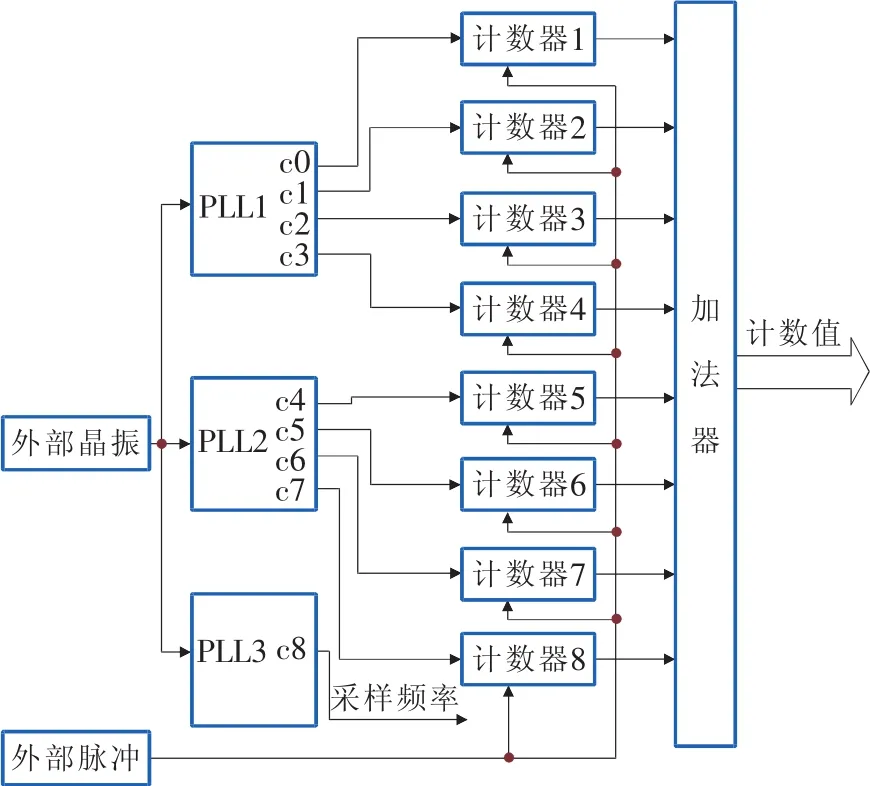

由于FPGA內部有許多IP核,如加法器、FIFO、PLL、COUNTER已經集成,不需要進行編程可以直接設置需要的IP核,為實現各種算法提供了極大便利。FPGA鎖相環模塊如圖2所示。PLL模塊的inclk0為外部輸入晶振輸入端,c0為PLL模塊倍頻輸出端口。通過對PLL模塊進行設置使c0達到1GHz。計數器模塊如圖3所示。clock為時鐘輸入端,與c0相連,cin為外部脈沖輸入端,sclr為清除端,在外部脈沖下降沿到來之后將計數器清0,以便對下一個到來的外部脈沖重新計數。q為32位的計數寄存器,用于儲存計數結果。將計數器設置為上升沿使能從而達到本次實驗所需要求[7]。為模擬產生一個外部脈沖,在FPGA內部模擬了一個高脈沖來測試搭建的測量模塊,設計了一個脈沖發生器,脈沖發生模塊算法流程如圖4所示。圖中a與b為一個常量且a 圖2 PLL模塊的配置 圖3 counter模塊的配置 圖4 脈沖發生器算法 1.2 移相計數法 直接計數法使測量精度達到納秒量級就必須使用更為高端的FPGA芯片,其性價比不高。本文介紹一種基于FPGA的移相計數法,可以用中低端FPGA實現其精度,從而極大地降低成本[7-8]。 為實現外部脈沖信號納秒量級精確測量,本文結合數字移相技術,設計了改進型移相脈沖寬度測量技術,其優勢在于FPGA無需倍頻至1GHz,就能實現1ns的誤差精度。由于FPGA內部鎖相環(PLL)設置時鐘多輸出功能和各輸出時鐘相位功能,使得多個時鐘信號輸出各產生一定的相位差來等效1GHz的時鐘信號。原理如圖5所示。 圖5 移相計數法測量原理 通過FPGA內部鎖相環移相功能,FPGA的晶振所產生的50MHz時鐘信號進行相鄰信號依次相差45°處理,例如以第1路輸出時鐘信號CLK相位為0°,那么其他信號則依次為CLK45°、CLK90°、CLK135°、CLK180°、CLK225°、CLK270°、CLK315°,然后用FPGA內部鎖相環多路輸出功能產生這8路時鐘信號,原理如圖6所示。然后將8路信號分別驅動一個計數器,8個計數器分別用N1、N2、N3、N4、N5、N6、N7和N8表示。據此可以精確測量出外部脈沖寬度t,其計算公式為 式中f為8路時鐘信號的頻率。 對8路時鐘信號所驅動的計數器的計數值進行相加相當于采用了8倍頻的時鐘頻率為8f的信號來測量外部脈沖信號,即時鐘信號的周期1/8,從而在不提高時鐘頻率的情況下實現精度要求,其等效的時鐘信號如圖6所示。由圖可見,在計數時鐘頻率為125MHz時,這種測量方法可得到時鐘頻率為1GHz的等效時鐘,從而使測量精度達到要求,并且大部分中低端FPGA內部鎖相環都可以實現125MHz的時鐘信號。文獻[3]提到的4路輸出移相的方法相當于PLL模塊要輸出250MHz的輸出時鐘頻率,然而這種頻率在中低端FPGA的鎖相環倍頻不是很穩定,從而使測量不精確,無法達到要求。 圖6 1GHz等效的8路時鐘信號 移相測量方法依然在直接計數法的基礎上,等待外部脈沖到來,其上升沿使能8個計數器開始計數,等到外部脈沖下降沿到來停止計數,將8個計數值再通過FPGA內部的加法器相加,最終數值為數字脈沖寬度。總體算法框圖如圖7所示。 圖7 總體算法 實驗所使用的FPGA是在ALTERA公司的Quartus II環境下選用Cyclone IVE系列的EP4CE15F17C8芯片進行設計并仿真[9-11],此芯片鎖相環(PLL)模塊最多有5路時鐘信號輸出,因此必須使用兩個鎖相環模塊產生8路時鐘信號,其中每個鎖相環產生4路時鐘信號,第3個鎖相環是為了產生采樣頻率而設置,由于每一路時鐘信號的頻率為125MHz,根據香農采樣定理,采樣頻率必須不低于最大采樣信號的2倍,所以經過多次實驗用鎖相環3產生300MHz的采樣頻率。8個時鐘信號各自驅動計數器,等待外部脈沖到來與結束,將計數結果加和后送出。 實驗依然使用鎖相環模塊,不過這次使用2個鎖相環模塊產生8路依次相差45°時鐘信號,并且每路信號經鎖相環倍頻到125MHz。仿真如圖8所示。 圖8 PLL配置的8路時鐘信號 圖中inclk0為外部輸入晶振50MHz,PLL1的c0、c1、c2、c3為頻率125MHz的時鐘輸出,相位角分別為0°、45°、90°、135°,PLL2的c0、c1、c2、c3也為頻率125MHz的時鐘輸出,相位角分別為180°、225°、270°、315°,從而形成8路相位依次相差45°的時鐘輸出來驅動計數器。其原理為在脈沖計數法基礎上,采用8個計數器計數。計數器的clock分別連接鎖相環的8路輸出時鐘信號,然后再用加法器將計數器輸出值相加。 2.1 串口通信 經FPGA測量出的信號可以通過串口RS232與PC機相連傳輸數據,電腦上位機用LabVIEW軟件開發平臺開發,將測得數據顯示在上位機軟件上。 實驗的開發板上帶有串口RS232,再接一個串口與USB的轉接線連接PC機,與下位機的串口通信也使用轉接線來完成。FPGA與工控機或PC機的整體框架如圖9所示。 整體思路是將關電開關產生的脈沖經過FPGA移相脈沖計數法處理得到精確的脈沖時間,放入FPGA內部緩沖器FIFO中,等待串口通信模塊空閑時發送FIFO內的數據到PC機的COM端口,用LabVIEW設計上位機軟件將脈沖時間數據顯示在PC機上[12-13]。首先,必須設計一個緩存器FIFO,因為外部脈沖任意時刻都可能產生,一旦外部脈沖產生會觸發8個計數器模塊開始計數得到的計數結果直接通過串口模塊發送,PC上將顯示整個計數器計數的所有數據,所以設計FIFO就是在外部脈沖下降沿到來觸發FIFO寫使能,將最終計數結果存入到FIFO中等待串口發送模塊發送給PC機。串口通信模塊如圖10所示。 圖9 系統結構 圖10 串口通信模塊 圖中FIFO模塊已經集成在串口通信模塊中,引腳CLK為125MHz,RSTn為復位引腳,Write_Reg_Sig為FIFO寫使能,FIFO_W rite_Data為寫入FIFO的數據,TX_Pin_Out為串口232發送引腳。在串口通信方面,FIFO起著非常重要的數據緩沖的作用,如果串口通信沒有FIFO來緩存數據,有可能測量系統將測量的數據傳輸到串口發送模塊時,串口發送模塊處于忙狀態,導致傳輸的數據丟失從而導致測量系統的性能變差,這在工程設計方面是絕對不允許的。 2.2 上位機設計 首先,FPGA將測量數據發送至PC機COM口,使用LabVIEW搭建一個串口接收模塊,由于串口接收的是字符串,需進行處理后再送入表格中顯示出來。編寫的軟件界面分為串口號、數據緩沖區和表格3個部分。其中串口號就是來選擇FPGA串口所連接的COM口,數據緩沖區為所選串口中的數據,表格是將數據緩沖區的數據進行處理后顯示的顯示控件。 串口RS232每次發送一幀,每一幀為11位,包括1個起始位、1個結束位、1個校驗位和8個數據位。一幀有效位為8位,然而光電開關的數字脈沖寬度在幾微秒到幾百微秒之間,遠超過8位數據的范圍,因此將FPGA測量數據設為32位以滿足需求,將32位測量數據分成4組8位數據放入FIFO中等待串口發送模塊傳輸。通過串口接收模塊接收FPGA串口發送模塊傳輸的字符串,String Subset模塊截取相應的8位數據,經數值化處理過后整合成32位數字脈沖寬度,再傳輸至Build Table與Write to spread sheet File模塊中顯示。 3.1 直接計數法的結果與分析 在Quartus II環境下選用Cyclone IVE系列的EP4CE15F17C8芯片對設計進行驗證,并用邏輯分析儀查看結果。如圖11所示,為120 ns寬度的脈沖信號。圖中clk50m為外部輸入晶振50MHz,sync_in為外部脈沖信號,add1為計數器計數值。可以看出,計數器最終計數的值為132 ns與設定的外部脈沖120ns相差12ns,誤差已經遠遠超過了1ns范圍,說明實驗使用的中低端PFGA芯片無法實現1ns的精度,無法直接倍頻穩定1GHz的時鐘信號,對于低成本測量系統來說,直接計數法不適用。 3.2 移相計數法的結果與分析 用脈沖產生模塊產生60,2600,18000ns,實驗結果見圖12~圖14。圖中,clk50m是外部50MHz的晶振,sync是脈沖產生模塊產生的被測量脈沖,result是8個計數器計量結果,由于選用的采樣頻率是300MHz,所以無法完整的從邏輯分析儀中看PLL模塊倍頻的125MHz,如果再提高采樣頻率由于這個型號FPGA自身的硬件設備原因將無法進行實驗。 脈沖寬度設定值與實驗測量值見表1。由表可見,比較脈沖寬度設定值與測量值可知,其誤差為1ns左右,符合設計目標。 表1 脈沖寬度實際值與測量值 圖11 實驗結果 圖12 60ns脈沖波測量結果 圖13 2600ns脈沖波測量結果 圖14 18000ns脈沖波測量結果 3.3 上位機界面測試 實驗用FPGA內部脈沖發生器產生60 ns的高脈沖進行實驗,實驗結果如圖15所示。圖中表格中顯示的數據跟Quartus II的邏輯分析儀顯示的被測數據一致,足以證明串口發送模塊設計的準確性,其中數據緩沖區3B為字符串16進制顯示,轉化成10進制數值就是表格Table中的數據。 圖15 60ns實驗結果 雖然本文實現了對FPGA測量數據可視化顯示,但是一旦關閉工控機軟件顯示在表格中的數據也會隨之消失,無法對測量數據進行保存。LabVIEW則提供了數據保存相關的集成模塊能將測量系統傳輸的數據及時保存。通過編程在工控機軟件基礎上采用Excel來保存系統測量數據,并且測量數據能實時傳輸到Excel中,且在工控機軟件關閉的情況下,會將測量數據緊接著上組數據下方進行儲存。實現保存測量數據的功能。 針對基于FPGA設計的兩種脈沖寬度測量方法,直接計數法雖然原理較為簡單,但是一般中低端FPGA很難能倍頻1GHz時鐘信號,高端FPGA雖然能實現算法,但成本過高。 在基于直接計數法的基礎上,改進了第一種算法的局限性,設計了基于移相測量算法,其優點為鎖相環模塊不需要直接倍頻到1GHz,通過8路時鐘信號依次相差45°來等效1GHz的時鐘信號,每一路時鐘信號僅125MHz頻率,使得多數中低端FPGA的鎖相環模塊都可以得以實現,極大地降低了整個測量系統的成本。 在串口通信方面,采用了簡單可靠的串口RS232的數據傳輸方式,實現了與工控機之間的基本通信,這種方式優點突出,可靠性高、成本低、易實現,但是有線通信的局限性比較突出使得工控機必須在一定范圍內,距離過遠會影響通信質量。隨著工程需求可以進一步將有線串口通信改成無線通信,能符合大部分工程需求。 LabVIEW是一種G語言編寫模式,圖形化編程對于編程人員來說易上手,可以節約大量開發時間,并且在做測量系統方面有著較大優勢,有很多集成好的模塊可以直接應用,例如串口通信模塊,通過LabVIEW編寫工控機實現PFGA測量數據的傳輸,實現了整個測量系統的功能。 [1]萇凝凝,魯昌華,劉春.納秒級周期脈沖信號檢測方法的研究[J].電子測量與儀器學報,2006,20(4):86-101. [2]郭小明,蘇進喜,羅承沐,等.納秒級脈沖電壓的電光測量[J].清華大學學報(自然科學版),1997,37(4):65-67. [3]仵曉輝,師廷偉,金長江.基于移相技術的脈沖寬度精確測量方法及FPGA實現[J].周口師范學院學報,2012,29(2):108-109. [4]王玨,張適昌,嚴萍,等.用自積分式羅氏線圈測量納秒級高壓脈沖電流[J].強激光與粒子束,2004,16(3):399-404. [5]ZHANG Y B,JI F,LIU G M,et al.Communication between industrial computer and micro-energy pulse power supply with nanosecond pulse width[C]∥International Conference on Advanced Technology of Design and Manufacture.ATDM,2010:413-418. [6]STENHLM T J,SOINI JT,H?NNINEN P E.A long-arm autocorelator for measurement of pico-to nanosecond laser pulse widths[J].Measurement Science and Technology,2004,15(10):1525-1531. [7]張志剛.FPGA與SOPC設計教程:DE2實踐[M].西安:西安電子科技大學出版社,2007:57-65. [8]陳傳波,杜娟,張智杰.WIN32下基于RS232C協議的串口通信方法及應用研究[J].南昌大學學報(工科版),2005,27(3):71-76. [9]楊建偉,鄭瓊華,沈昱明.基于LabVIEW的數據保存[C]∥第八屆工業儀表與自動化學術會議論文集.上海:中國儀器儀表學會,2007:485-489. [10]陳錫輝,張銀鴻.LabVIEW 8.20程序設計從入門到精通[M].北京:清華大學出版社,2007:97-115. [11]施雅婷,郭前崗,周西峰.一種改進的LabVIEW串口通信系統的實現[J].電子測試,2010,8(8):64-70. [12]HAN X H,KONG X X.The designing of serial comm unication based on RS232[C]∥ACIS International Symposium on Cryptography,and Network Security,Data Mining and Knowledge Discovery,E-Commerce and Its Applications,and Embedded Systems.IEEE,2010:382-384. [13]MACHACEK J,DRAPELA J.Control of serial port(RS-232)communicaton in LabVIEW[J].Modern Technique and Technologies,2008(37):121-127. (編輯:李妮) A nanosecond level measurement method of pulse w idth based on FPGA YU Longyang,LIU Ye,SUN Peiqin,ZHANG Yaoyun In order to make the width of digital pulse generated by photoelectric switch reach the precision of 1ns approximately grasp the real-time working state of the photoelectric switch.This paper proposed two FPGA-based accurate measurement methods to measure the precision,directing counting method and phase shift counting method were included.The experiments show that the error of the phase shift counting method is about 1 ns,which verifies its correctness and effectiveness.The communication system and software of IPC were also designed in this paper.The communication system used a RS232 serial interface and the serial communicationmodule transfers data to the IPC was designed by FPGA;IPC software was written by LabVIEW,which enables the data to be observed intuitively and stored to Excel easily.The experimental results show that the design of the system is correct and effective. nanosecond;FPGA;serial communication;LabVIEW A 1674-5124(2017)05-0005-06 10.11857/j.issn.1674-5124.2017.05.002 2016-09-18; 2016-11-20 于龍洋(1992-),男,陜西寶雞市人,碩士研究生,專業方向為控制理論與科學。

2 測量系統設計

3 實驗結果與分析

4 結束語

(School of Electrical Engineering,Xi’an Jiaotong University,Xi’an 710049,China)