高速模擬數據源系統的電源設計

吳 凱,張 磊,2*,佟首峰,2,李曉龍

(1.長春理工大學空間光電技術研究所,長春 130022;2.長春理工大學空地激光通信技術國防重點學科實驗室,長春 130022;3.長春理工大學電子信息工程學院,長春 130022)

高速模擬數據源系統的電源設計

吳 凱1,張 磊1,2*,佟首峰1,2,李曉龍3

(1.長春理工大學空間光電技術研究所,長春 130022;2.長春理工大學空地激光通信技術國防重點學科實驗室,長春 130022;3.長春理工大學電子信息工程學院,長春 130022)

針對星上高速載荷模擬數據源系統的需求,采用三輸出10 A降壓型微型模塊穩壓器LTM4633設計了一套開關電源供電模塊,產生11種輸出電壓,輸出電流高達20 A,并且利用LTspice IV仿真軟件對電源電路進行仿真分析,保證FPGA邏輯電路和收發器GTX的上電順序符合設計要求,同時改善輸入和輸出濾波來降低輸出電壓的紋波噪聲,紋波范圍12 mV~50 mV,實驗測試輸出電壓與仿真一致,為整個模擬源系統的正常工作提供了保障。

開關電源;LTM4633;LTspice IV;FPGA;上電順序

隨著現場可編程門陣列FPGA的快速發展,FPGA向著集成度更高,速度更快,功能更強,功耗更大,供電系統更復雜的方向發展[1-2],FPGA供電要求由原來的1種~2種電源(Kintex)供電向十幾種電源(Kintex-7)供電發展,并且這么多種電源中,對電源加電順序也有一定的要求[3],傳統的電源設計方法已經不再使用。在眾多電源芯片生產廠家中,凌力爾特公司的電源模塊具有紋波噪聲小,輸出功率大,單片電源輸出路數多等優點,同時推出功能強大的開關電源設計及仿真軟件Ltspice IV,成為眾多電路設計者的選擇[4-5]。本文采用4片穩壓器芯片LTM4633為基于FPGA的模擬數據源系統設計了一種12 V轉1 V、1.2 V、1.5 V、1.8 V、3.3 V、5.5 V等輸出電壓的開關電源模塊。

1 模擬源系統電源需求

為了滿足星間激光通信在地面上的演示試驗需求,研究并設計了一種基于FPGA的高速載荷智能化數據模擬源,系統框圖如圖1所示。模擬源的主要功能是模擬星上有效載荷的數據輸入與輸出,既要將多路視頻、音頻信號復用成一路高速串行數據流經過光調制發送出去,又要實現高速偽隨機序列的傳輸用于誤碼率測試[6]。同時對接收信號進行解復用,還原出音視頻信號。本文主要討論模擬源系統的電源模塊設計。

圖1 模擬源系統框圖

1.1 FPGA主芯片的供電

FPGA是高度可配置的邏輯器件,可以在它周圍放置不同的組件來完成最終系統設計。雖然會有各式各樣的應用系統,但是所有設計的一個共同特點就是它們全都需要電源。根據應用的不同,主輸入電源可以采用背板電源、隔離電源、非隔離電源,甚至是電池供電的方式。這些主輸入通常生成一個中間DC電壓來為FPGA的主電壓軌供電。這些中間電壓通常為5 V或12 V的DC電壓。

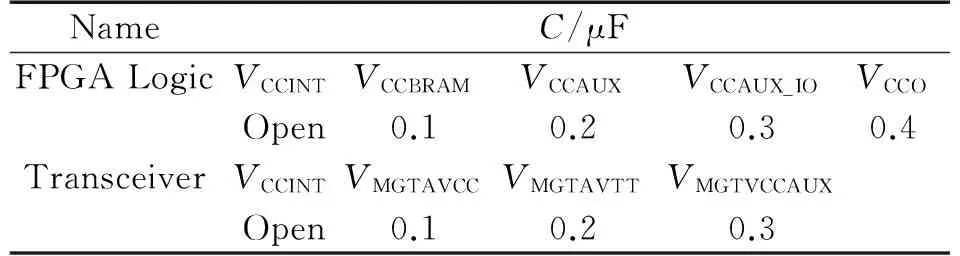

本設計中選用Xilinx公司的Kintex-7系列FPGA芯片XC7K325T-2FFG900I,該芯片一共需要8種電源,內核電壓VCCINT(1.0 V),Block RAM供電電源VCCBRAM(1.0 V),輔助供電電壓VCCAUX(1.8 V),輔助IO供電電壓VCCAUX_IO(1.8 V),IO電源VCCO(1.2 V、1.8 V,2.5 V或3.3 V)[3],本設計中IO供電使用3.3 V,高速收發模塊GTX的QPLL模擬供電電源VMGTAVCC(1.0 V),高速收發模塊GTX的發送、接收終端供電電源VMGTAVTT(1.2 V),高速收發模塊GTX的QPLL輔助模擬供電電源VMGTVCCAUX(1.8 V),高速收發模塊GTX的電阻校準電路模擬供電電源VMGTAVTTRCAL(1.2 V),此電源可與VMGTAVTT共用同一個電源,上述8種電源在上電瞬間或工作過程中需要的電流有可能會比較大,因此,每種電源都由電源芯片獨立提供。上述8種電源在上電順序上還有一定的要求,官方建議邏輯電路的加電順序為VCCINT、VCCBRAM、VCCAUX、VCCAUX_IO和VCCO。收發器的加電順序為VCCINT、VMGTAVCC、VMGTAVTT和VMGTVCCAUX。由于有數個電源軌為FPGA供電,上面推薦的電源序列在啟動時汲取最小電流,這反過來防止了對器件的損壞。表1列出了FPGA的供電要求。

表1 Kintex 7 FPGA電源要求

在FPGA電源設計中,不同電源軌會有不同的要求。內核電源軌通常需要在線路、負載和溫度范圍內保持更加嚴格的精度。收發器電源軌對于噪聲更加敏感,并且需要將它們的輸出保持在特定的噪聲閥值以下。還需注意的是,某些具有共模電壓的電源軌可組合在一起,并且可以用一個鐵氧體磁珠進行隔離,以實現濾波或作為一個負載開關。

1.2 外圍元件的供電

系統中除了FPGA的供電,主要外圍芯片的工作電壓同樣要考慮。表2列出了系統中主要外圍芯片的工作電壓。

表2 主要外圍芯片的工作電壓

2 電路設計

在明確了FPGA及系統的電源要求后,開始進行器件選型。一般有3種方案供選擇:低壓降線性穩壓器(LDO)、開關模式電源(SMPS)和集成模塊,它們都具有不同的優缺點[7-8]。例如,由于其簡單性和低輸出噪聲,LDO是某些較低電流FPGA電源軌的理想選擇。而LDO的缺點在于效率不高,并且在較高電流時,通過導通晶體管大量散熱。它們通常適用于功率較低、要求低噪聲的應用。當需要的電流值大于2安培,并且效率更為重要的話,設計人員可以選擇開關模式電源(SMPS)。這些器件在單相位配置中的效率可以達到90%以上,并且提供高達30 A的電流。與LDO相比,它們的設計工作量更大,并且在較輕負載時的效率不太高,不過它們更加靈活,并且在較高電流電平時的效率較高[9-11]。

本設計需要高電流輸出,采用開關模式電源設計方案,選用的電源模塊為凌力爾特的最新產品LTM4633,輸入電壓范圍為4.7 V~16 V,輸出3路電源,每個通道輸出電流可高達10 A,第1、2通道輸出電壓范圍為0.8 V~1.8 V,第3通道輸出電壓范圍為0.8 V~5.5 V[12]。該芯片集成了散熱器以增強散熱能力,通道1、通道2可以并聯,以支持高達20 A電流。

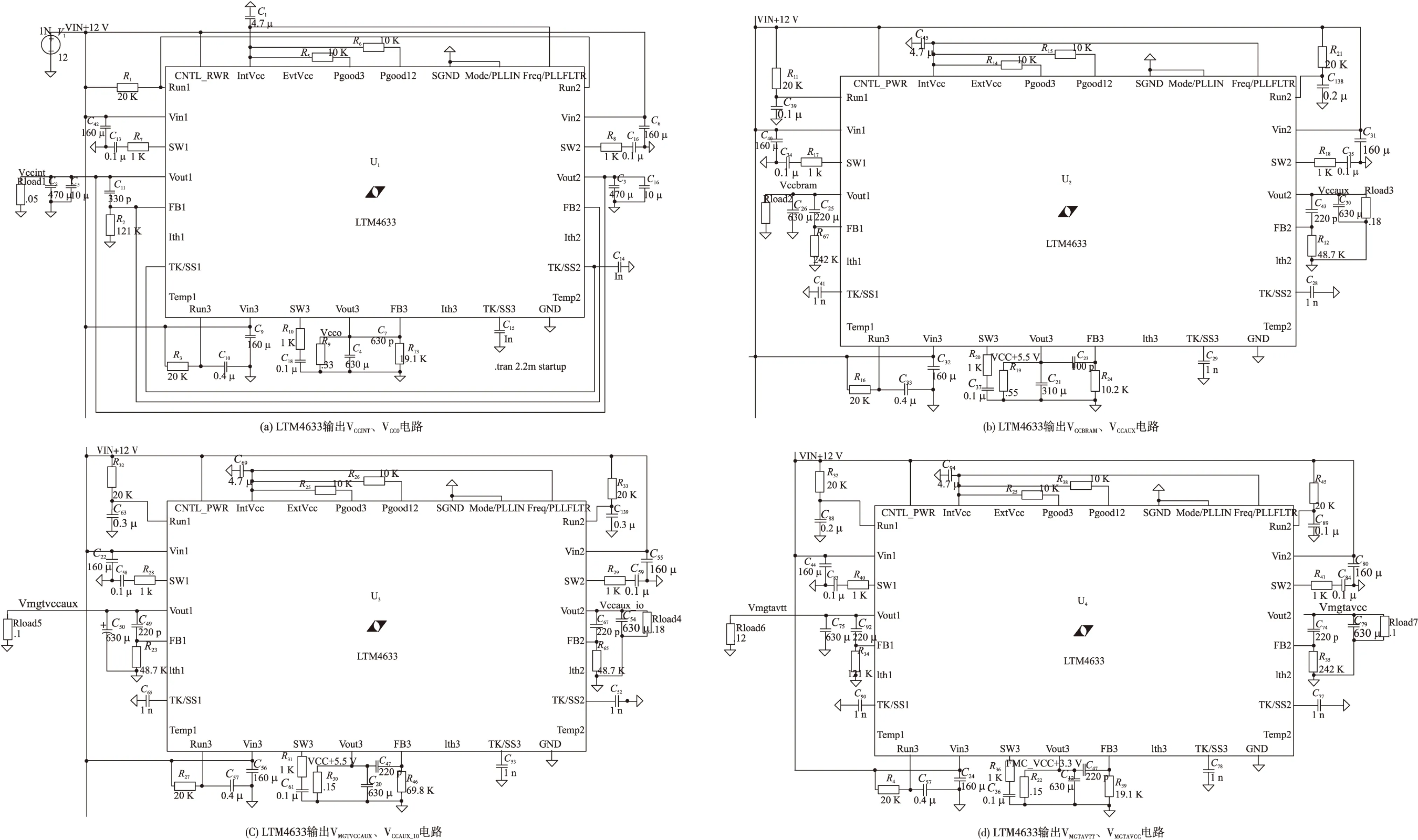

由于VCCINT需要的電流較大,需要LTM4633通道1和通道2并聯,以達到輸出電流20 A的目的,由于系統中還用到了5.5 V,1.5 V,整個系統使用了4片LTM4633為FPGA及系統其他部分提供電源。通過RUN管腳利用RC延時電路來控制其上電順序,LTM4633的輸入電壓為12 V。電路設計如圖2所示。

圖2 系統電源電路設計

2.1 RC延時電路

RC延時電路的工作原理是系統上電后利用對電容的充電來實現延時的,設計中保證電阻R不變,通過改變電容的大小來達到不同的延時時間,延時時間的計算公式:

(1)

式中:電阻R和電容C串聯,VIN是輸入電壓,VRun是電容兩端要達到的電壓來啟動RUN。表3列出了在R=20kΩ下改變電容C的大小來控制電源上電順序。

表3 在R=20 kΩ下電容C來控制電源上電順序

2.2 輸出電壓控制

電源芯片LTM4633是利用PWM調節輸出穩定電壓的,內部有一個60.4 kΩ的電阻連接著VOUT和VFB引腳,通過在VFB和地之間加一外部反饋電阻就可以控制輸出電壓的大小。當芯片無外接反饋電阻(VFB開路),默認輸出電壓0.8 V。反饋大阻RFB大小與輸出電壓VOUT的關系[10]:

(2)

(3)

表4列出了典型VOUT與RFB的對應值。

表4 典型VOUT與RFB的對應關系

為了增大輸出電流,有時需要把通道1和通道2并聯(RUN1與RUN2,VFB1與VFB2,TK/SS1與TK/SS2皆并聯),此時反饋電阻VFB的計算公式:

(4)

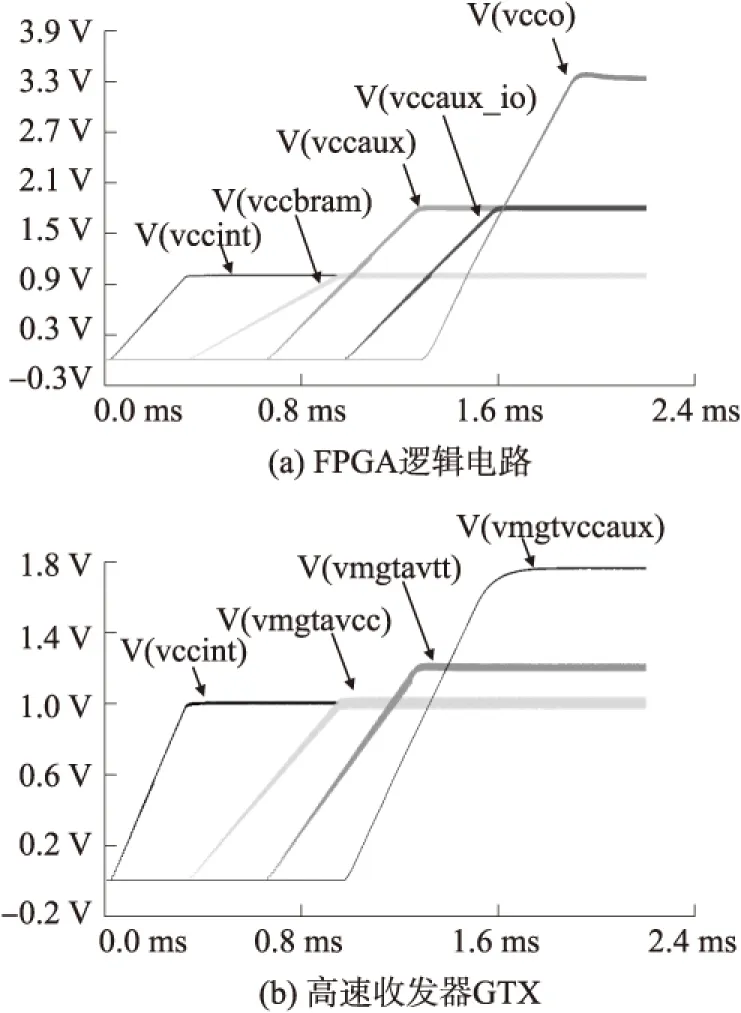

圖3 電源仿真波形

3 仿真及分析

在LTspice IV中對模擬源系統的整個電源模塊進行了設計和仿真,仿真結果如圖3所示。由圖3可以看出,不同電源電壓的加電順序滿足設計要求,電源輸出電壓紋波噪聲小。

電路的輸入為12 V直流電源,輸入濾波電容為150 μF,用于減少輸入電壓紋波;輸入旁路電容為10 μF,有效去除了輸入電壓的高頻分量。輸出濾波由470 μF和150μF電解電容及10μF電容構成。在FPGA邏輯電路上電過程中,不同電壓軌VCCINT、VCCBRAM、VCCAUX、VCCAUX_IO和VCCO的穩定供電時間依次為0.34 ms、0.96 ms、1.28 ms、1.59 ms、1.96 ms;在高速收發器上電過程中,VCCINT、VMGTAVCC、VMGTAVTT和VMGTVCCAUX的穩定供電時間依次為0.34 ms、0.96 ms、1.28 ms、1.84 ms,都與1.1節中要求的上電順序一致。

4 PCB設計

模擬源系統板的PCB設計采用16層板設計。首先進行整體布局,布局時要考慮PCB的形狀和尺寸。通常,電路板的最佳形狀為矩形,PCB尺寸過大時,印制線條長,阻抗增加,抗噪聲能力下降,成本也增加;而PCB尺寸過小時,散熱不好,且鄰近線條易受干擾[13-14]。由于設計的PCB板上有由4片LTM4633組成系統的供電單元,根據系統要求設計尺寸為233.0 mm×160.0 mm。在電源電路設計仿真成功的前提下,利用Cadence設計出PCB電路板,圖4所示為模擬源系統的PCB設計圖。

圖4 模擬源系統的PCB設計圖

圖5 示波器測試波形

5 電路板測試

在模擬源系統上電瞬間,使用Tektronix數字熒光示波器DPO5104檢測出電源波形,如圖5所示,由于示波器只能同時采集4路信號,所以FPGA邏輯電路少了VCCO的波形,其他電壓軌波形測試結果與仿真一致。但從測試波形看出,內核電壓VCCINT的輸出紋波較大,造成這一結果的原因可能有兩個:①由于內核電壓要求輸出電流高達20 A,設計時把LTM4633的兩路輸出并聯;②輸入輸出濾波應特殊設計,增加濾波電容和旁路電容來增強濾波效果。在以后電源設計中這一點需要認真考慮。

6 結論

本文詳細闡述了基于FPGA高速載荷模擬數據源系統電源的設計、仿真和實現,利用LTspice IV對電源電路進行了仿真,結果達到預想的要求。經實際電路板測試,電源各項指標均符合系統要求,滿足系統供電需求,現已在實際應用中得到驗證。

[1] 韓江濤,胡慶生,孫遠. 基于TPS54610的FPGA供電模塊設計[J]. 電子技術應用,2006(10):114-117.

[2] 胡曉軍. 基于ISL65426的FPGA電源設計[J]. 電子元器件應用,2007,9(9):14-16.

[3] Xilinx. Kintex-7FPGAsDataSheet:DC and AC Switching Characteristics Datasheet[EB/OL]. Http://www.xilinx.com/,2015.

[4] 涉谷道雄. 活學活用LTspice電路設計[M]. 北京:科學出版社,2015:97-105.

[5] 賴聯有,陳僅星,許偉堅. 基于LTspice IV的開關電源設計及仿真[J]. 通信電源技術,2010,27(1):28-29.

[6] 張伶伶,佟首峰,紀慶楠,等. 空間激光通信中智能高速模擬數據源的研制[J]. 激光與紅外,2013,43(6):611-614.

[7] 馬尼克塔拉. 精通開關電源設計[M]. 第2版. 北京:人民郵電出版社,2015:231-243.

[8] 長谷川彰. 開關穩壓電源的設計與應用[M]. 北京:科學出版社,2006:76-92.

[9] 巴索. 開關電源仿真與設計—基于SPICE[M]. 第2版. 北京:電子工業出版社,2015:108-116.

[10] 汪峰,章堅武. 基于TMS320DM6446的電源模塊設計與實現[J]. 電子器件,2010,33(3):266-270.

[11] 王俠,王進軍. 基于UC3842的三路輸出小功率開關電源設計[J]. 電子器件,2015,38(4):785-789.

[12] Linear Technology. LTM4633,Triple 10A Step-Down DC/DC uModule Regulator Datasheet[EB/OL]. Http://www.linear.com/LTM4633,2013.

[13] 吳均,王輝,周佳永. Cadence印刷電路板設計[M]. 北京:電子工業出版社,2014:166-174.

[14] 閆靜純,李濤,蘇浩航. 高速高密度PCB電源完整性分析[J]. 電子器件,2012,35(3):296-299.

Design of Power Supply for High-Speed Simulation Data Source System

WUKai1,ZHANGLei1,2*,TONGShoufeng1,2,LIXiaolong3

(1.Institute of Space Optoelectronic Technology,Changchun University of Science and Technology,Changchun 130022,China;2.Defence Key Subject Laboratory of Aero and Ground Laser Communication Technology,Changchun University of Science and Technology,Changchun 130022,China;3.School of Electronics and Information Engineering,Changchun University of Science and Technology,Changchun 130022,China)

For the satellite high-speed simulation data source system,a switching power-supply system of using three-output step-down 10 A uModule regulator LTM4633 is designed. The system can produce 11 kinds of output voltage,output current up to 20 A. The simulation software LTspiceIV is used to analyse power circuit for ensuring FPGA logic sequence and transceiver sequence to meet the design requirements,while improving the input filter and output filter to reduce the ripple noise of voltage,ripple range is 12 mV~50 mV. The experimental test is basically the same as simulation.It provides a guarantee for the entire system to work properly.

switching power-supply;LTM4633;LTspice IV;FPGA;power-up sequence

2016-04-01 修改日期:2016-05-02

C:1210

10.3969/j.issn.1005-9490.2017.02.019

TN609

A

1005-9490(2017)02-0356-05