基于字線負偏壓技術的低功耗SRAM設計

馮 李,張立軍,鄭堅斌,王 林,李有忠,張振鵬

(1.蘇州大學 江蘇 蘇州215000 2.蘇州兆芯半導體科技有限公司 江蘇蘇州215000)

基于字線負偏壓技術的低功耗SRAM設計

馮 李1,張立軍1,鄭堅斌2,王 林2,李有忠1,張振鵬1

(1.蘇州大學 江蘇 蘇州215000 2.蘇州兆芯半導體科技有限公司 江蘇蘇州215000)

隨著工藝節點的進步,SRAM中靜態功耗占整個功耗的比例越來越大,納米尺度的IC設計中,漏電流是一個關鍵問題。為了降低SRAM靜態功耗,本文提出一種字線負偏壓技術,并根據不同的工藝角,給出最合適的負偏壓大小,使得SRAM漏電流得到最大程度的降低。仿真結果表明,SMIC 40nm工藝下,和未采用字線負偏壓技術的6管SRAM存儲單元相比,該技術在典型工藝角下漏電流降低11.8%,在慢速工藝角下漏電流降低能到達29.1%。

靜態功耗;低功耗;SRAM;字線負偏壓

長期以來,國內外科研工作者一直都在致力于研究功耗更低、速度更快的SRAM,以實現更高性能的SOC。集成度的提高和電路性能的提升使得單位面積芯片的功耗不斷上升,從而使功耗成為重要的設計約束條件。近年來,智能手機、平板電腦、數碼相機等便攜式設備的流行,對SRAM的功耗提出了更高的要求,對于使用電池作為電源的產品,高功耗會大大降低電池的使用壽命并造成封裝和冷卻成本的增加。

SRAM的功耗包括動態功耗和靜態功耗。工藝每前進一個節點,MOSFET漏電流大約增加5倍。器件特征尺寸的減少,使得靜態功耗在電路總功耗中所占比例越來越大,同時也必然引起靜態泄漏電流的增加[1]。據統計,在90 nm工藝下,IC漏電流功耗大約占整個功耗的1/3,在65 nm工藝下,IC漏電流功耗已經占總功耗的一半以上。

目前,業內已提出多種降低SRAM靜態功耗的方法[2-12]。文中提出一種新的降低SRAM靜態功耗的方法:字線負偏壓技術,但是由于負偏壓的大小對MOSFET中各漏電流的影響是不同的,如何尋找最合適的負偏壓,使得SRAM靜態功耗最小,是該技術實現的關鍵。為了實現該技術,本文給出了新的字線產生電路,而且在SMIC 40 nm工藝下,給出了不同工藝角下最優的字線負偏壓。

1 字線負偏壓的原理

一個MOSFET存在多種漏電流:亞閾值漏電流,柵漏電流,PN結漏電流,柵致漏極泄漏GIDL電流,耗盡層結穿通電流。MOS管在不同狀態時的主要構成電流是不同的,當管子處于關態或等待狀態時,GIDL電流占主導地位。

所謂GIDL電流即是柵致漏極泄漏電流,是由于工藝限制產生的電流,MOSEFET柵極和漏極之間會不可避免的存在相互交疊的區域,GIDL電流就發生在柵漏交疊區這一重要區域。當漏極柵極之間電壓很大時,交疊區界面附近硅中電子在價帶和導帶之間發生帶帶隧穿,從而形成GIDL電流。隨著器件尺寸縮小,器件源極漏極以及襯底的濃度越來越大,柵氧化層越來越薄,導致GIDL電流急劇增加[13],使得GIDL電流成為器件靜態功耗中不可忽略的一部分。

亞閾值漏電流表達式如公式(1)所示,其中K1和n是實驗相關的系數,W代表柵極寬度,V代表熱電壓,室溫下是25 mV,由公式(1)可知,通過增加閾值電壓,可以達到降低亞閾值漏電流的目的。對于NMOSFET來說,可以通過在柵極加負壓的方式增加閾值電壓,而對于PMOSFET可以采用在柵極加高于VDD的電壓來降低漏電流,但是這一方法同時也會導致GIDL電流增加。

為了驗證這一理論,我們以6管SRAM的兩個傳輸管為原型做了仿真,當SRAM處于數據保持狀態時,其中一個傳輸管的漏極和源極分別接高電平和低電平,另一個傳輸管的源極和漏極都為高電平。表格1是電壓1.1 V、典型工藝角TNTP、溫度25℃下,NMOSFET柵極電壓分別為0 V和-0.1 V仿真得到的襯底電流Isub和亞閾值漏電流Is的數據。由表格1的方針數據可知,在NMOSFET柵極加-0.1 V的負壓后,若源極漏極壓差為0時,NMOSFET漏電流是增加的,因為此時NMOSFET的漏電流主要是GIDL電流,而GIDL電流隨著柵極負偏壓的增加而增加;若源極漏極壓差為VDD時,此時NMOSFET的漏電流的主要構成部分同時包括亞閾值漏電流和GIDL電流,加上柵極負偏壓之后,亞閾值漏電流降低,GIDL電流增加,但總的漏電流與原來相比有所降低。該實驗說明了字線負偏壓技術的可行性,為我們提出的字線負偏壓技術提供了理論支持。

表1 NMOSFET在柵極負偏壓下的漏電流

2 6管存儲單元漏電流分析

SRAM存儲單元有多種結構,最常見的是6T存儲單元,結構如圖1所示。6T存儲單元由兩個傳輸管AL、AR,兩個負載管PL、PR和兩個驅動管NL、NR構成,其中PL、NL和PR、NR分別組成兩個交叉耦合的反相器,首尾相連形成鎖存器,將數據保存在存儲節點Q和QB。SRAM支持三種基本的操作:數據保持、數據讀出和數據寫入[14]。在對存儲器進行讀寫操作時,兩傳輸管起到開關作用,使得存儲單元與外圍電路連接或者斷開。讀操作時,WL為高電平,兩傳輸管打開,存儲單元的存儲信息傳遞到位線BL和BLB,外圍電路通過BL和BLB讀取存儲單元的信息;寫操作時,BL和BLB連接外圍電路的輸入端,通過傳輸管,將數據寫入存儲單元。

圖1 6T存儲單元待機狀態漏電流示意圖

當6T存儲單元處于數據保持狀態時,WL為低電平,BL和BLB被預充到高電平。假設Q點存儲低電平“0”,QB點存儲高電平“1”,則6T存儲單元各個MOSFET的漏電流如圖1所示,虛線表示的是亞閾值電流,細實線表示柵極泄漏電流,粗實線表示襯底電流。襯底電流包括柵極漏電流、GIDL電流以及反向PN節漏電流,當管子處于關態時,GIDL電流是構成襯底電流的最主要部分。

由前面對NMOSFET的分析可知,對于存高電平“1”的節點QB來說,由于傳輸管源極漏極電壓均為高電平,則漏電流主要是襯底電流,傳輸管漏電流隨WL上負電壓的增加而增加。對于存低電平“0”的節點Q來說,由于傳輸管源極漏極一個為高電平一個為低電平,漏電流主要是由MOS管源極和漏極之間的壓差引起的亞閾值漏電流,隨WL上負電壓的增加而減小。但是由于柵上加負電壓,漏上加正電壓,因此電場方向從漏指向柵,在交疊區界面附近這一強電場作用下,此處硅中的能帶向上強烈彎曲,電子隧穿過禁帶從而產生GIDL隧穿電流。因此隨著WL上負電壓的增加,漏電流的走向會出現轉折點,當亞閾值漏電流占主導地位時,漏電流隨WL負電壓得增加而減小,當GIDL電流成為漏電流的主要構成部分時,則會隨WL上負電壓的增加而增加。

3 字線負偏壓技術的實現

由表1可知,MOSFET柵極加-0.1V的電壓后,亞閾值漏電流降低,GIDL電流增加,但總的漏電流是降低的。本文提出的字線負偏壓技術就是基于此結論,當SRAM存儲單元處于數據保持狀態時,WL電壓不是通常情況下的電壓0,而是給一個負偏壓Vbias,通過該技術來降低SRAM的靜態功耗。本文旨在通過降低字線電壓為負偏壓來降低亞閾值漏電流,從而降低6管SRAM的靜態功耗。但是字線電壓降低之后,當柵極電壓小于0時,并且漏極加工作電壓時,它會在交疊區下面的漏極上積累耗盡原來的N-Si,而導致漏極的強電場加在了這個耗盡區里面產生輔助陷阱的載流子復合,其過程為先從價帶到陷阱,再從陷阱到導帶的過程(如果電場夠強,則不需要陷阱也可以直接隧穿過去)。也就是傳說中經典的帶帶隧穿,即形成了GIDL電流,而GIDL電流隨柵極負電壓的增加而增加,與亞閾值漏電流形成競爭關系。

由此可見靜態功耗并不一定隨著柵極負偏壓變大而變得更小。當帶帶隧穿因素占據主要地位時,靜態功耗就會變大[15],因此必須在其中取得折中,選取合適的柵極負偏壓,只有這樣,才能最大程度減小靜態功耗。因此設置Vbias的大小、更好的權衡亞閾值漏電流和GIDL電流對漏電流的影響是字線負偏壓技術的關鍵。

圖2是6管存儲單元在1.1 V TNTP25℃時漏電流的仿真結果,其中(a)為不同WL電壓下的存儲單元漏電流,(b)為不同WL電壓下的BL漏電流,(c)為不同WL電壓下的BLB漏電流。由結果可知,存儲單元漏電流變化圖隨WL電壓變化而呈倒駝峰狀,當WL電壓取-0.1 V時,使得存儲單元漏電流最小,即靜態功耗最小。由仿真結果可知,當WL電壓取-0.1 V時,SRAM在數據保持狀態時的漏電流為62.785 pA,而WL為0 V時6管SRAM存儲單元的漏電流是71.215 pA,因此若WL電壓設為-0.1 V,則能夠使得存儲單元靜態功耗降低11.8%。同時由(b)和(c)圖可驗證GIDL電流和亞閾值電流相互競爭的關系,說明了(a)圖呈現倒駝峰的原因。由于兩傳輸管源漏極的電壓不同,所以漏電流隨柵極電壓變化的趨勢也是不同的[16]。對BLB一側的傳輸管來說,漏電流主要是亞閾值電流,由前面分析可知,亞閾值電流隨著WL負壓的增加而減小,當WL電壓持續降低時,GIDL電流成為漏電流的主要構成部分,因此BLB電壓先減小后增加,如圖2(c)所示;BL一側傳輸管的漏電流主要是GIDL電流,隨著WL負壓的增加而增加,如圖2(b)所示。

圖2 不同字線電壓下各漏電流

4 仿真結果

圖3(a)左側波形為沒有采用字線負偏壓技術的WL電壓,右側波形是采用該技術的WL電壓,即原來的WL低電平不再是傳統意義上的“0”電平,而是更低的負電壓Vbias。為了實現該技術,我們設計了新的字線產生電路,電路結構如圖3(b)所示,在原來電路的基礎上增添了新的開關電路,使得新產生的字線電壓能夠運用本文提出的字線負偏壓技術。電路原理如下:當WL_OLD為高電平“VDD”時,WL_NEW與WL_OLD的值相同,都為VDD,即存儲單元的讀寫操作與之前一致;當WL_OLD為低電平“0”時,WL_NEW與Vbias的值一致,保證當存儲單元處于數據保持狀態時,運用本文提出的字線負偏壓技術,達到降低功耗的目的。該電路使得SRAM在數據保持狀態時的字線電壓為Vbias,而在讀寫操作時的電壓為VDD。

圖3 帶負偏壓的字線產生電路

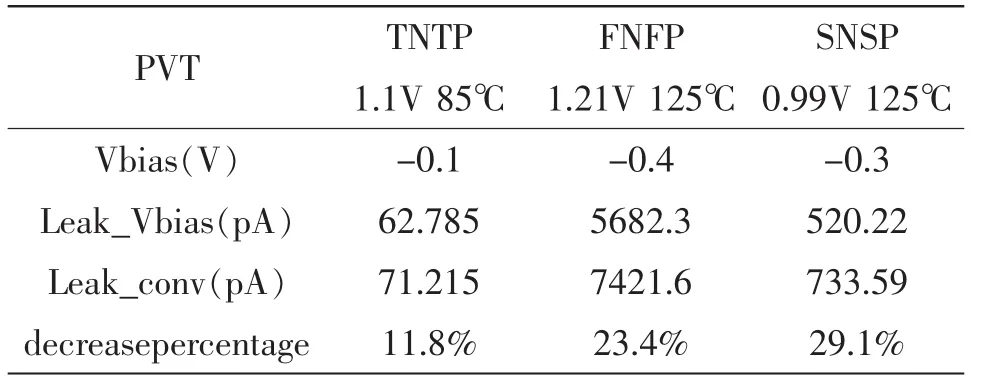

最優字線負偏壓的大小不僅與工藝有關,還會因工藝角(P)、供電電壓(V)、溫度(T)的不同而呈現不同的結果,因此我們對不同PVT下的6管存儲單元在數據保持狀態時的漏電流做了仿真[17]。表2給出了采用SMIC 40nm工藝且不同PVT情況下的最優字線負偏壓,并且給出了采用該技術前后6管SRAM存儲單元的靜態功耗對比。由結果可知,采用了字線負偏壓技術之后,在典型工藝角TNTP85℃下,存儲單元的靜態功耗降低了11.8%;在快速工藝角 FNFP125℃下,存儲單元的靜態功耗降低了23.4%;在慢速工藝角SNSP125℃下,存儲單元的靜態功耗降低了29.1%。

表2 不同PVT下的最優字線負偏壓

5 結 論

基于SMIC 40 nm的工藝,本文提出了字線負偏壓技術,該技術通過降低6管SRAM存儲單元在數據保持狀態時的字線電壓,達到降低漏電流的目的,從而實現降低存儲單元的靜態功耗。并且考慮到不同工藝、電壓、溫度情況下的最優字線負偏壓值是不同的,因此我們對6管SRAM存儲單元在不同PVT下的漏電流做了仿真,給出了不同PVT下的最優負偏壓值。通過使用該技術,存儲單元在典型工藝角下漏電流降低 11.8%,快速工藝角下漏電流降低23.4%,慢速工藝角下漏電流降低29.1%。

[1]Eid SherifT,WhatelyMorgan,KrishnegowdaSandeep-A microcontroller-based PVT control system for a 65nm 72Mb synchronous SRAM [C]//2010 IEEE International Solid-State Circuits Conference-San Francisco,CA,United states:[s.n.],2010:184-185-

[2]Venkatareddy A,Sithara R,Nithin Kumar Y B,et al.Characterization of a Novel Low Leakage Power and Area Efficient 7T SRAM Cell[C]//2016 29th International Conference on VLSI Design and 2016 15th International Conference on Embedded Systems.Kolkata,India:IEEE Computer Society, 2016:202-206.

[3]Anand P R,Chandra Sekhar P.Reduce Leakage Currents in Low Power SRAM Cell Structures[C]// 2011 IEEE 9th International Symposium on Parallel and Distributed Processing with Applications Workshops.Los Alamitos,CA,USA:IEEE Computer Society,2011:33-38.

[4]Corsonello P,Fstaci F,Perri S.Low-Leakage SRAM Wordline Drivers for the 28-nm UTBB FDSOI Technology[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2015,23(12):3133-3137.

[5]Amalraj K,Sathishkumar P,Vigneshraja K,et al. Nano scaled low power leakage st-based SRAM[C]// Proceedings of the 2012 International Conference on Emerging Trends in Electrical Engineering and Energy Management.Piscataway, NJ, USA: IEEE,2012:312-316.

[6]Mohammad B.Low leakage power SRAM cell for embedded memory[C]//2011 International Conference on Innovations in Information Technology. Piscataway,NJ,USA:IEEE,2011:367-370.

[7]Upadhyay P,Ghosh S,Mandal D,et al.Low static and dynamic power MTCMOS based 12T SRAM cell for high speed memory system[C]//2014 11th International Joint Conference on Computer Science and Software Engineering.Piscataway,NJ,USA:IEEE,2014:212-217.

[8]Sharma A,Lata K.Low-leakage and processvariation-tolerant write-read disturb-free 9T SRA cell using CMOS and FinFETs[C]//2016 17th International Symposium on Quality Electronic Design. Piscataway,NJ,USA:IEEE,2016:205-210.

[9]Venkatareddy A,Sithara R,et al.Characterization of a Novel Low Leakage Power and Area Efficient 7T SRAM Cell [C]//2016 29th International Conference on VLSI Design and 2016 15th International Conference on Embedded Systems. Los Alamitos,CA,USA:IEEE Computer Society,2016:202-206.

[10]Chua-Chin Wang,Deng-Shain Wang,Chiang-Hsiang Liao.A leakage compensation design for low supply voltage SRAM[J].IEEE Transactions on Very Large Scale Integration (VLSI)Systems,2016,24(5):1761-1769.

[11]Nair P,Eratne S,John E.A quasi-power-gated low-leakage stable SRAM cell[C]//2010 53rd IEEE International Midwest Symposium on Circuits and Systems.Piscataway,NJ,USA:IEEE,2010: 761-764.

[12]Delgado-Frias J G,Zhe Zhang,Turi M A.Low power SRAM cell design for FinFET and CNTFET technologies[C]//2010 International Conference on Green Computing.Piscataway,NJ,USA:IEEE,2010:547-553.

[13]陳海峰.超深亞微米CMOS器件GIDL電流及其可靠性研究[D].西安:西安電子科技大學,2008:2.

[14]Jan M Rabaey,AnanthaChandrakasan數字集成電路—電路、系統與設計[M].周潤德,等譯.北京:電子工業出版社,2010:484-490.

[15]陳海峰.超深亞微米CMOS器件GIDL電流及其可靠性研究[D].西安:西安電子科技大學,2008.

[16]崔巖.采用T型電路參數法對現場電流互感器測量的研究[J].陜西電力,2011(9):63-66.

[17]朱成龍,張杰,何康康,等.彎管成型截面畸變有限元數值仿真分析[J].火箭推進,2015(5):77.

Design of low power SRAM based on a negative word line technique

FENG Li1,ZHANG Li-jun1,ZHENG Jian-bin2,WANG Lin2,LI You-zhong1,ZHANG Zhen-peng1

(1.SooChowUniversity,Suzhou215000,China;2.MegacoresTechnolgyCompanyLimited,Suzhou215000,China)

With the development of semiconductor manufacturing technology,SRAM static power consumption in the proportion of the total power consumption is more and more serious.Leakage is a key issue in the nanoscale IC design.In order to reduce the static power consumption of SRAM,this paper proposes a negative word line technique,and gives the most appropriate negative bias voltage under different corners,which can lead to a maximum decrease of cell leakage.The simulation results show that under the SMIC 40 nm process,the technology can reduce 11.8%in the typical corner,and 29.1%in SNSP corner,comparing 6T-SRAM without this technology.

static power consumption;low power;SRAM;negative word line

TN432

:A

:1674-6236(2017)08-0115-04

2016-06-26稿件編號:201606200

國家自然科學基金項目(61272105;61076102)

馮 李(1992—),女,安徽宿州人,碩士。研究方向:低功耗SRAM。