基于FPGA的簡易手持式示波器設(shè)計

孫緒福

摘 要 本文設(shè)計的簡易手持式示波器是基于FPGA應(yīng)用技術(shù),以PCF8951為數(shù)據(jù)采集前端。通過內(nèi)建RAM進(jìn)行對采集數(shù)據(jù)的存儲以及波形的顯示。利用有限狀態(tài)機(jī)實(shí)現(xiàn)對不同狀態(tài)之間的轉(zhuǎn)換,最后顯示在ST7735液晶顯示屏上。本設(shè)計最大的特點(diǎn)是所用器件都為低功耗、低成本、小體積的器件,能夠?qū)崿F(xiàn)手持式設(shè)計。通過在開發(fā)板上的測試結(jié)果表明,該設(shè)計能夠?qū)崿F(xiàn)示波器的基本功能,且大大降低成本及減少體積。

【關(guān)鍵詞】FPGA 示波器 PCF8591 有限狀態(tài)機(jī)

示波器是一種應(yīng)用十分廣泛的電子測量儀器,能夠方便地測量各種不同的波形。但是傳統(tǒng)的模擬示波器具有體積大、成本高、攜帶不方便等缺點(diǎn),因而使得許多電子實(shí)驗(yàn)限制在了實(shí)驗(yàn)室中進(jìn)行。由于這種局限性推動了示波器朝著微型化、簡單化、廉價化的方向發(fā)展。對于精度要求不是特別高的情況下,生產(chǎn)出一款便攜手持式的低成本數(shù)字示波器將會有很大的需求和市場價值。由此本文提出一種簡單手持式示波器設(shè)計方案,基于FPGA應(yīng)用技術(shù),實(shí)現(xiàn)了對信號的實(shí)時顯示,以及具有調(diào)節(jié)掃描速度和垂直靈敏度的功能。本設(shè)計方案均采用體積小、成本低的元器件進(jìn)行設(shè)計,在保證一定精度的前提下大大減小體積以及降低成本。在簡易的電子實(shí)驗(yàn)中此設(shè)計能夠發(fā)揮重要的作用。

1 系統(tǒng)設(shè)計

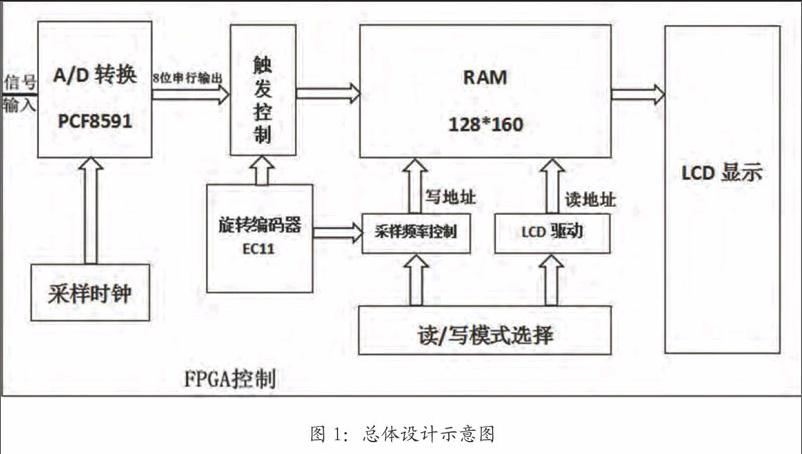

數(shù)字示波器是由取樣存儲、系統(tǒng)控制和讀出顯示三大部分組成,它們之間通過數(shù)據(jù)總線、地址總線、和控制總線相互聯(lián)系和交換信息,以完成各種測量功本次設(shè)計采用萊迪思LCMX02-4000HC芯片,通過將外部輸入模擬信號經(jīng)過PCF8591芯片進(jìn)行A/D轉(zhuǎn)換,將轉(zhuǎn)換后的數(shù)據(jù)根據(jù)旋轉(zhuǎn)編碼器EC11設(shè)定的觸發(fā)條件以及采樣頻率,篩選出符合條件的數(shù)據(jù),之后將數(shù)據(jù)送入RAM中保存。當(dāng)RAM存滿后,狀態(tài)切換至讀RAM狀態(tài),通過對ST7735顯示屏的初始化以及對RAM中數(shù)據(jù)的適當(dāng)操作后,將信息呈現(xiàn)至屏幕上,以實(shí)現(xiàn)示波器的基本功能。此外,還設(shè)置了復(fù)位按鍵以實(shí)現(xiàn)示波器的復(fù)位功能。本次設(shè)計主要包括FPGA邏輯控制模塊、A\D數(shù)模轉(zhuǎn)換模塊、觸發(fā)條件及采樣頻率調(diào)節(jié)模塊、RAM的讀寫控制模塊、液晶顯示模塊圖1所示,為本次設(shè)計的總體示意圖。

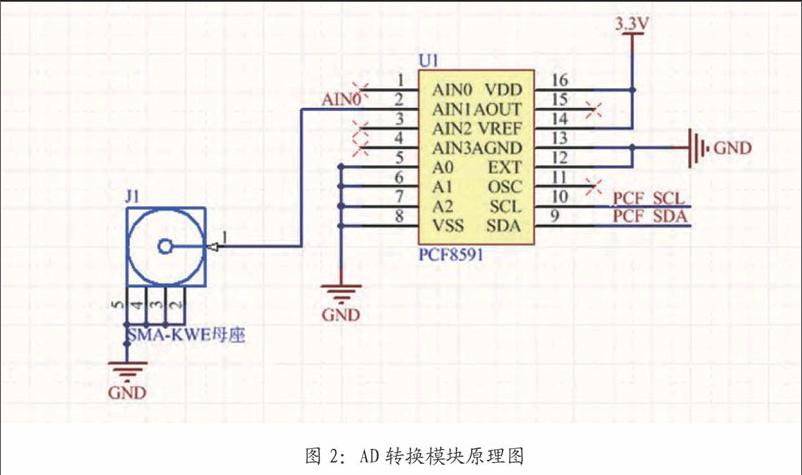

1.1 A/D轉(zhuǎn)換模塊

由于本設(shè)計旨在設(shè)計低成本、便攜式示波器,對轉(zhuǎn)換速度、轉(zhuǎn)換精度要求相對降低,故采用8位串行輸出A/D轉(zhuǎn)換芯片進(jìn)行A/D轉(zhuǎn)換模塊。綜合對各A/D轉(zhuǎn)換芯片的比較后,本設(shè)計采用恩智浦半導(dǎo)體公司生產(chǎn)的具有8位CMOS數(shù)模轉(zhuǎn)換芯片PCF8591以實(shí)現(xiàn)對輸入信號的采樣。該芯片們具有單獨(dú)供電、低功耗的特點(diǎn),在2.5V~6V的工作電壓內(nèi),采樣速率取決于I2C總線的速度,在標(biāo)準(zhǔn)速度下可達(dá)100kbps,能夠?qū)崿F(xiàn)本設(shè)計對采樣速度的要求。此外,它同時具有4路模擬輸入端及1路輸出端,可編程為單端或差分輸入,3個地址引腳A0、A1和A2用于編輯硬件的地址,允許同時將多個器件接至總線本設(shè)計中采用超小型SOP-16貼片式封裝以減少器件所用面積,有利于實(shí)現(xiàn)便攜式攜帶的要求。綜合以上特點(diǎn),該芯片適用于本次關(guān)于簡易手持式示波器的設(shè)計,能滿足各項(xiàng)指標(biāo)要求。A/D轉(zhuǎn)換模塊程序的編寫,主要采用設(shè)計有限狀態(tài)機(jī)(FSM),通過對不同狀態(tài)的計數(shù),實(shí)現(xiàn)在初始化、開始、寫指令、讀數(shù)據(jù)、結(jié)束狀態(tài)之間的轉(zhuǎn)換。圖2所示為A/D轉(zhuǎn)換模塊的原理圖,其中模擬信號的輸入,通過連接母座以送入芯片模擬輸入端。

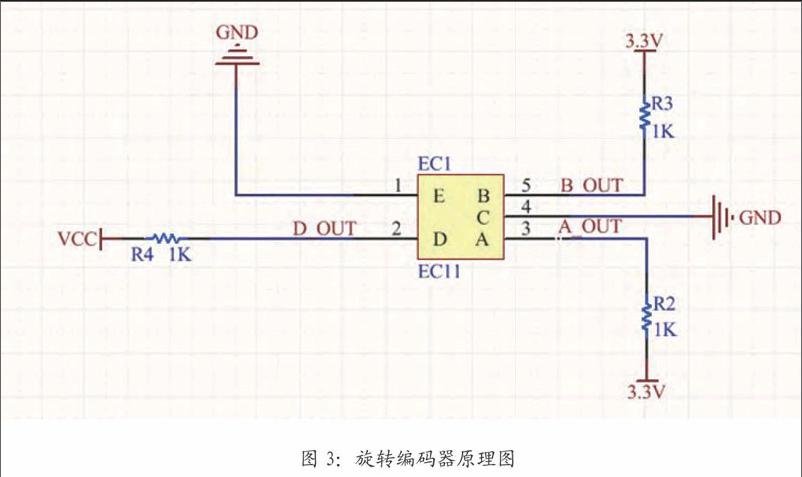

1.2 觸發(fā)條件及頻率調(diào)節(jié)模塊

考慮到輸入信號頻率及幅值的不同,在本設(shè)計中可以實(shí)現(xiàn)對采樣頻率以及觸發(fā)條件的改變。鑒于旋轉(zhuǎn)操作的簡易性,本設(shè)計采用ALPS常用金屬軸編碼器EC11實(shí)現(xiàn)對采集頻率以及觸發(fā)幅值的調(diào)節(jié),通過對編碼器的左右旋轉(zhuǎn)實(shí)現(xiàn)增大與縮小的功能。EC11編碼器屬于小型高精度旋轉(zhuǎn)式編碼器,15脈沖30定位,20脈沖20定位的高分辨率,適用于微小電流回路的電子設(shè)備其上還帶有0.5mm按壓開關(guān),在本設(shè)計中用于切換采樣頻率調(diào)節(jié)模式和觸發(fā)調(diào)節(jié)模式。

頻率調(diào)節(jié)通過旋轉(zhuǎn)編碼器的左右旋轉(zhuǎn),改變采樣計數(shù)值的大小,以實(shí)現(xiàn)頻率的改變。以計數(shù)標(biāo)志cnt_sample為例,初始設(shè)定cnt_sample為5,即每5個采樣點(diǎn)放進(jìn)一次RAM當(dāng)中用以之后顯示。當(dāng)左旋一次后,設(shè)定cnt_sample自加1,則每6個采樣點(diǎn)放進(jìn)RAM當(dāng)中,右旋反之,由此實(shí)現(xiàn)了示波器采樣頻率的增大。

觸發(fā)幅值調(diào)節(jié)通過旋轉(zhuǎn)編碼器的左右旋轉(zhuǎn),改變觸發(fā)邊界條件的大小,從而實(shí)現(xiàn)對不同信號觸發(fā)條件的改變。以幅值為1.5V的正弦波為例,若觸發(fā)條件設(shè)置為2V,則始終無法達(dá)到觸發(fā)條件,可以通過旋轉(zhuǎn)編碼器改變觸發(fā)條件,以獲取完整的信號波形。同時為避免始終無波形顯示的情況,本設(shè)計中通過設(shè)定計數(shù)環(huán)節(jié),若連續(xù)16次未有滿足觸發(fā)條件的信號,則設(shè)置為已滿足觸發(fā)條件,實(shí)現(xiàn)對波形的顯示。此外,觸發(fā)條件的設(shè)置,還具有穩(wěn)定波形的作用,由于A/D轉(zhuǎn)換時時進(jìn)行,若要保證波形的穩(wěn)定以及顯示時無視覺殘留,可以通過設(shè)定合適的觸發(fā)條件,當(dāng)滿足觸發(fā)條件后,才將采樣數(shù)據(jù)保存至對應(yīng)RAM中,以達(dá)到穩(wěn)定波形的作用。圖3所示為本次設(shè)計中旋轉(zhuǎn)編碼器的原理圖。

1.3 RAM的讀寫控制模塊

由于A/D采集信號的保存以及LCD顯示數(shù)據(jù)的讀取共用同一個RAM,我們通過設(shè)立不同的標(biāo)志位,來確定進(jìn)行A/D轉(zhuǎn)換數(shù)據(jù)存RAM操作還是將RAM中數(shù)據(jù)輸出顯示至液晶屏操作。

當(dāng)進(jìn)行存RAM操作時,信號經(jīng)過A/D轉(zhuǎn)換輸出8位二進(jìn)制數(shù)據(jù)后,由于本此設(shè)計所采用的LCD顯示為128*160RGB三色顯示,數(shù)據(jù)存儲深度為128,我們可以將經(jīng)A/D轉(zhuǎn)換后的8位二進(jìn)制數(shù)左移一位,使采集數(shù)據(jù)范圍為0 ~127,恰能滿足數(shù)據(jù)存儲要求。當(dāng)滿足觸發(fā)條件后,根據(jù)采樣條件,將符合條件的數(shù)據(jù)讀入RAM中直至存滿160個數(shù)據(jù)。此時RAM中儲存的就是采集到的信號。

當(dāng)進(jìn)行讀RAM操作時,為了起到顯示波形的效果,我們將RAM中除了采集到的160個數(shù)據(jù)外全部設(shè)置為黑色顯示,將信號設(shè)置為白色顯示,由此我們可以實(shí)現(xiàn)在顯示屏上看到白色的波形。圖4所示,為本次設(shè)計中RAM中數(shù)據(jù)部分示意。

1.4 LCD顯示模塊

本次設(shè)計采用ST7735液晶屏,具有132(H)*RGB*162(V)位大小的RAM,在本次設(shè)計中,數(shù)據(jù)保存至128*160,剩余的部分作為邊緣顯示,以更好地實(shí)現(xiàn)示波器的顯示效果。該顯示屏具有紅、綠、藍(lán)三色,可以根據(jù)對這三種色彩的16位二進(jìn)制數(shù)據(jù)進(jìn)行調(diào)配實(shí)現(xiàn)其它色彩的顯示,例如本次設(shè)計中白色16hffff以及黑色16h0000為了達(dá)到更好的顯示效果,本設(shè)計采用豎屏顯示。由數(shù)據(jù)手冊,我們可以得到驅(qū)動該器件的指令,利用有限狀態(tài)機(jī)實(shí)現(xiàn)對命令的寫入以及對RAM中數(shù)據(jù)的讀入。當(dāng)RAM中數(shù)據(jù)顯示結(jié)束后,狀態(tài)切換至存RAM操作。圖5所示為本次設(shè)計中LCD模塊顯示原理圖。

2 程序設(shè)計

本次程序采用Verilog語言進(jìn)行編輯使用Lattice diamond設(shè)計軟件進(jìn)行綜合與調(diào)試。頂層模塊設(shè)計主要包括A/D轉(zhuǎn)換模塊、讀寫選擇模塊、采樣頻率調(diào)節(jié)模塊、觸發(fā)條件設(shè)置模塊、LCD顯示模塊以及LCD讀寫RAM模塊。關(guān)于輸入輸出端口及頂層模塊和各模塊的關(guān)系描述如下:

module Oscilloscope //示波器模塊

(

input clk, //時鐘輸入

input rst, //復(fù)位按鍵

input encode_left, //旋轉(zhuǎn)編碼器左旋

input encoder_right, //旋轉(zhuǎn)編碼器右旋

input encoder_key, //按下旋轉(zhuǎn)編碼器

inout ad_sda, //PCF8591數(shù)據(jù)端

output ad_scl, //PCF8591時鐘端

output lcd_rst, //LCD復(fù)位端

output lcd_bl, //LCD背光設(shè)置端

output lcd_dc, //LCD的D/C端

output lcd_clk, // LCD顯示SPI時鐘

output lcd_data // RAM讀寫數(shù)據(jù)端口

);

wire sample_en; //取樣使能信號

wire sample_finish; //取樣完成標(biāo)志

wire display_en; //顯示使能信號

wire display_finish; //顯示完成標(biāo)志

wire ad_finish; //ad轉(zhuǎn)換完成標(biāo)志

wire [7:0] ad_data; //8位串行數(shù)據(jù)

wire [7:0] trigger; //觸發(fā)條件

wire wr_clock; //RAM寫時鐘

wire [7:0] wr_add; //RAM寫地址

wire [131:0] ram_ad; //RAM中寫對應(yīng)AD轉(zhuǎn)換數(shù)據(jù)

wire re_clock; //RAM讀時鐘

wire [7:0] re_add; //RAM讀地址

wire [131:0] ram_lcd; //RAM中LCD讀數(shù)據(jù)

Mode_choosemode_choose //選擇進(jìn)行顯示/讀數(shù)據(jù)模塊

(

.clk (clk ), //系統(tǒng)時鐘

.rst (rst ), //復(fù)位按鍵

.display_finish (display_finish ), //顯示完成標(biāo)志

.sample_finish (sample_finish ), //采樣完成標(biāo)志

.sample_en (sample_en ), //采樣使能標(biāo)志

.display_en (display_en ) //顯示使能標(biāo)志

);

AD_conversionad_conversion //A/D轉(zhuǎn)換模塊

(

.clk (clk ), //系統(tǒng)時鐘

.rst (rst ), //復(fù)位按鍵

.ad_scl (ad_scl ), //AD轉(zhuǎn)換控制時鐘

.ad_sda (ad_sda ), //AD轉(zhuǎn)換數(shù)據(jù)端

.ad_finish (ad_finish ), //AD轉(zhuǎn)換完成標(biāo)志

.ad_data (ad_data ) //數(shù)據(jù)存儲寄存器

);

Parameter_setparameter_set //參數(shù)設(shè)置模塊

(

.clk (clk ), // 系統(tǒng)時鐘

.rst (rst ), //復(fù)位按鍵

.encode_left (encode_left ), // 左旋標(biāo)志

.encode_right (encode_right ), // 右旋標(biāo)志

.encode_key (encode_key ), // 按鍵標(biāo)志

.trigger (trigger ), //觸發(fā)條件設(shè)置

.ad_finish (ad_finish ) //AD轉(zhuǎn)換完成標(biāo)志

);

AD_SampleAD_sample //AD存RAM模塊

(

.clk (clk ), // 系統(tǒng)時鐘

.rst (rst ), //按鍵復(fù)位

.ad_finish (ad_finish ), //AD轉(zhuǎn)換完成標(biāo)志

.ad_data (ad_data ), //AD轉(zhuǎn)換后數(shù)據(jù)

.trigger (trigger ), //觸發(fā)條件

.sample_en (sample_en ), //采樣使能標(biāo)志

.sample_finish (sample_finish ), //采樣完成標(biāo)志

.wr_clock (wr_clock ), //RAM寫時鐘

.wr_add (wr_add ), //RAM寫地址

.ram_data (ram_data ) //RAM中數(shù)據(jù)

);

LCD_DisplayLCD_display //LCD顯示模塊

(

.clk (clk ), //系統(tǒng)時鐘

.rst (rst ), //按鍵復(fù)位

.trigger (trigger ), //觸發(fā)條件

.display_en (display_en ), //顯示使能標(biāo)志

.display_finish (display_finish ), //顯示完成標(biāo)志

.re_clock (re_clock ), //RAM讀時鐘

.re_add (re_add ), //RAM讀地址

.ram_data (ram_data ), //RAM中數(shù)據(jù)

.lcd_rst (lcd_rst ), //LCD復(fù)位

.lcd_bl (lcd_bl ), //LCD背光控制

.lcd_dc (lcd_dc ), //LCD的DC端

.lcd_clk (lcd_clk ), // LCD傳輸SPI的時鐘

.lcd_data (lcd_data ) // LCD數(shù)據(jù)端

);

endmodule

采用Verilog語言進(jìn)行電路設(shè)計,能夠在每個抽象層次的描述上對設(shè)計進(jìn)行仿真設(shè)計,及時發(fā)現(xiàn)可能存在的設(shè)計錯誤,能夠有效縮短設(shè)計周期,并保證設(shè)計過程中的正確性,以此實(shí)現(xiàn)我們最終的設(shè)計。

3 設(shè)計驗(yàn)證

通過在開發(fā)板上的測試結(jié)果表明,雖然LCD液晶顯示模塊的分辨率較低,但依然可以實(shí)現(xiàn)示波器的基本功能,特別是對于頻率不太高的模擬信號,能夠在屏幕上清晰地顯示波形對應(yīng)的像素點(diǎn)。此外,通過調(diào)節(jié)旋轉(zhuǎn)編碼器,也實(shí)現(xiàn)了預(yù)定的切換模式、調(diào)節(jié)采樣頻率及改變觸發(fā)條件的功能。通過Lattice diamond自帶的仿真軟件測試得出本次設(shè)計運(yùn)算速度較快,頻率顯示較為準(zhǔn)確,能夠?qū)崿F(xiàn)數(shù)據(jù)的快速讀取。本設(shè)計方案具有簡單易操作的特點(diǎn),此外還具有體積小、功耗低、成本低的優(yōu)點(diǎn)。由于FPGA并行執(zhí)行的特點(diǎn),大大提高了系統(tǒng)的性能,能夠?qū)崿F(xiàn)手持式設(shè)計同時能滿足基礎(chǔ)電子實(shí)驗(yàn)的需求。此外,本次設(shè)計的示波器綜合成本相對于市場銷售的手持式示波器大大降低,便于推廣,有較大的市場價值和實(shí)用價值。

4 結(jié)論

本設(shè)計利用FPGA、A/D轉(zhuǎn)換芯片、LCD液晶顯示器、旋轉(zhuǎn)編碼器實(shí)現(xiàn)了對輸入模擬信號的采樣、存儲以及波形的顯示功能,并增添了調(diào)節(jié)采樣頻率及觸發(fā)條件的功能,實(shí)現(xiàn)了對簡易手持式示波器的設(shè)計。通過驗(yàn)證得出本設(shè)計具有較快的數(shù)據(jù)傳輸速度及較高的精度,能夠滿足日常的電子相關(guān)測量需求。本設(shè)計的低成本與小型化能夠?qū)崿F(xiàn)廉價手持式示波器的廣泛化應(yīng)用。此外,也可通過使用12位、16位并行A/D轉(zhuǎn)換芯片以提高本設(shè)計的精度與速度,利用更高分辨率的LCD顯示以實(shí)現(xiàn)對本設(shè)計的更高要求。

參考文獻(xiàn)

[1]朱英明.數(shù)字示波器原理與測試分析[J].測試技術(shù),2007(Z1).

[2]雷貴,胡福云.基于FPGA的虛擬簡易數(shù)字存儲示波器設(shè)計[J].現(xiàn)代商貿(mào)工業(yè),2011(08).

[3]CoolborXie,PCF8591芯片手冊,Philips公司.

[4]ALPS公司,旋轉(zhuǎn)編碼器EC11數(shù)據(jù)手冊,ALPS公司.

[5]孫盛坤,丁昊等.基于FPGA和TFT彩屏液晶的便攜示波器設(shè)計[J].現(xiàn)代電子技術(shù),2011.

[6]夏宇聞.Verilog數(shù)字系統(tǒng)設(shè)計教程[M].北京航天航空大學(xué)出版社,2008.