AXI4總線的USB2.0設備控制器IP核設計*

韓進,秦宏超,劉鍇

(1.山東科技大學 信息科學與工程學院,青島 266590; 2.山東高云半導體科技有限公司)

?

AXI4總線的USB2.0設備控制器IP核設計*

韓進1,秦宏超1,劉鍇2

(1.山東科技大學 信息科學與工程學院,青島 266590; 2.山東高云半導體科技有限公司)

本設計依托星核計劃——山東國產IP軟核平臺,基于最新片上總線AMBA4.0協議,使用VerilogHDL語言完成了主要由AXI4總線接口、ULPI模式控制、封包、解包和協議處理等模塊組成的USB2.0設備控制器的IP核設計,通過綜合驗證證明了設計的正確性,并有效降低了FPGA邏輯資源占用率。可以根據實際應用要求將設計的USB2.0控制器 IP核直接移植到FPGA內部,實現USB數據傳輸協議,省去了USB協議芯片,節省了產品開發成本,并且有效縮短了產品設計周期。

USB2.0;IP核;AXI4總線;VerilogHDL

引 言

Philips、Cypress等公司推出的各類USB芯片得到了廣泛應用,但國內并沒有廠商推出相關產品,特別是兼容USB2.0協議的接口芯片,幾乎完全依賴國外產品[1-2]。目前國內對USB的相關研究更多的是利用國外的控制芯片進行產品開發,因此設計擁有自主知識產權的USB2.0 IP核顯得尤為重要。本設計依托星核計劃——山東國產IP軟核平臺,基于最新片上總線AMBA4.0協議,使用VerilogHDL硬件描述語言完成了USB2.0設備控制器的IP核設計及驗證。

1 整體系統設計

圖1是AXI4USB2.0設備控制器的整體架構圖。該IP主要有寄存器管理模塊、AXI總線接口模塊、工作模式控制模塊、數據包處理模塊、協議處理模塊和端點緩沖區模塊組成。設計采用外接符合ULPI協議的PHY芯片。寄存器管理模塊定義了USB設備控制器IP所需要的所有寄存器,用于管理整個IP的各種功能;AXI4總線接口模塊實現IP與AXI4-Lite、AXI4-Stream總線的接口;基于ULPI的工作模式控制模塊主要是檢測USB總線狀態,根據USB總線狀態來控制整個IP核的工作狀態;數據包處理模塊和外接的PHY相連,用于實現USB物理層;協議處理模塊主要功能是處理各種不同的傳輸事務,用于實現USB協議層;端點緩沖區模塊主要用于緩存協議處理模塊和AXI4總線之間需要交互的所有數據。

圖1 整體架構

2 模塊設計

2.1 AXI4總線接口模塊

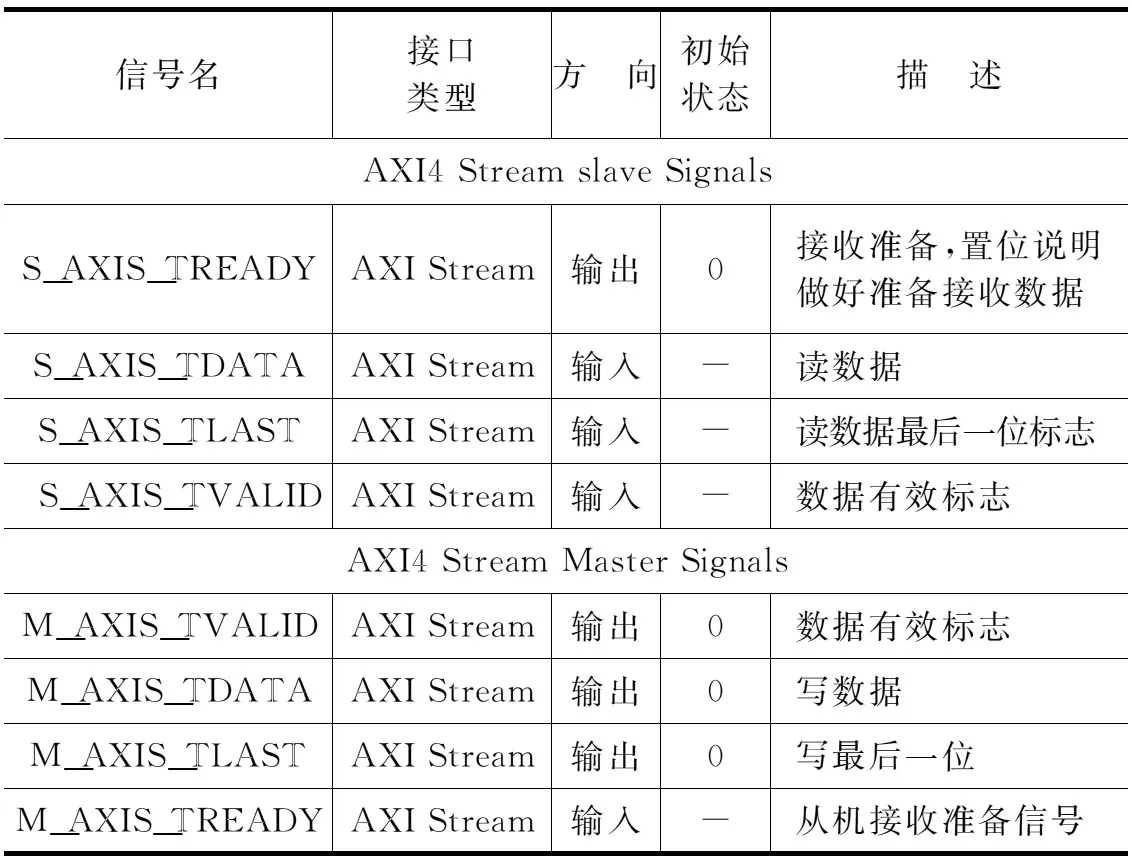

AXI4總線接口模塊實現IP與AXI4-Lite、AXI4-Stream總線的接口,AXI4-Lite接口主要用于實現AXI4總線主設備對USB設備控制器寄存器的讀寫,AXI4-Stream接口用于AXI4主機完成對USB數據緩沖區的讀寫[3]。表1是AXI4-Stream I2C主機總線的端口信號及描述。

表1 AXI4-Stream I2C主機總線端口信號描述

AXI4-Lite總線的信號可以參考ARM公司的相關標準。

AXI4 Streamslave 接口具體實現如下:

assignaxis_wr_en=S_AXIS_TVALID;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_wr_addr<=13'b0; //復位清空寫地址信號

else if(!S_AXIS_TVALID)

axis_wr_addr[12:0] <=axis_s_addr[12:0];

else

axis_wr_addr<=axis_wr_addr + 1'b1;

//數據有效寫入下一個數據地址

assign axis_wr_data=S_AXIS_TDATA;

//總線寫入主機讀數據

AXI4 Stream Master接口具體實現:

regaxis_m_en_reg;

wireaxis_m_en_ris_edge;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_m_en_reg<=0;

else

axis_m_en_reg<=axis_m_en;

assignaxis_m_en_ris_edge = axis_m_en& (!axis_m_en_reg);

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_rd_addr<=13'b0;

else if(!axis_rd_en)

axis_rd_addr[12:0] <=axis_m_addr[12:0];

else

axis_rd_addr<=axis_m_addr + 1'b1;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

axis_rd_en<=1'b0;

else if(axis_m_en_ris_edge)

axis_rd_en<=1'b1; //上升沿總線讀數據使能

else if(axis_m_sendov)

axis_rd_en<=1'b0;

always@(posedge S_AXI_ACLK)

if(!S_AXI_ARESETN)

data_send_count<=11'b0;

else if(axis_rd_en)

data_send_count<=data_send_count+1'b1;

//數據有效主機發送數據量加1

else

data_send_count<=11'b0;

assignaxis_m_sendov=(data_count==data_send_count) ? 1:0;

assign M_AXIS_TDATA=axis_rd_data;

assign M_AXIS_TVALID=axis_rd_en;

2.2 ULPI模式控制模塊

基于ULPI的模式控制模塊主要是檢測USB總線狀態,根據USB總線狀態來控制整個IP核的工作狀態,完成復位檢測、設備掛起與恢復、高速握手等工作。模式控制模塊有PHY_CLK和S_AXI_ACLK這兩個時鐘,其中非掛起狀態檢測RX_CMD的電路工作在PHY_CLK,其他電路基本都工作在來自AXI4總線的系統時鐘域。模式控制模塊采用狀態機設計,如圖2所示。

圖2 模式控制模塊狀態圖

圖2中部分狀態和跳轉沒有畫出。除了與掛起相關的狀態,其他狀態只要是vbus無效(設備與HOST斷開連接),狀態機都會回到IDLE狀態。

2.3 協議處理模塊

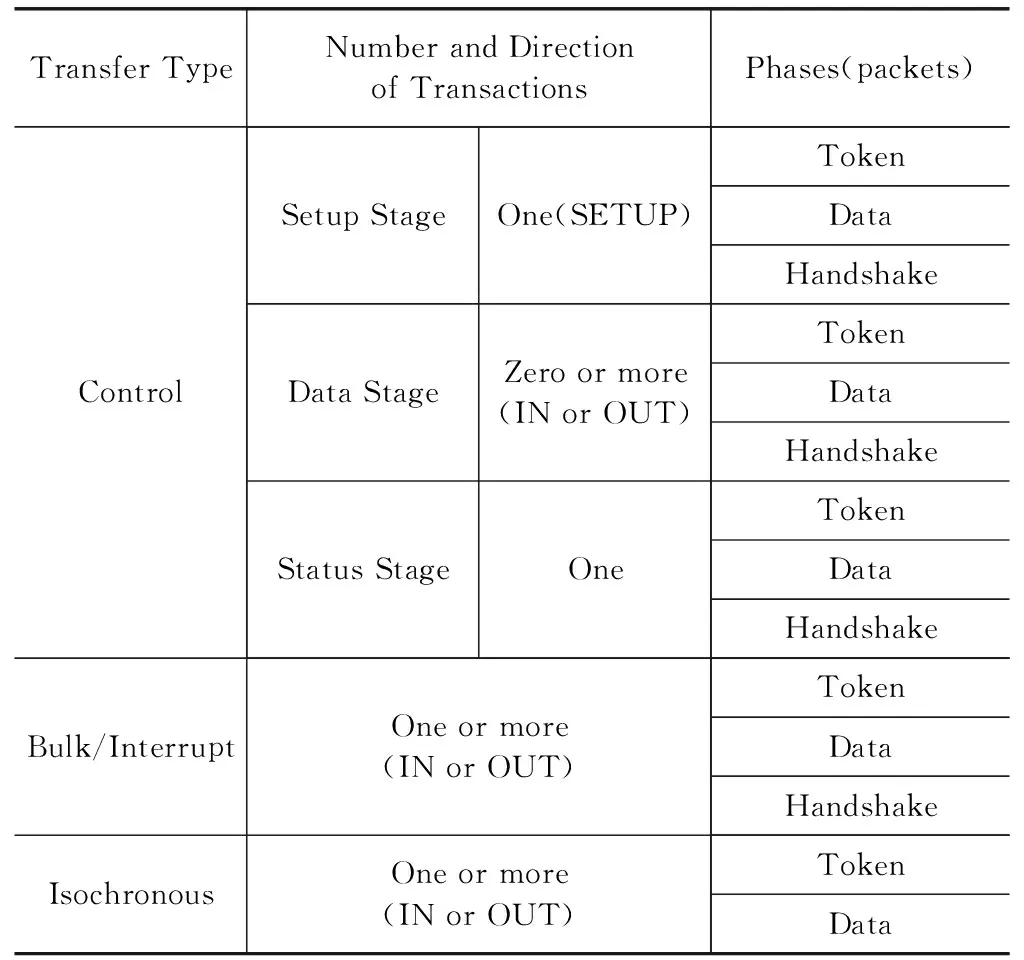

協議處理模塊作用是完成USB2.0協議規定的各項功能,處理SETUP、IN、OUT等各項事務。USB2.0協議中定義了4種數據傳輸類型:控制傳輸(Control Transfer)、批量傳輸(Bulk Transfer)、中斷傳輸(Interrupt Transfer)以及同步傳輸(Isochronous Transfer)。USB各種傳輸過程如表2所列。

表2 USB傳輸過程

2.3.1 USB控制傳輸

控制傳輸由2~3個階段組成,分別是建立階段、數據階段(可能沒有)和狀態階段,每個階段都由一次或多次事務傳輸組成[4]。

(1) 建立階段

主機從USB設備獲取配置信息,并設置設備的配置值。建立階段的數據交換包括了SETUP令牌包、緊隨其后的DATA0數據包以及ACK握手包。它的作用是執行一個設置的數據交互,并定義控制傳輸的內容(即在數據階段中IN或OUT的data包個數及發送方向,在建立階段已經被設定)。如果建立階段發送CRC錯誤,USB設備控制器不會有任何回應,如果正確接收到SETUP令牌包和8字節的DATA0數據包,USB設備控制器回應ACK,并且使能接收完成狀態標志。

(2) 數據階段

控制傳輸數據階段包括控制讀取(IN事務)和控制寫入(OUT事務),控制讀取是用于讀取USB設備描述符,控制寫入是用于傳輸USB設備的配置信息。控制讀取和控制寫入過程如圖3所示。

圖3 控制讀取和控制寫入過程

(3) 狀態階段

用來表示整個傳輸過程已經結束。狀態階段傳輸方向與數據階段方向相反,即數據階段是IN令牌包,狀態階段應為OUT令牌包;反之,數據階段是OUT令牌包,狀態階段為IN令牌包。

控制傳輸事務處理流程比較復雜,采用了三段式狀態機的方式進行設計,如圖4所示。

圖4 控制傳輸狀態圖

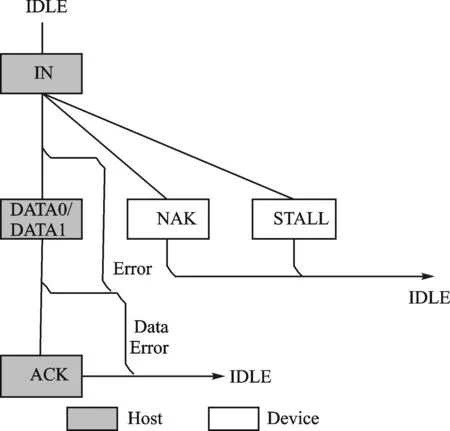

2.3.2 USB IN事務處理

USB的IN事務處理模塊主要完成USB中批量、中斷和同步傳輸的IN事務的處理,在主機給出IN令牌后,該模塊發出向主機發送數據的指令信號。該模塊會首先檢測當前的端點、緩存是否可用,若端點掛起,發STALL;若緩存不可用,發NACK。該模塊由狀態機實現,流程如圖5所示。

圖5 IN事務處理流程圖圖

2.3.3 USB OUT事務處理

OUT事務處理狀態機比較簡單,圖6是批量傳輸和中斷傳輸OUT事務處理流程。圖中NYET流程只有在批量傳輸中出現,中斷傳輸中設備不會回應NYET。

圖6 批量傳輸和中斷傳輸OUT事務處理流程圖

3 驗證綜合結果

3.1 VCS驗證

由于USB2.0事務較多,協議比較復雜,采用純信號的方式加入激勵信號驗證功能操作起來會非常復雜,實現比較困難。因此,為了提高驗證效率,采用基于事務的角度加入激勵。具體操作為在測試激勵和待驗證的USB2.0控制器之間加入附加層,使信號激勵的加入轉變為事務激勵的加入,從而在測試時只需按不同事務的加入來驗證控制器的功能。

以IN事務傳輸仿真驗證為例,本設計使用Synopsys

公司的VCS仿真軟件進行仿真驗證。仿真如圖7所示。圖中給出的是端點1執行IN事務傳輸,當時鐘上升沿dir置1開始由USB設備向主機發送數據,通過8位數據輸出信號data_out[7:0]可以看出,首先完成握手發送握手包1f,之后傳輸令牌包,8’h69為IN 事務PID高4位,是第4位的取反,8’hd5和8’hd8包含的16位數據為7位ADDR、4位ENDP以及5位CRC5,由此可以知道ADDR為1010101B,ENDP為0001B即端點1執行IN事務傳輸。令牌包之后會接著發送一個1f握手包,之后發送數據(1a、2b、3c…為自定義的傳輸數據)。

圖7 IN事務傳輸仿真

圖8所示為編寫testbench對各模塊代碼進行測試的結果,代碼覆蓋率超過90%,IP核邏輯正確。

圖8 各模塊代碼覆蓋率

3.2 Synplify Pro綜合

通過綜合工具Synplify Pro對IP核進行綜合驗證,綜合驗證結果如圖9所示。

使用不同的器件、密度、速度和等級時,AXI4-LiteI2C主機總線IP的性能和資源利用情況可能不同。IP設計時,適配采用默認設置。AXI4USB2.0設備控制器IP核可以應用于高云的GW2A55系列FPGA。性能和資源利用情況如表3所列。整個IP核占用資源只有2100 LUTs,具有170個I/O接口,最高速率可達120 MHz。

表3 性能和資源利用表

結 語

[1] Philips Semiconductors. ISP1501 Hi-Speed Universal Serial Bus peripheral transceiver Rev.2[S].2002.

[2] Cypress Semiconductor Corporation. CY7C68000 USB2.0 UTMI Transceiver Datasheet[S].2003.

[3] ARM Corporation. AMBA4.0規范優化性能與功耗[J].微電腦世界, 2010(4): 6.

[4] 劉清明.USB2.0設備控制器IP核設計與驗證[D].合肥: 中國科學技術大學, 2014.

USB2.0 Device Controller IP Core Based on AXI4 Bus

Han Jin1,Qin Hongchao1,Liu Kai2

(1.College of Information Science and Engineering,Shandong University of Science and Technology,Qingdao 266590,China;2.Shandong Gowin Semiconductor Technology Co.,Ltd.)

The design relies on the star nuclear program-Shandong domestic IP soft core platform.Based on the lastest on-chip bus AMBA4.0 protocol,the design of USB2.0 device controller IP core is completed using Verilog hardware description language,which includes the AXI4 bus interface module,the ULPI mode control module,the packet and unpacked module,the protocol processing module.The experiment results prove the correctness of the design,and it effectively reduces the logic resource utilization of FPGA. According to the actual application requirements, the designed USB2.0 controller IP core will be directly plant into the FPGA internal.It implementates the protocol of USB data transmission without the USB protocol chip.The design saves the product development cost and shorts the product design cycle effectively.

USB2.0;IP core;AXI4 bus;Verilog HDL

國家自然科學基金資助(項目編號:41572244);山東省自然科學基金(項目編號:ZR2015DM013)資助。

TP336

A

?迪娜

2016-08-08)