DSP與FPGA異步數據傳輸方法

邵曉剛,宋茂忠

(南京航空航天大學江蘇南京211100)

導航衛星信號模擬器能夠模擬動態衛星運動過程中接收機接收的衛星信號,為接收機特別是高動態高精度接收機的研制、測試提供模擬環境,同時也可以用于系統級仿真試驗[1]。在研制導航衛星信號模擬器時候,需要大量的浮點計算以及基帶信號生成,現在多采用基于“DSP+FPGA”的架構來進行導航信號模擬器的研制[2]。DSP作為參數計算部分用來實時產生衛星信號的狀態參數、控制參數和導航電文,FPGA主要進行基帶信號處理與中頻生成,DSP與FPGA數據通信時易產生數據丟失,系統不穩定,需要進行參數傳輸設計[3]。

1 DSP與FPGA參數傳輸方案

基于“DSP+FPGA”的架構設計GPS衛星信號模擬器,DSP芯片采用TI公司的高速浮點型處理器TMS320C6713B,具有強大的通用信號處理能力[4]。FPGA采用ALTERA CycloneII系列芯片,門數資源非常豐富,可滿足目前絕大多數的信號處理硬件編程和控制[5]。DSP與FPGA之間傳輸的參數表現為載波控制字、碼控制字、復位與啟動控制信號、導航電文等。基于上述平臺DSP通過32位EMIF總線往FPGA發送上述數據,由于EMIF總線輸入的時鐘速率和基帶讀取的時鐘速率不同,這就會產生異步數據跨時鐘域的傳輸問題,易造成亞穩態[6],這里通過異步FIFO來緩存DSP端發送過來的大量導航數據[7]。

2 FPGA中異步數據處理

2.1 DSP與FPGA接口設計

DSP與FPGA在硬件上通過EMIF連接,外部存儲器接口是TI DSP器件上的一種接口,EMIF可實現DSP與不同類型存EMIF可實現DSP與不同類型存儲器的連接[8]。FPGA掛接在DSP EMIF CE2空間,該空間配置為32位異步存儲器,如圖1所需接口信號。

圖1 EMIF接口原理圖

TED作為32位數據信號,TEA作為地址信號,TSDWEn作為寫使能信號,EXINT為中斷反饋信號。其中FPGA地址分配為0x01XY0,其中X作為衛星通道選擇,Y作為參數類型選擇[9]。

2.2 導航電文的異步傳輸

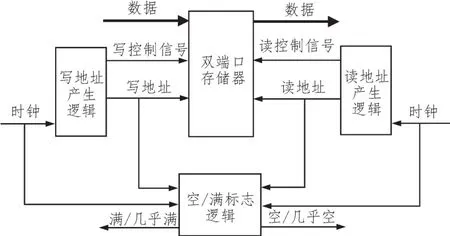

在導航模擬源中,為增加數據傳輸率、處理大量數據流、匹配具有不同傳輸率的系統為目的而廣泛使用異步FIFO緩存器,從而提高了系統性能。異步FIFO緩存器是一個先入先出的雙口緩沖器,對連續的數據流進行緩存,防止在進機制和存儲操作時丟失數據,為避免頻繁的總線操作,數據需集中起來進行存儲與讀取[10],如圖2所示。

圖2 異步FIFO原理圖

由于導航電文作為最重要的傳輸參數,而且傳輸的數據量比較大且只有’1’和’0’兩種狀態,可作為異步信號處理。異步信號跨時鐘域傳輸時,不滿足建立時間(setup time)和保持時間(hold time)[11],會造成采樣的不準確,所以我們這里采用了異步FIFO來對導航電文進行緩存。ALTERA的FPGA開發環境中提供異步FIFO內核,我們只需要基于該內核做接口開發,這樣可以降低編程難度,提高系統的穩定性。這里主要需要完成的是接口的信號設計,DSP往FPGA中寫接口信號包括寫時鐘以及寫使能其中寫使能信號表 達 為=20'h01210)&&(TSDWEn==0)。

2.3 控制字的異步傳輸

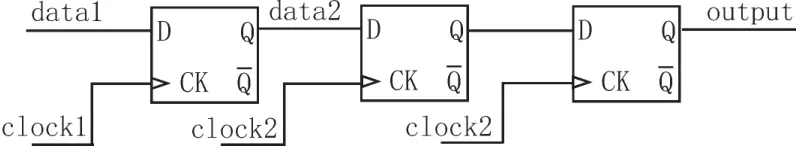

控制字的計算是基于FPGA中斷而進行的,在FPGA基帶處理模塊中進行時序控制,每隔100 ms產生一個EXINT中斷,DSP通過IO口檢測到中斷后,進行一次載波以及碼控制字的計算[12],控制字取32位,每次傳輸過來由于需要跨時鐘域,未免出現在基帶中控制字采樣時出現亞穩態,所以這里做了一個簡單的電平同步器[13]。電平同步器原理圖如圖3所示。

圖3 同步器原理圖

簡單的同步器,是由兩個觸發器級聯產生的,中間沒有其他組合邏輯。這種方法是通過保證后面的觸發器在接收前面觸發器的輸出的時候,前面的觸發器已經不再處于亞穩態,實現輸出穩定。基帶處理之前通過Verilog HDL編程做兩級觸發器級聯[14],控制字數據經過時鐘沿同步后,延遲時間為基帶時鐘域的1~2個時鐘周期,這樣輸出的數據就被同步到基帶的時鐘域中,避免出現亞穩態,數據丟失[15]。

3 實驗結果與分析

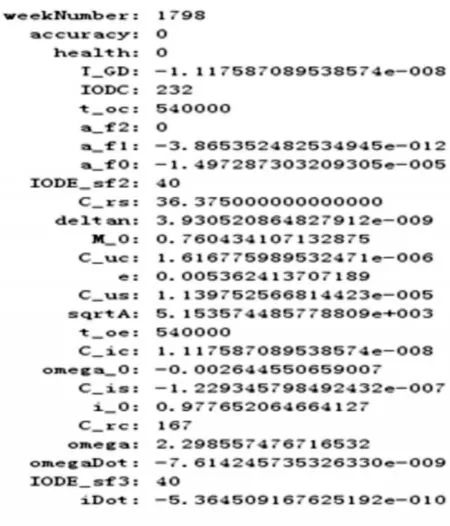

本實驗模擬產生13號GPS衛星信號,在Quartus開發環境下根據FIFO內核設計了信號接口,先將DSP計算出的導航電文通過根據時序要求選擇地址總線和數據總線通過EMIF發送給FPGA中的異步FIFO,然后再發送啟動模擬信號,這樣FPGA自己產生時序讀取異步FIFO中的導航電文數據,輸出NAV_OUT_13,再和生成的偽碼CA_CODE13異或輸出code13,運用Quartus中的Signal Tap工具抓取了FIFO輸出的導航電文以及生成偽碼信號,如圖4所示。FPGA基帶處理生成了13號星的中頻信號,在經過DA生成中頻模擬信號,最后生成射頻信號發射出去。運用GP2015采集射頻出去的13號衛星,成功捕獲并且解調出導航電文,結果如圖5所示。

圖4 導航電文與碼信號輸出

圖5 解調出導航電文中的星歷參數

4 結論

在設計導航衛星信號模擬源時候,基于“DSP+FPGA”的架構研制,能很好的滿足實時性,可靠性要求。但是在DSP[16-17]與FPGA通過總線交互數據時往往會產生跨時鐘域的異步數據傳輸的問題,通過異步FIFO和電平同步器的設計能很好地解決這個問題,減少亞穩態的,提高系統的穩定性。

[1]賈超廣,肖海霞.基于衛星信號模擬器的北斗接收機性能測試與分析[J].導航定位學報,2013,1(3):14-16.

[2]任風華,符強,紀元法.GPS模擬器的FPGA實現及其雜散研究[J].計算機測量與控制2013,21(8):2224-2226.

[3]劉志國.衛星導航信號模擬器研究與實現[D].太原:中北大學,2014.

[4]賀璽,楊述斌,曹珩.基于DSP和FIFO信號采集系統硬件設計及實現[J].武漢工程大學學報,2011,33(1):79-83.

[5]冀臻.GNSS衛星信號模擬器研究與實現[D].太原:中北大學,2011.

[6]黃隸凡,鄭學仁.FPGA設計中的亞穩態研究[J].微電子學,2011,41(2):255-273.

[7]胡波,李鵬.異步FIFO在FPGA與DSP通信中的運用[J].電子科技,2011,24(3):53-55.

[8]楊龍,李范鳴,劉士建.DSP EMIF與FPGA雙口RAM高速通信實現[J].現代電子技術,2014,37(13):10-13.

[9]王普.GPS衛星信號模擬源控制字計算和DSP數據接口[J].電子技術與軟件工程,2016:44-45.

[10]司嵐山.一種高速大容量異步FIFO存儲器設計[D].無錫:江南大學,2013.

[11]唐輝艷,李紹勝.FPGA設計中跨時鐘域同步方法的研究[J].鐵路計算機應用,2011,20(5):43-47.

[12]肖晶晶.實時多通道GPS信號模擬器的設計與實現[D].北京:清華大學,2011.

[13]趙曉海.跨時鐘域信號的幾種同步方法研究[J].電子設計應用,2012,20(7):139-144.

[14]張智明.基于FPGA的位同步電路設計[J].現代電子技術,2016,39(4):132-134.

[15]王曉婷.跨時鐘域設計方法研究[D].西安:西安電子科技大學,2012.

[16]倪原,劉琦,秦東旭,等.基于雙DSP的某飛行器飛行姿態控制系統的軟件設計[J].西安工業大學學報,2015(1):52-56.

[17]李忠楠,楊冰,王強,等.一種用于電力線通信的次優交織算法與DSP實現[J].電力信息與通信技術,2014(7):12-16.