一種應用于低功耗植入式醫療芯片的無線能量管理單元

夏瑞威++趙亞++高海軍

摘 要:針對低功耗無線供能植入式醫療系統,采用SMIC 0.18 m CMOS工藝設計出一種無片外電容的無線能量管理單元。其中,電荷泵整流器采用二極管連接低閾值本征MOS管以提高其整流效率。通過電源抑制增強電路提高帶隙基準源的電源抑制能力,另外,通過前饋消除技術提高低壓差線性穩壓器的PSR,并利用零極點追蹤補償技術增強LDO的穩定性。仿真結果表明,BGR輸出為1.17 V,靜態電流為36 A,PSR為-97 dB@DC、-40 dB@500MHz。LDO輸出為1.43 V,靜態電流為30 A ,PSR優于-85 dB@ DC、-60 dB@500 MHz,可提供負載電流為0.2 mA,在負載變化范圍內相位裕度均大于60度。

關鍵詞:低功耗;無線供能;電荷泵整流器;低壓差線性穩壓器;帶隙基準電壓源;電源抑制

中圖分類號:TM44;TN722;TP393 文獻標識碼:A 文章編號:2095-1302(2016)12-00-04

0 引 言

近幾年,受益于集成電路工藝技術與片上系統(System on Chip,SOC)的不斷發展,射頻識別、微傳感網絡以及環境感知等智能技術得到了飛速發展。其中,對于無線供能植入式芯片的能量管理、功耗等問題受到了持續關注與研究。當能量采集完成后,如何管理該能量是下一代被動與半被動植入式醫療設備的要點之一。

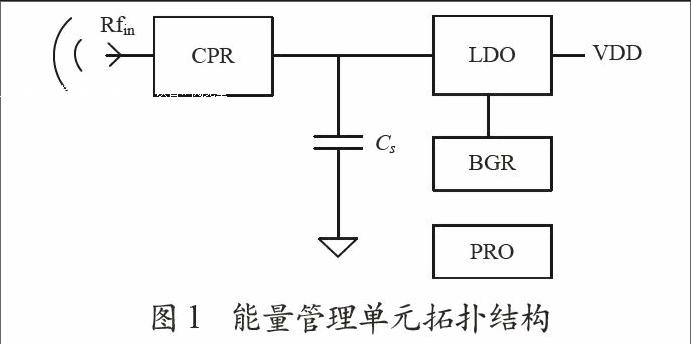

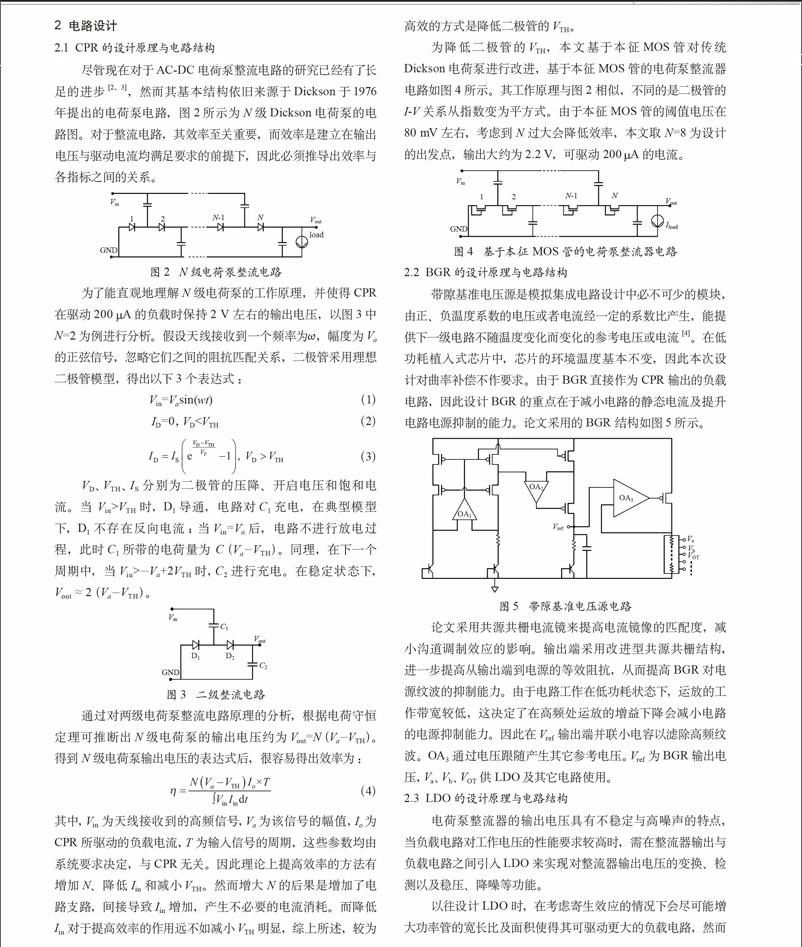

在低功耗植入式芯片中,如低噪聲放大器、模數轉換器等對工作電壓及其紋波都有一定的要求,因此須通過無線能量管理單元(Wireless Power Management Unit,WPMU)將其電源性能優化。在被動式芯片中,電荷泵整流器(Charge Pump Rectifier,CPR)、帶隙基準源(Bandgap Reference,BGR)、低壓差線性穩壓器(Low Dropout Regulator,LDO)是WPMU的重要組成單元[1]。芯片工作時,人體各種低頻信號(EEG、ECG)會通過相應的耦合方式傳輸到電源通路上,從而產生低頻噪聲,因此必須采用相關技術獲得高電源抑制比電源。論文首先通過電荷守恒定理對傳統Dickson電路進行動態分析及能量轉換效率的改進;然后采用電源抑制增強(Power Supply Rejection Boosting,PSRB)與前饋消除(Feed-forword Cancellation,FWC)等技術分別提高BGR、LDO在運放工作帶寬內的電源抑制力(Power Supply Rejection,PSR),并在輸出節點并聯電容以濾除超高頻紋波;最后為保證LDO在負載變化時的穩定性,利用零極點追蹤補償來滿足相位裕度的要求。

論文對高性能無線能量管理單元預設指標為:

(1)CPR在輸入500 mV交流小信號時能輸出2 V電壓并驅動200 A的電流。

(2)BGR輸出電源抑制比在LDO的工作范圍內盡可能大于60 dB,以減小對LDO的影響。

(3)LDO輸出電源抑制比在生物信號頻率處(01 kHz)及CPR輸入信號處大于60 dB,從而提供負載電路高性能的工作電壓。

(4)在滿足以上性能的情況下,盡可能減小電路工作時的靜態電流。

1 無線能量管理單元的基本原理

圖1所示為論文采用的無線供能能量管理單元拓撲結構。由圖1可知,WPMU主要包含CPR、BGR、LDO及保護電路(PRO)等模塊。芯片通過片外天線采集到由基站發射的高頻無線能量信號,CPR將信號整流后進行升壓,產生紋波較大的電壓,并將該能量儲存到Cs中。由BGR與LDO所組成的環路通過負反饋輸出紋波較小的VDD來驅動負載電路。其中BGR為LDO提供一個精準穩定的參考電壓,因此BGR的性能影響著LDO輸出電壓的性能。芯片中的保護電路包括過溫保護電路、過壓保護電路、限流電路,其主要目的在于意外情況下對電路關斷,實現對電路的保護。

設計能量管理單元時,在無線供能的環境下要注意相關性能的優化,而這又伴隨著其它性能的犧牲,下面將詳細分析論文采用的CPR、BGR、LDO設計原理及電路結構。

3 版圖及后仿真結果

采用SMIC 0.18 m CMOS工藝,在Cadence下對電路進行仿真驗證,無線能量管理單元的版圖如圖7所示,其中包含了CPR、BGR、LDO及PRO等模塊,芯片的尺寸大小為277 m×656 m。

電路在工作時要避免反饋環路發生震蕩,必須保證LDO環路的相位裕度,論文在tt、ff、ss三個工藝角下對其進行不同負載電流(0200 A)的仿真,仿真結果如表1所列。該結果表明在負載電流0200 A內,由于零極點追蹤補償的作用,相位裕度均大于60度,根據奈奎斯特穩定判據,LDO環路能在負載變化的范圍內穩定工作。

圖8所示為BGR、LDO的PSR仿真波形,從圖中可以看出,BGR采用PSRB技術后,PSR在低頻降低了近25 dB。當LDO采用FWC技術時,電源抑制在低頻段得到了顯著提升,電路空載時,在100 Hz內提升了近20 dB,滿載時提升了近40 dB。

圖912給出了WPMU中CPR與LDO的相關瞬態仿真結果,當輸入頻率為500 MHz、幅度為0.5 V的正弦波時,電路建立時間約為13 s,CPR的紋波約為5 mV,而LDO的輸出電壓紋波減小至2.3 V,即高頻處PSR約為-66 dB。因此論文采用的LDO在生物信號頻率處(DC-10 kHz)與輸入信號頻率處(100 MHz以上)具有較好的PSR。表2對相關文獻與本文設計進行性能比較,可以看出,該電源管理單元能輸出性能更好的工作電壓。

4 結 語

論文針對CPR、LDO、BGR進行研究,設計了一種應用于低功耗無線供能植入式醫療芯片的能量管理單元。采用SMIC 0.18 m CMOS工藝提供的本征MOS管使CPR的效率得到提升。利用PSRB將BGR的PSR在低頻處從-75 dB降低到-95 dB,這是優化LDO電源抑制能力的基本前提。通過FWC、零極點追蹤補償改善LDO的PSR與穩定度,在驅動0.2 mA的負載電流時,PSR為-85 dB@DC,而相位裕度在負載范圍內均大于60度,該性能可適用于對電源性能要求較高的模塊。

參考文獻

[1]郭文雄.應用于植入式經皮能量傳輸的集成電路研究與設計[D].廣州:華南理工大學,2013.

[2]Pierre Favrat, Philippe Deval, Michel J.Declercq. A High-Efficiency CMOS Voltage Doubler[J]. IEEE Journal of Solid-State Circuits, 1998, 33(3) : 410-416.

[3]To shiyuki Umeda, Hiroshi Yoshida, Shuichi Sekine, et al. A 950-MHz Rectifier Circuit for Sensor Network Tags With 10-m Distance[J]. IEEE Journal of Solid-State Circuits, 2006, 41(1): 35-41.

[4]Keith Sanborn, Dongsheng Ma, Vadim Ivanor. A Sub-1-V Low-Noise Bandgap Voltage Referen-ce[J]. IEEE Journal of Solid-State Circuits, 2007, 42(11) : 2466-2481.

[5]Mohamed El-Nozahi, Ahmed Amer, Joselyn Torres, et al. High PSR LOW Drop-Out Regulator With Feed-Forward Ripple Cancellation Techniq-ue[J]. IEEE Journal of Solid-State Circuits, 2010, 45(3) : 565-577.

[6]王憶.高性能低壓差線性穩壓器研究與設計[D].杭州:浙江大學,2010.

[7]溫曉珂.應用于射頻SOC芯片的低噪聲高PSRR的LDO的設計[D]. 上海:復旦大學,2011.

[8]韓曉婧,張子佑,劉鋒.一種毫微功耗的微弱能量收集電路設計[J].物聯網技術,2016,6(9):90-93.