基于AD9957和XC4VSX55在線動態(tài)可配QPSK調(diào)制器設(shè)計與實現(xiàn)

孫義卓++隋紹勇++段濤

摘 要:文中采用在線動態(tài)配置的方法,實現(xiàn)了QPSK調(diào)制器的通用、靈活設(shè)置,解決了在實際應(yīng)用中適應(yīng)性較差的難題,實現(xiàn)了設(shè)計目標。

關(guān)鍵詞:調(diào)制;QPSK;AD9957;XC4VSX55

中圖分類號:TN961 文獻標識碼:A 文章編號:2095-1302(2016)11-0-01

0 引 言

在實際應(yīng)用中,為了達到某些試驗?zāi)康模?jīng)常需要對QPSK調(diào)制器進行在線動態(tài)配置,而目前大部分調(diào)制器都是固定寫死的,若需要改變參數(shù)設(shè)置則必須重新燒寫程序,這樣給試驗帶來了不便。本文提出了一種基于XC4VSX55、AD9957的在線動態(tài)可適時配置參數(shù)的QPSK調(diào)制器的設(shè)計方法,解決了試驗難題。

1 芯片簡介

1.1 AD9957簡介

AD9957可以在成本、尺寸、功耗和動態(tài)性能等均非常關(guān)鍵的通信系統(tǒng)中作為通用I/Q調(diào)制器和捷變上變頻器。AD9957將一個高速直接數(shù)字頻率合成器(DDS)與一個具有高性能、高速率的14位數(shù)模轉(zhuǎn)換器(DAC)、時鐘乘法器電路、數(shù)字濾波器和其它DSP功能集成在一個芯片上。該器件可以在有線或無線通信系統(tǒng)中為數(shù)據(jù)傳輸提供基帶上變頻。AD9957是正交數(shù)字上變頻器(QDUC)系列中的第三款產(chǎn)品,該系列還包括AD9857和AD9856。該器件可以在工作速度、功耗和頻譜性能方面提供更好的性能。同其前款產(chǎn)品不同,該器件針對I/Q基帶數(shù)據(jù)支持16位串行輸入模式。此外,該器件可通過編程設(shè)置為單頻正弦波信號源或插值DAC。AD9957支持三種基本工作模式,分別為正交調(diào)制(QDUC)模式(默認)、DAC插值模式與單頻調(diào)制模式。工作模式通過控制功能寄存器中的工作模式位來進行選擇。

1.2 XC4VSX55簡介

XC4VSX55是Xilinx公司V4系列大門數(shù)FPGA,支持多種單端和差分I/O標準。例如LVTTL、LVCMOS及連接至板上其他器件。與單端I/O標準相比,差分信號可提供更好的噪音容限,產(chǎn)生更低的電磁干擾(EMI),且降低功耗。支持的差分標準有LVDS、LVPECL等。

2 實現(xiàn)原理

2.1 頂層實現(xiàn)原理

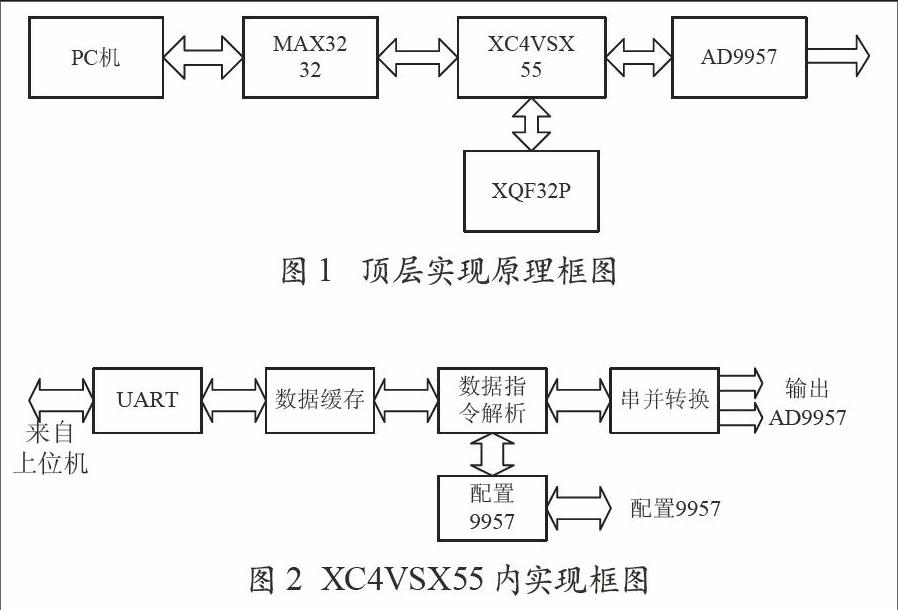

頂層實現(xiàn)原理框圖如圖1所示。可通過PC機進行在線配置,通過MAX3232進行電平轉(zhuǎn)換后發(fā)送給XC4VSX55,在XC4VSX55內(nèi)實現(xiàn)UART接口進行在線配置數(shù)據(jù)的收集并分析,在串并轉(zhuǎn)換后發(fā)送至AD9957進行QPSK調(diào)制。XQF32P用來給XC4VSX55加載程序。

系統(tǒng)工作時可通過PC機進行在線動態(tài)配置調(diào)試數(shù)據(jù)、調(diào)制速率及設(shè)置AD9957內(nèi)部工作時鐘等。

2.2 XC4VSX55實現(xiàn)原理

XC4VSX55為了實現(xiàn)與PC機通信,采用VHDL語言編寫UART(異步串口)程序,接收到數(shù)據(jù)后就緩存,然后對接收的數(shù)據(jù)進行指令解析,經(jīng)串并轉(zhuǎn)換后輸出給AD9957進行QPSK調(diào)制。XC4VSX55內(nèi)實現(xiàn)框圖如圖2所示。

3 結(jié) 語

本文通過MAX3232、XC4VSX55、AD9957等芯片設(shè)置了在線動態(tài)可配的QPSK調(diào)制器,提高了使用的靈活性、通用性,滿足了用戶對調(diào)制數(shù)據(jù)、調(diào)制數(shù)據(jù)速率等多樣化要求,符合設(shè)計要求。

參考文獻

[1]崔葛瑾.基于FPGA的數(shù)字電路系統(tǒng)設(shè)計[M].西安:西安電子科技大學(xué)出版社,2008.

[2]樊昌信,張甫翊,徐炳祥,等.通信原理(第5版)[M].北京:國防工業(yè)出版社,2001:259-260.

[3]胡廣書.數(shù)字信號處理理論、算法與實現(xiàn)[M].北京:清華大學(xué)出版社,2006:409-417.

[4]蘇濤,何學(xué)輝,呂林夏.實時信號處理系統(tǒng)設(shè)計[M].西安:西安電子科技大學(xué)出版社,2006:45-50.

[5] AD9957數(shù)據(jù)手冊[Z].