CMOS電路中外部能耗控制模塊的設計與實現

李瑞芳

摘 要: 傳統的大規模集成電路的功耗控制方法存在運算量高、精確度有限的問題。因此,基于雙閾值低功耗技術設計并實現CMOS電路中外部能耗控制模塊,采用雙閾值電壓技術通過較低閾值的晶體管設計CMOS能耗控制模塊。通過高閾值電壓的NMOS管控制低閾值模塊,降低電路的泄露電流,使用低閾值模塊中的NMOS管對CMOS門單元電路進行管理,提高門單元電路的運行效率,降低總體CMOS電路的功耗。采用雙閾值技術設計CMOS電路的單邊沿脈沖觸發器,對觸發器的時鐘響應電路進行優化,確保時鐘翻轉通過數字信號進行管理,極大降低時鐘翻轉頻率,減小電路動態功耗。實驗結果表明,所設計模塊具有較高的控制效率,較低的延遲和功耗,其控制下的CMOS電路節能效果顯著。

關鍵詞: CMOS電路; 能耗控制; 雙閾值; NMOS

中圖分類號: TN108+.7?34; TN432 文獻標識碼: A 文章編號: 1004?373X(2016)22?0112?0

0 引 言

集成電路工業的發展增強了CMOS電路運行頻率和集成度,也導致電路功率逐漸增加。大功耗導致系統穩定性和可靠性降低,提高了系統封裝的難度[1?2]。CMOS電路中的大功耗,使得芯片運行情況減弱,大大降低了芯片價值。因此,功耗問題成為CMOS電路快速發展過程中急需解決的問題。而傳統的大規模集成電路的功耗控制方法,存在運算量大、精確度有限的問題[3?5]。因此,采用合理的功耗控制方法,保證CMOS電路完成預期的功耗目標,成為相關任務研究的熱點方向。

以往研究出的集成電路能耗控制方法都存在一定的問題,如文獻[5]基于傳統晶體管功耗模塊,其依據電路完整的硬件描述實施功耗模擬,但是該模塊要求CMOS電路中存在完整的寄存器傳輸設計,并且其運行時間和內存消耗較高。文獻[6]通過PSPLCE模擬采集CMOS電路電源特征和數據,通過動態閾值功耗預測方法,實現CMOS電路功耗的有效控制,但其對電源穩定性要求較高,并且需要采用大量的數據進行模擬分析,運算效率低,存在一定的局限性。文獻[7]通過降低CMOS電源電壓,控制CMOS電路功耗,設計出電流型CMOS電路,實現CMOS電路能耗的合理控制,但是該方法存在控制精度的缺陷,并且容易產生過電量問題。文獻[8]采用基于仿真的CMOS電路平均功耗估計方法,其通過全部可能的輸入組合對電路進行仿真,依據仿真功耗運算平均功耗,但是該方法需要用戶明確輸入模式中的全部信息,局限性較高。文獻[9]通過最小平方方法預測CMOS電路的平均能耗,其通過點預測方法,可在高精度下得到較高的收斂效率,但該方法的估計結果容易受到電路內部和外部環境的干擾,無法對電路能耗進行準確控制。

為了解決上述分析方法存在的問題,降低CMOS電路能耗,采用雙閾值電壓技術通過較低閾值的晶體管設計CMOS能耗控制模塊,也就是低閾值模塊。通過高閾值電壓的NMOS管控制低閾值模塊,降低電路的泄露電流;通過低閾值模塊中的NMOS管對CMOS門單元電路進行管理,提高門單元電路的運行效率,降低總體CMOS電路的功耗。

1 CMOS電路中外部能耗控制模塊設計

1.1 雙閾值CMOS電路能耗控制過程

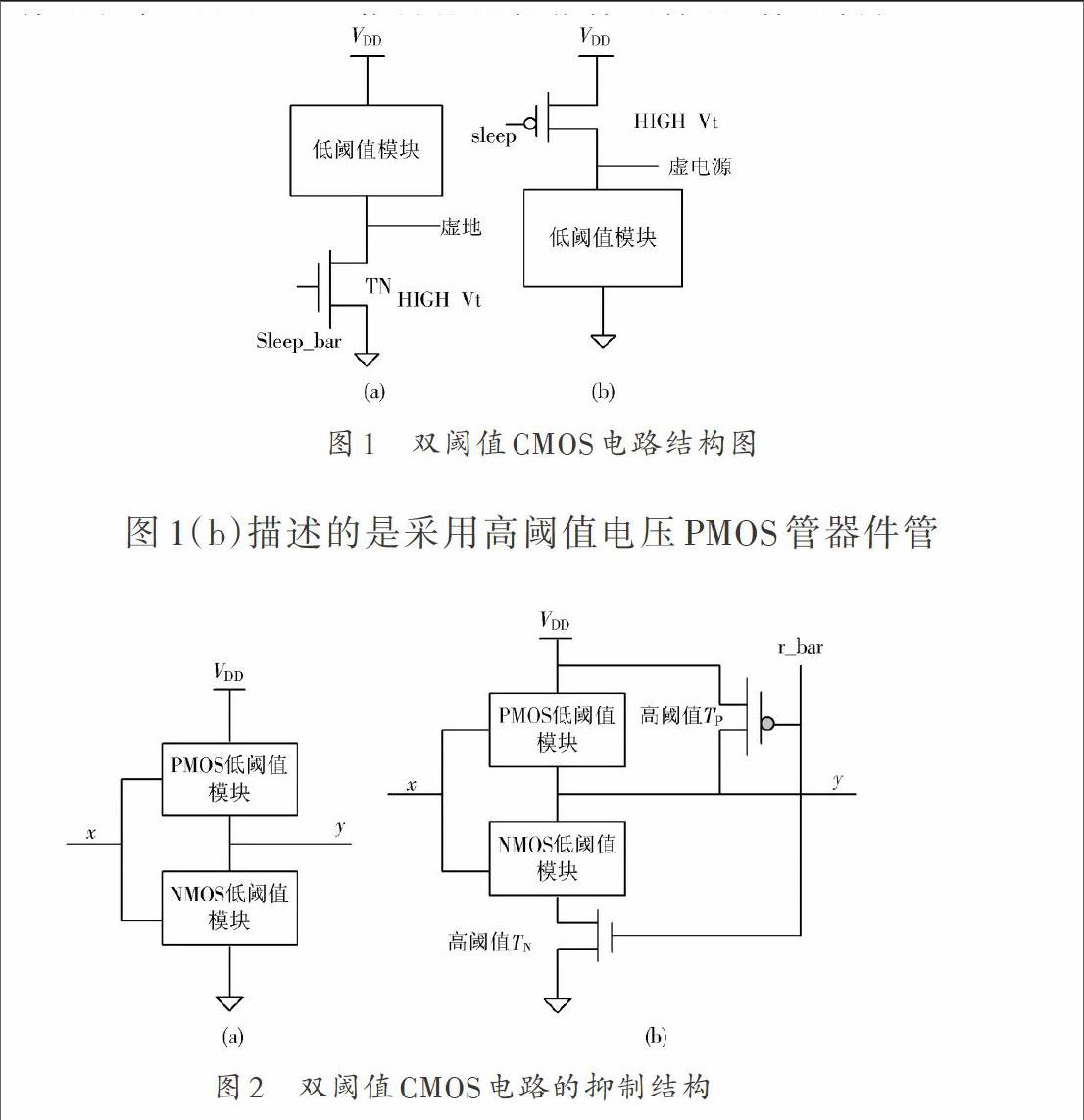

雙閾值CMOS電路結構圖如圖1所示。為了提高CMOS電路邏輯單元的性能,通過較低閾值的晶體管設計CMOS能耗控制模塊,也就是低閾值模塊。在低閾值模塊間設計了高閾值電壓的NMOS管TN,如圖1(a)所示。通過Sleep_bar管理信號調控低閾值模塊,如果管理信號為1,則TN導通,低閾值電路模塊可順利運行,模塊同地連接。TN管的漏極可看成虛地,形成微高于0的電壓,該電壓不會干擾總體電路的運行。受到漏極電壓的干擾,低閾值模塊的晶體管中的電壓增加,使得泄露電流減少;如果管理信號設置為0,則TN管不導通,低閾值模塊停止運行,同地斷開,虛地點懸空。TN管較高的閾值電壓導致自身泄露電流降低,有效控制了低閾值模塊電流,大大降低了總體CMOS電路功耗。

圖1(b)描述的是采用高閾值電壓PMOS管器件管理低閾值模塊的結構,該結構的原理與高閾值NMOS管管理相似,通過sleep信號的置復位管理情況,管理低閾值模塊電路的運行,實現降低功耗的目標。高閾值NMOS管管理低閾值模塊,具有較低的導通電阻,能夠更加節省CMOS電路硅片的面積。

雙閾值CMOS電路結構能夠完成切斷電路以及電源回路的設計,過濾額外功耗。通過對CMOS電路結構中NMOS管以及PMOS管的邏輯互補特性,確保總體電路系統的上拉和下拉形成不同通路輪流互相導通,完成CMOS電路外部能耗的合理控制。

雙閾值CMOS電路的抑制結構如圖2所示。

分析圖2能夠看出,當雙閾值CMOS電路采用圖2(a)描述的結構時,其輸出端在高閾值NMOS管子停止后會形成懸空問題,會產生負面干擾。而使用圖2(b)結構情況下,額外產生的高閾值PMOS管,將在NMOS管終止運行情況下保存輸出端的穩定,限制輸出節點懸空問題的發生。

實際控制CMOS電路外部能耗過程中,通過冗余檢測信號r替代管理信號Sleep調控高閾值NMOS管的通斷,主要是因為信號r能夠分析CMOS電路的冗余狀況,并且其具有同管理信號Sleep的相同作用。如果信號r檢測到低閾值模塊為冗余狀態,則終止NMOS管的運行,確保邏輯塊停止運行,避免其泄露電流,降低電路能耗。該結構設計能夠避免低閾值模塊出現泄露電流現象,并且合理控制CMOS電路的冗余問題,避免出現冗余情況下的電平翻轉波動的傳遞,最大程度降低電路動態功耗。

1.2 雙閾值CMOS電路門單元運行控制

通過上述分析的雙閾值CMOS電路能耗控制過程可得,采用高閾值NMOS管可設置該低功耗控制裝置。因此,在各CMOS門單元電路中融入Sleep管理信號,通過低閾值模塊中的NMOS管對不同CMOS門單元電路的運行情況進行有效管理,提高門單元電路的運行效率,降低總體CMOS電路的功耗。通過門單元能夠設計出雙閾值的反相器、與非門以及或非門等,如圖3所示。

采用關聯信號Sleep_bar調控高閾值NMOS管的通斷,若Sleep為0,Sleep_bar為1,則門單元正常工作;否則,若Sleep為1,終止高閾值管的運行,電路休眠,門單元終止工作,最大程度降低電路能耗。

1.3 雙閾值CMOS電路中單邊沿脈沖觸發器設計

觸發器是CMOS電路中的關鍵電路單元,對其功耗進行優化控制,可降低CMOS電路的功耗。將CMOS電路的總平均功耗當成觸發器的功耗參數,主要包括觸發器內在功耗、數據驅動功耗以及時鐘驅動功耗。觸發器中的緩沖反相器驅動數據輸入以及時鐘信號的過程中,將形成數據驅動功耗和時鐘驅動功耗。觸發器內部功耗是其內部消耗的功耗。因此,對觸發器進行優化設計,降低其功耗,可確保總體CMOS電路能耗的最低化。觸發器的時序參數是其塑造時間以及單元本征延時。觸發器的塑造時間是數據在時鐘信號沿到來前的持續時間,如圖4所示。其中,[TD-C]是數據Data到時鐘C延時,[TD-Q]是數據D到輸出Q的傳播時間,其是單元的傳播延時,[TC-Q]是時鐘到輸出的延時,同持續時間具有一定的關聯性,其通過式(1)獲取。

圖5為設計的雙閾值CMOS電路中的單邊沿脈沖觸發器,該觸發器能夠對CMOS電路能耗進行優化處理。圖5中設計的單邊沿脈沖觸發器包括時鐘響應電路和數據響應電路。通過高閾值電壓和低閾值電壓分別設計數據響應電路和時鐘響應電路。該觸發器中時鐘脈沖時序產生過程為CLK信號通過反相器鏈,獲取一個延時反向信號CLKBD,計算該信號和CLK信號,能夠獲取高窄脈沖CLKP信號。但是時鐘脈沖跳變時,容易形成電平的翻轉,導致CMOS電路形成較高的動態功耗。因此,為了降低電路功耗,采用雙閾值技術設計單邊沿脈沖發生電路,對時鐘信號進行調控,降低翻轉率,減少時鐘電路動態功耗。該觸發器采用時鐘信號CK在D和Q間的延時差間產生脈沖,并且采用異或電路進行優化設計,得到如圖6所示的單邊沿脈沖發生電路。

該單邊沿脈沖發生電路的脈沖信號波形示意圖如圖7所示。

傳統CMOS電路觸發器中的電路,存在時鐘通過反相器翻轉的跳變,導致動態功能增加。因此,將單邊沿觸發器電路數據端D信號和Q信號當成時鐘響應電路的使能信號,確保時鐘翻轉出現D信號處于高電平的區間。

該設計能夠確保當D信號處于低電平區間時,時鐘信號不會出現翻轉,降低反相鏈電路以及數據采樣電路中的電平翻轉發生率,減少動態功耗,實現CMOS電路的低功耗設計。同時設計的雙閾值單邊沿脈沖觸發器,能夠降低時鐘在電路中的跳變,降低時鐘脈沖的數量以及晶體管跳變數量,最大程度上減少功耗。

2 實驗分析

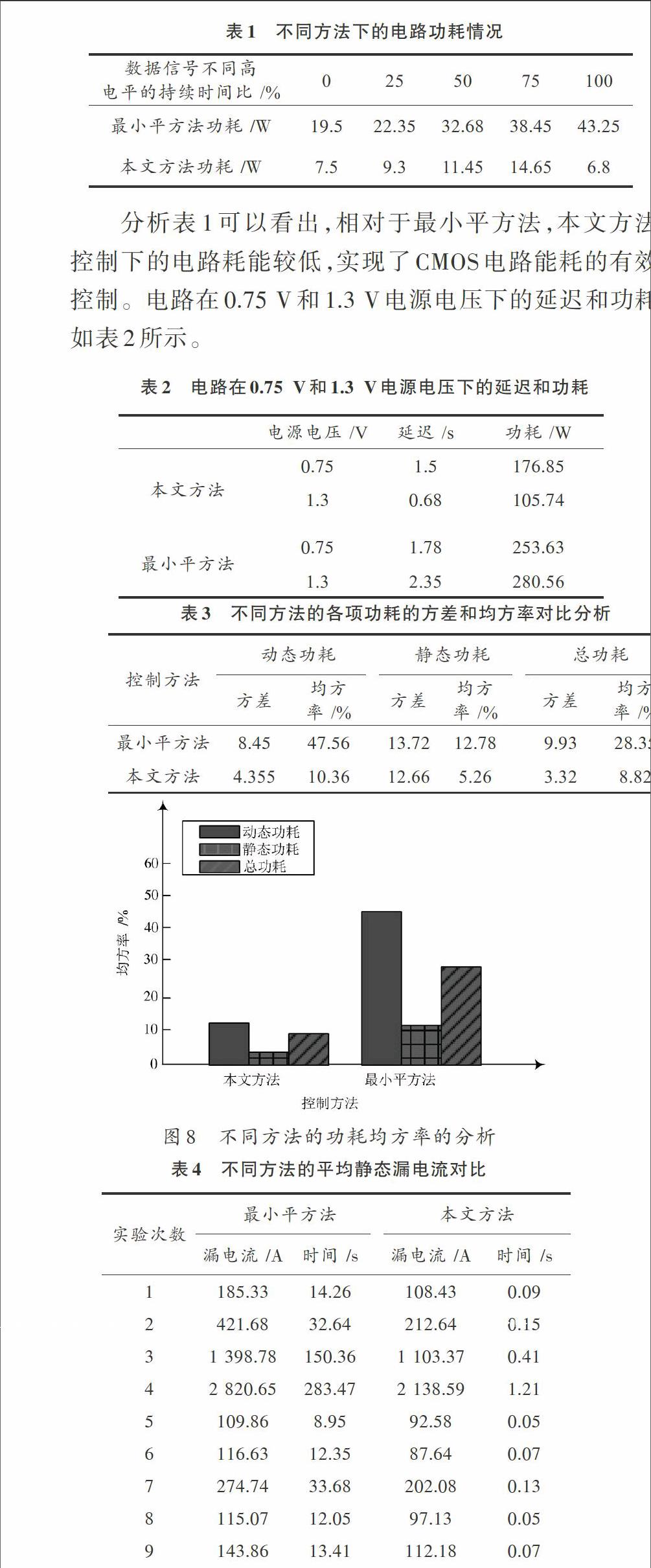

本文采用SMIC 0.11 μm CMOS工藝設計相關電路,通過HSpice軟件進行仿真實驗中,設置觸發器的時鐘頻率為200 MHz,電源電壓是1.0 V。實驗在數據信號不同高電平持續時間下,對比分析本文方法和最小平方法的CMOS電路功耗情況如表1所示。

表1 不同方法下的電路功耗情況

分析表1可以看出,相對于最小平方法,本文方法控制下的電路耗能較低,實現了CMOS電路能耗的有效控制。電路在0.75 V和1.3 V電源電壓下的延遲和功耗如表2所示。

分析表2可以看出,在相同電源電壓下,采用本文方法控制的CMOS電路,其電路延時和功耗低于最小平方法。而在不同電源電壓下,隨著電源電壓值的提高,不同方法下的CMOS電路延遲和功耗都增加,但是本文方法的延遲和功耗始終低于最小平方法。

兩種方法下CMOS電路動態功耗、靜態功耗和總功耗對比情況如表3所示。

表3 不同方法的各項功耗的方差和均方率對比分析

依據表3中的數據可以獲取圖8中不同方法的功耗情況對比結果,能夠看出,不同方法的靜態功耗的均方率低于動態功耗,并且動態功耗的波動幅度較高,而靜態功耗的變化較為平穩。而本文方法的靜態功耗略低于最小平方法,但動態功耗遠遠低于最小平方法,并且總功耗遠低于最小平方法。說明本文方法控制下的CMOS電路功耗較低,具有較高的優勢,能夠滿足CMOS電路節能控制的需求。

分析表4可得,相對于最小平方方法,本文方法的控制時間較低,能夠極大提高控制效率,并且相差若干數量級。在本文方法下的CMOS電路漏電流低于最小平方法,說明本文方法的節能效果較優。

3 結 論

傳統的大規模集成電路的功耗控制方法,存在運算量大、精確度有限的問題。因此,基于雙閾值低功耗技術設計并實現CMOS電路中外部能耗控制模塊,采用雙閾值電壓技術通過較低閾值的晶體管設計CMOS能耗控制模塊,也就是低閾值模塊。通過高閾值電壓的NMOS管控制低閾值模塊,降低電路的泄露電流,通過低閾值模塊中的NMOS管對CMOS門單元電路進行管理,提高門單元電路的運行效率,降低總體CMOS電路的功耗。采用雙閾值技術設計CMOS電路的單邊沿脈沖觸發器,對觸發器的時鐘響應電路進行優化,確保時鐘翻轉通過數字信號進行管理,極大降低了時鐘翻轉頻率,減小了電路動態功耗。實驗結果說明,所設計模塊具有較高的控制效率,較低的延遲和功耗,其控制下的CMOS電路節能效果顯著。

參考文獻

[1] 李志遠,曹貝,卜丹,等.互連線對CMOS電路性能的仿真分析[J].黑龍江大學自然科學學報,2014(5):697?700.

[2] 王玥.基于130 nm CMOS工藝UHF RFID系統中頻率綜合器的研究與設計[D].合肥:中國科學技術大學,2015.

[3] 肖奔,殷蔚.利用Cadence設計CMOS低噪聲放大器[J].現代電子技術,2009,32(10):8?10.

[4] 張麗.磁隧道結模型及自旋轉移力矩磁隨機存儲器設計技術研究[D].西安:西安電子科技大學,2014.

[5] 馮海濤,裴志強,劉寶娟.COMS電路的參數提取及模型建立[J].微處理機,2012,33(6):4?5.

[6] 張少強.基于CMV300的CMOS相機光電響應特性研究[D].北京:中國科學院研究生院,2015.

[7] 盧沖贏,徐立新,李建華,等.CMOS兼容高Q值微機電系統懸浮片上螺旋電感[J].兵工學報,2014,35(5):634?639.

[8] 王冠華.一種基于CMOS的I/F轉換電路的設計與研究[D].哈爾濱:黑龍江大學,2014.

[9] 劉仲方.CMOS電路低功耗設計與優化研究[D].杭州:浙江大學,2015.