雙DSP共享Flash程序加載引導設計與實現*

王怡林

(光電控制技術重點實驗室,河南 洛陽 471009)

?

雙DSP共享Flash程序加載引導設計與實現*

王怡林

(光電控制技術重點實驗室,河南 洛陽 471009)

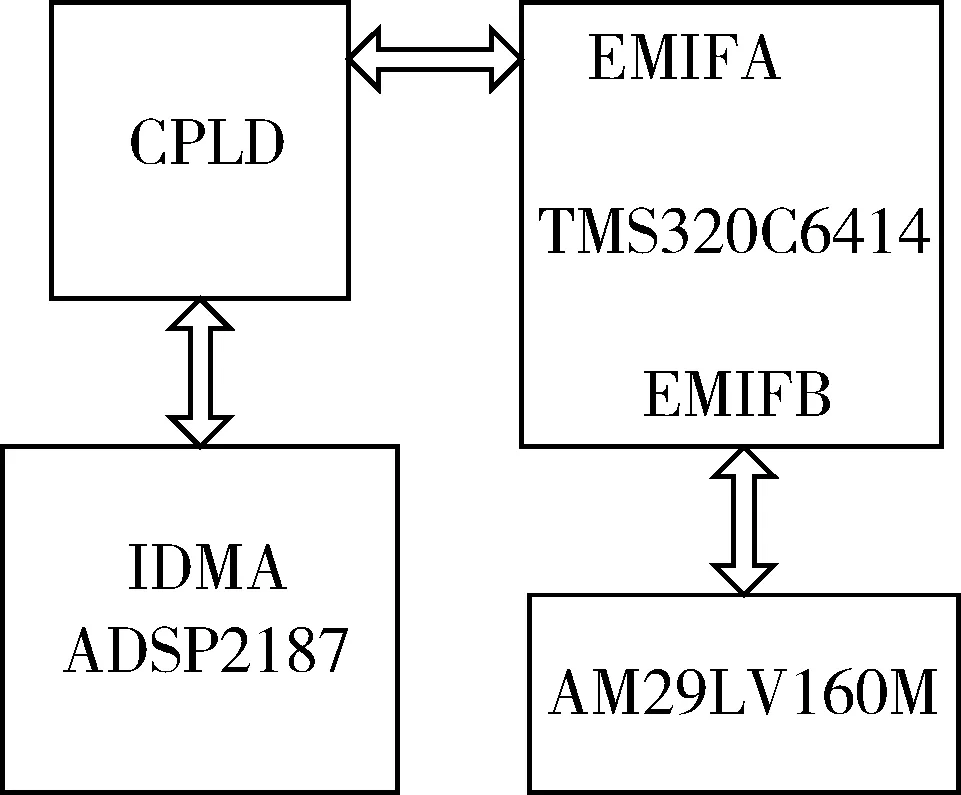

針對雙DSP共享Flash進行程序加載引導的復雜問題,對基于TMS320C6414和ADSP2187的雙DSP程序加載引導方法進行了研究與設計。其中TMS320C6414作為主處理器,ADSP2187作為協處理器,共享的Flash芯片連接在TMS320C6414的EMIFB接口上,TMS320C6414通過EMFIA接口與ADSP2187的IDMA接口連接。系統上電后,TMS320C6414首先從Flash芯片讀出主處理程序并完成自身加載和引導,然后讀出協處理程序,發送給ADSP2187并協助其完成加載和引導。

TMS320C6414;ADSP2187;共享Flash;加載;引導

0 引言

在紅外目標跟蹤領域,隨著算法復雜度的提升,運算量增長速度非常驚人,這使傳統的單DSP處理系統難以負荷, 因而對復雜的信號處理算法進行分塊并在硬件系統上采取多DSP 并行處理的方法勢在必行[1]。某信息處理平臺是某光電跟蹤裝置的核心,為滿足系統要求,該平臺以TMS320C6414和ADSP2187兩型DSP芯片為核心進行設計。基于體積、成本等限制,需兩個DSP共用一片Flash完成程序存儲,并在上電時順利完成兩個DSP程序的加載和引導。本文針對這一要求進行研究,設計了一種兩個DSP共享Flash的程序加載引導方法。

1 系統方案設計

TMS320C6414是TI公司推出的一款32位定點數字處理器,采用超長指令字結構,一個周期可同時執行8條指令,主頻最高達600 MHz[2],內部包括64個用于配置的32位寄存器,還有6個計算單元(ALU),2個乘法器。接口方面具備2個外部存儲接口,3個多通道緩沖串行接口, 1個主機接口和通用I/O接口等,還具備EDMA功能。

ADSP2187是ADI公司的ADSP系列的定點數字信號處理器[3],內含3個相互獨立的計算單元,即ALU、MAC和桶形移位器。除此之外,還有1個程序控制器(PC),1個可編程的定時器,2個數據地址產生器,以及32 K×24 bit的程序存儲空間和32 K×16 bit的數據存儲空間。對外接口方面包括1個可編程的Flash I/O,2個串口,1個16 bit的內部DMA接口以及1 B DMA接口(BDMA)。

基于兩個處理器的特點,本設計將Flash芯片連接在TMS320C6414上,程序的加載和引導由TMS320C6414主導完成。首先對TMS320C6414 的啟動模式進行配置。TMS320C6414 的啟動模式由其上電時的EMIFB接口地址總線中的BEA[15:14](BOOTMODE[1:0])的連接電平決定, 在復位期間檢測這兩位的高低電平來決定TMS320C6414的引導模式。本設計將TMS320C6414的引導模式配置成使用默認的8位ROM時序。TMS320C6414完成自身的程序引導后,通過IDMA接口向ADSP2187發送其程序并控制對方完成引導[4]。兩個處理器及存儲器連接關系如圖1所示。

圖1 處理器及存儲器連接關系

2 接口電路設計

要通過TMS320C6414來完成ADSP2187的程序加載和引導,首先要使兩者之間建立通信連接,由于兩個處理器架構以及對外接口的不同,需要對兩個處理器的通信接口進行匹配性設計,以滿足數據傳輸需求。

TMS320C6414的對外通信接口主要有兩個EMIF接口、兩個McBSP接口、一個HPI接口以及通用I/O等其他接口。ADSP2187主要的對外數據通信接口是IDMA接口,且可通過IDMA完成程序加載和引導。根據這兩個處理器接口的特點,基于EMIFA接口和IDMA接口來進行兩個處理器的數據通信接口電路設計。

EMIF接口全稱為外部存儲器接口(External Memory Interface),是C6000系列DSP主要的外部存儲器擴展接口,最高數據吞吐率可達1 200 MB/s。可以與目前幾乎所有的存儲器類型直接連接,包括SBSRAM、SDRAM、SRAM、FIFO等以及其他可以共享內部存儲空間的設備。

相比C6000系列其他DSP型號,TMS320C6414的EMIFA接口具有以下特點:

(1)總線寬度達64 bit。

(2)接口時鐘可以基于其輸入時鐘在片內產生,有3種方案:1/6×CPU時鐘、1/4×CPU時鐘和外部輸入時鐘。

(3)具有一個可編程同步存儲器控制器。

(4)具備PDT信號,可支持外部設備之間的數據傳輸。

ADSP2187的IDMA接口實質上是一個并行的I/O接口,當ADSP2187作為從機時,主機可通過該接口讀/寫ADSP2187內部的存儲器和寄存器。IDMA接口具有復用的16 bit數據/地址總線,支持對其內部16 bit數據存儲器和24 bit程序存儲器的訪問,對IDMA的訪問是完全異步的。

IDMA接口的控制信號包括選擇信號(IS#)、讀取信號(IRD#)、寫入信號(IWR#)和地址鎖存信號(IAL#)。當選擇信號和地址鎖存信號有效時,ADSP2187將總線上的數據當做地址寫入IDMA控制寄存器,當選擇信號和讀取信號有效時,ADSP2187將控制寄存器內地址所指存儲單元的內容輸出到總線上,此過程構成一個完整的IDMA接口讀取操作。寫入操作和讀取操作的地址傳輸方式一致,完成地址傳輸后,將選擇信號和寫入信號置為有效,待寫入數據發送到總線上,ADSP2187將總線上的數據寫入IDMA控制寄存器內地址所指存儲單元。

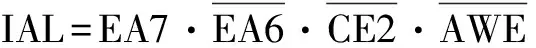

本設計將EMIFA的CE2空間設成16 bit異步接口,數據總線ED15:0與IDMA總線IAD15:0對應連接,EMIFA地址總線EA6和EA7求異或后再與片選信號CE2求或后作為IDMA接口的選擇信號(IS#),EA6求非后與EA7、CE2以及EMIFA的讀取信號ARW共4個信號一起求與作為IDMA接口的讀取信號(IRD#)輸入, EA6求非后與EA7、CE2以及EMIFA寫入信號AWE共4個信號一起求作為IDMA接口的寫入信號(IWR#)輸入, EA7和EA6求非、ARE非、AEW非、CE2非共5個信號求與后作為地址鎖存信號(IAL#)輸入。CPLD具有編程靈活等優點[5],本設計中采用CPLD完成譯碼。ADSP2187的IDMA接口輸入信號運算關系如下:

IS=CE2+(EA6?EA7)

在TMS320C6414看來,ADSP2187控制寄存器的映射地址是0xA000 00A0,數據寄存器的映射地址是0xA000 0050。

值得說明的是,僅僅完成相關信號的譯碼和地址映射還不夠,還需要對EMIFA和IDMA進行時序匹配。對于IDMA來說,有短周期和長周期兩種讀/寫方式選擇,后者需要主機檢測IACK信號的狀態來判斷IDMA是否準備好。本設計選用短周期讀/寫操作,其寫入操作的時序圖如圖2所示。

圖2 IDMA寫入操作時序

本設計中,EMIFA時鐘設置為1/6×CPU時鐘,CPU時鐘為480 MHz,則EMIFA時鐘為120 MHz。EMIFA接口CE2空間的時序由寄存器CE2CTL控制,主要包括建立時間、處罰時間、保持時間三項參數設置,三項參數均以時鐘周期數來表示。

根據圖2中IDMA接口的時序要求,建立時間、觸發時間和保持時間的總和應大于tIWP,換算后3項參數的和應大于等于2,同時保持時間應大于tIDH,將CE2CTL相應參數設為1即可。

TMS320C6414向ADSP2187寫入數據的流程為:先向地址0xA000 00A0寫存儲地址,然后向0xA000 0050寫入待寫數據即可完成寫操作。讀操作的時序匹配方法和流程與寫操作相似,不再詳述。

3 TMS320C6414加載引導方法

當光電跟蹤裝置上電后,TMS320C6414 進入復位狀態,完成復位后, 其只能先將1 KB大小的程序代碼自動加載到內部RAM。通常情況下,光電跟蹤裝置的信息處理程序規模遠遠大于1 KB,為了完成整個程序的加載和引導,必須編寫一段程序搬移代碼來將整個信息處理程序搬運到內部RAM,并且搬移低代碼的大小不能超過1 KB,按照TMS320C6414用戶手冊的要求,須用匯編語言完成,搬移程序在完成了信息處理程序的搬運后,須將PC指針指向信息處理程序的入口,自此信息處理程序才能開始運行,進而完成目標識別和跟蹤任務。完整的搬移程序的代碼及注釋如下:

…………;

//相關寄存器初始化工作結束

S_R .set b4

D_R .set a4

//將程序長度、RAM首地址、Flash首地址的存儲首地址拷貝進寄存器A3

mvkl copy_table, A3

mvkh copy_table, A3

//程序加載開始

copy_section_top:

ldw *A3++, B0

//將程序長度加載到B0

ldw *A3++, A4

//將運行首地址加載A4

ldw *A3++, B4

//將程序在Flash中的首地址加載到B4

nop 2

[!b0] b copy_done

//判斷拷貝是否完成

nop 5

shr B0,2,B1

//將B0除以4后加載到B1

//開始進行程序加載

copy_loop:

ldw *S_R++,B5

|| mv B1, A1

//待拷貝長度加載進A1

|| sub B1, 1, B1

//長度減1

//將程序從Flash讀入B5

[B1] ldw *S_R++,B5

||[B1] sub B1, 1, B1

//將B5中的程序加載到RAM中

stw B5,*D_R++

|| sub A1, 1, A1

[A1] stw B5,*D_R++

||[A1] sub A1, 1, A1

[B1] b copy_loop

//判斷是否完成加載

nop 5

//跳轉到開始處進行下一段的加載

b copy_section_top

nop 5

//加載完成,對相應的寄存器進行設置

copy_done:

mvkl 0x01840000,A4

mvkh 0x01840000,A4

stw B4,*A4

nop 5

mvkl .S2 _c_int00, B0

mvkh .S2 _c_int00, B0

B .S2 B0

nop 5

//各段長度、RAM首地址、Flash首地址設置

copy_table:

; .text

//代碼段長度

.word 0x00029220

.word 0x00000400

.word 0x64010400

; .cinit

//變量段

.word 0x00002dcc

.word 0x000460e0

.word 0x64039620

.word 0x0

//所有段結束標志

4 ADSP2187加載引導方法

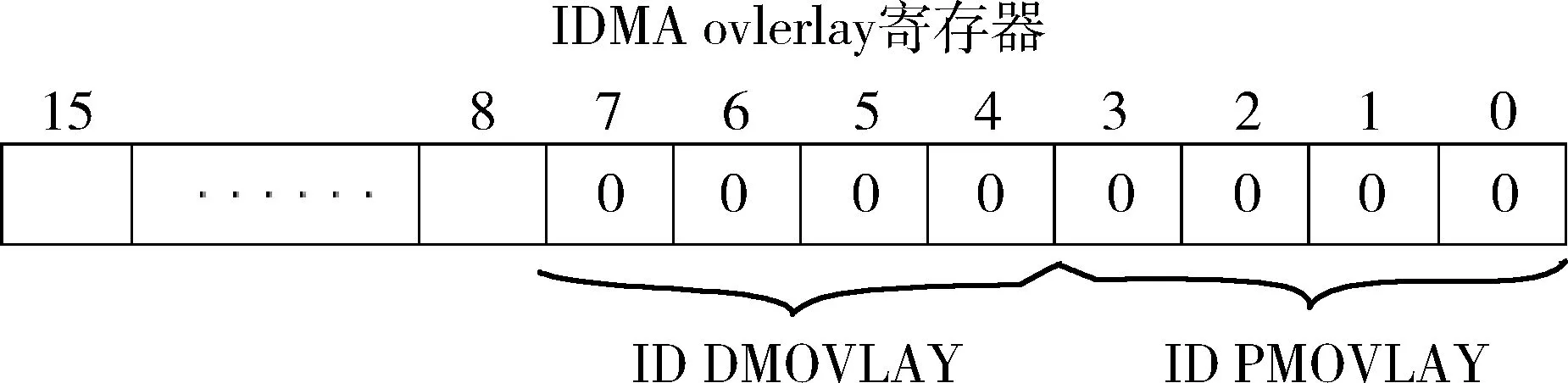

ADSP2187支持從片外ROM和IDMA接口引導兩種方式,非常方便用戶設計系統的需要[6]。本文所述信息處理機采用從IDMA接口引導的方式實現預處理程序的加載引導,ADSP2187上電后,從IDMA接口接收主處理器TMS320C6414傳輸的程序并執行。

ADSP2187函數根據在存儲器中所處的位置分為函數段、數據段,函數段和數據段又根據所處的OVERLAY頁面再分為不同的段[7]。每段前3個數據標示了該段的數據長度、該段在存儲區域的首地址和該段所處的頁面。該段數據處于函數區還是數據區由首地址的14位標示。

TMS320C6414首先對ADSP2187進行復位操作,然后從Flash中讀取該段數據的函數區字節數、函數區首地址和函數段所處的頁面,再從Flash中搬移1 B,通過IDMA口寫到ADSP2187的函數區,寫完后再從該函數區地址讀出數據并與所寫的數據進行比較,如果不相等則重新寫該地址和校對,循環TryCycle次退出;如果相等,則進行下一個字節的傳輸,直到該段數據全部傳輸到ADSP2187中。同樣地,TMS320C6414再把其余數據通過IDMA口傳輸到ADSP2187中,最后在ADSP2187的0地址寫數啟動ADSP2187運行,并以此判斷整個循環的結束。因為ADSP2187函數區數據為24 bit,因此對函數區數據讀寫時需要同時讀取2 B數據。

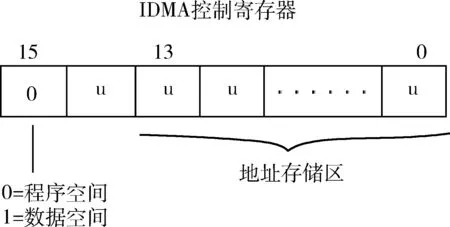

對ADSP2187芯片IDMA接口的讀寫,通過對IDMA的控制寄存器和OVERLAY寄存器的操作來實現。寄存器各位定義如圖3、圖4所示。

圖3 IDMA 控制寄存器

圖4 IDMA Overlay寄存器

對ADSP2187IDMA口的操作需要先對IDMA口控制寄存器和OVERLAY寄存器進行配置,說明需要讀取的數據是程序區還是數據區、在哪個頁面中、地址為多少,然后對總線進行讀寫操作,從而實現對ADSP2187內部存儲區的讀寫。

得益于接口電路的作用,TMS320C6414可以通過對地址0x03200000的操作來實現對IDMA控制寄存器和OVERLAY寄存器的配置,當寫到該地址的數據最高位為1時,對OVERLAY寄存器進行操作,為0時則對控制寄存器進行操作;可以通過對地址0x03100000的讀寫實現對數據總線的讀寫。ADSP2187的程序加載引導邏輯流程如圖5所示。

5 結論

本設計實現了TMS320C6414和ADSP2187兩個DSP芯片共享Flash的程序引導加載,該設計已成功應用于某光電跟蹤裝置上,較好地完成了信息處理程序的加載和引導,工作穩定可靠。本文設計方法為將來其他多DSP共享Flash的信息處理機設計提供了參考,有著重要的實際意義。

[1] 李宏,李偉,李蒙,等.基于多DSP的紅外目標跟蹤系統設計與實現[J]. 電子技術應用,2006,32(8):59-61.

[2] 楊明,趙曉博,狄衛國,等.基于TMS320C6414的大容量存儲器擴展設計[J]. 自動化技術與應用,2008(6):103-105.

[3] 王冬,李登科.基于雙DSP的信息處理機設計[J].國外電子測量技術,2013,32(6):89-92.

[4] 趙熠,景德勝.一種基于雙處理器的信息處理平臺的設計[J].電子技術設計與應用,2015(6):86-87.

[5] 陳誠,陳曉平,王識君.基于DSP+CPLD的電動舵機控制系統的設計[J]. 電子技術應用,2015,41(4):84-86.

[6] 陳勇,賈明永,董德新,等.ADSP2187L在某光電跟蹤裝置中的應用[J].航空兵器,2004(4):22-24.

[7] 梁楷.ADSP-218X的IDMA接口設計[J].網絡財富,2010(21):183.

Design and implementation of program loading for dual DSP shared Flash

Wang Yilin

(Science and Technology on Electro-optic Control Laboratory, Luoyang 471009, China)

Promgram loading and booting for dual DSP system sharing Flash is very complex. This paper takes a research on that issue based on TMS320C6414 and ADSP2187. TMS320C6414 is master processor, and ADSP2187 is co-pocessor. The shared Flash chip is connected to the EMIFB of TMS320C6414, the IDMA of ADSP2187 is connected to the EMIFA. When the system is powered,TMS320C6414 reads the main processing program from Flash chip,then completes loading and booting. Then TMS320C6414 reads the co-program and sends to ADSP2187, and helps it to load and boot the program.

TMS320C6414; ADSP2187; shared Flash; load; boot

圖5 ADSP2187程序引導邏輯流程

國家自然科學基金(61273075)

TP368

A

10.19358/j.issn.1674- 7720.2016.23.009

王怡林. 雙DSP共享Flash程序加載引導設計與實現[J].微型機與應用,2016,35(23):31-34.

2016-08-08)

王怡林(1979-),女,本科,工程師,主要研究方向:光電跟蹤控制。