基于FPGA+DSP實時圖像采集處理系統(tǒng)設計

靖固 楊華宇

摘要:采用FPGA和DSP的結構實現(xiàn)實時圖像采集處理系統(tǒng),利用FPGA運行速度快、并行處理能力強的優(yōu)勢,采用“對數(shù)拉伸”算法對攝像頭采集的數(shù)據(jù)進行前期預處理,達到圖像增強,使得停車場類昏暗光線圖像亮度分布不均勻的圖像變得清晰;利用DsP具有較強處理復雜算法的優(yōu)勢,對FPGA傳送過來的分塊圖像數(shù)據(jù)采用JPEG并行壓縮算法進行圖像的壓縮,實驗結果表明,圖像增強模塊能夠明顯改善圖片質量,F(xiàn)PGA和DSP的結構能夠很好的滿足系統(tǒng)實時性的要求,

關鍵詞:FPGA;DSP;圖像采集;圖像增強;圖像壓縮

DOI:10.15938/j.jhust.2016.04.008

中圖分類號:TP391.41

文獻標志碼:A

文章編號:1007-2683(2016)04-0040-05

0引言

隨著現(xiàn)代技術的發(fā)展和人們對圖像采集處理質量需求的不斷提升,對圖像采集系統(tǒng)的性能和實時性提出了更高的要求,而對于數(shù)據(jù)量大、噪聲干擾嚴重的圖像數(shù)據(jù),采用單個DsP芯片難以滿足系統(tǒng)的性能和實時性的要求,用FPGA對圖像進行預處理并實現(xiàn)對DSP的控制與管理,就可以很好的解決了這類問題,本系統(tǒng)針對停車場類昏暗光線圖像,利用FPGA采用零有效視頻信號提取算法提取出輸入的有效的YUV視頻數(shù)據(jù),采用對數(shù)拉伸增強算法對圖像進行預處理,預處理后的圖像送入到DSP內采用并行JPEG壓縮算法對數(shù)據(jù)進行壓縮,仿真結果表明,圖像增強模塊使昏暗光線圖像明顯增強,數(shù)據(jù)壓縮后使信息傳輸量減少20%,能很好地滿足系統(tǒng)實時陛要求,

1.實時圖像采集處理系統(tǒng)總體結構

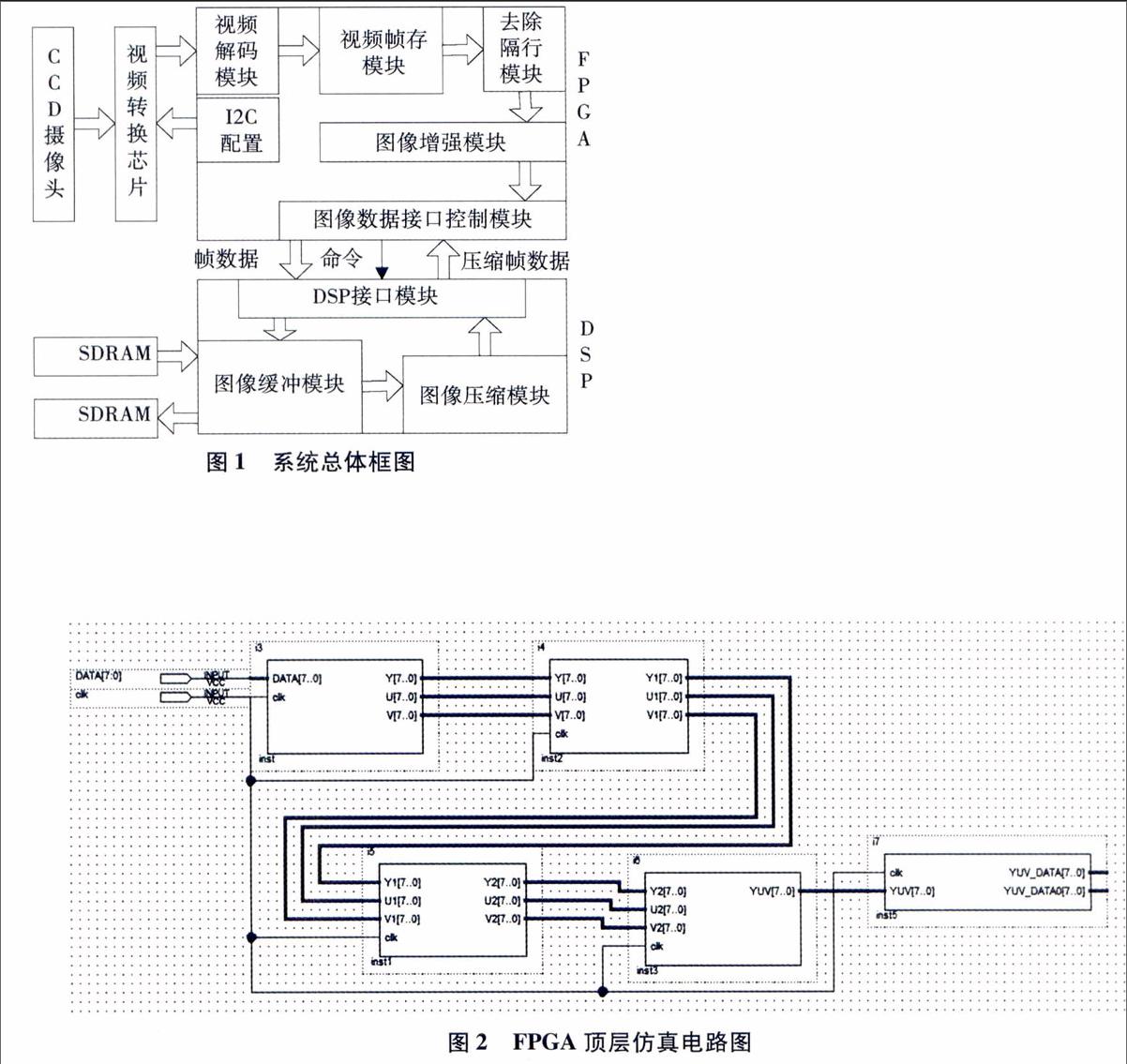

系統(tǒng)總體框圖如圖1所示,系統(tǒng)分為9個模塊,F(xiàn)PGA內包含的模塊有視頻解碼模塊,12C配置模塊,視頻幀存模塊,去除隔行模塊,視頻增強模塊,DSP接口模塊,

DSP芯片內包含的模塊有圖像數(shù)據(jù)接口模塊,圖像數(shù)據(jù)緩存模塊,圖像壓縮模塊,通過CCD攝像頭對視頻進行采集,圖像數(shù)據(jù)送入視頻A/D轉換芯

2.1視頻解碼模塊設計

視頻解碼模塊接受模數(shù)轉換器ADV71781 B的YUV數(shù)字信號,這些數(shù)字信號中包含有場參考信號VS、行參考信號HS和奇偶場信號,要對YUV信號分別進行處理必須從圖像數(shù)據(jù)中提取出有效的Y、u、V數(shù)據(jù),攝像頭采集的數(shù)據(jù)經(jīng)過ADV7181B轉片中,經(jīng)12C總線對視頻A/D轉換芯片初始化,完成控制寄存器的配置,使其上電后進人工作模式;A/D轉換芯片輸出圖像送人視頻解碼模塊,視頻解碼模塊接收A/D轉換的視頻流后對視頻流進行解碼,產(chǎn)生YUV數(shù)據(jù);視頻幀存儲模塊采用乒乓存儲算法結構對YUV數(shù)據(jù)進行存儲,使YUV圖像數(shù)據(jù)轉化成并行數(shù)據(jù);為了增強視頻效果,消除抖動閃爍去除隔行模塊完成采集圖像的奇場幀和偶場幀的合并,由于系統(tǒng)應用于地下車庫監(jiān)控系統(tǒng),采集的圖像數(shù)據(jù)光線以及燈光等原因圖像畫面不清晰,通過圖像增強模塊增強其對比度使圖像清晰;增強后的圖像數(shù)據(jù)通過DSP接口模塊送入DSP芯片內進行壓縮;DSP芯片壓縮處理數(shù)據(jù)量很大,為避免數(shù)據(jù)丟失,圖像數(shù)據(jù)通過DSP內部的接口模塊和圖像緩存模塊緩存到SDRAM中;緩存一幀圖像數(shù)據(jù)后,在DSP內也采用乒乓讀寫操作將數(shù)據(jù)送入壓縮模塊進行壓縮,壓縮后數(shù)據(jù)送回FPGA存儲待發(fā)送。

2.FPGA內部模塊設計

FPGA內部共有5個模塊組成,頂層仿真設計電路如圖2所示,輸人為攝像頭采集的復合信號DATA,時鐘信號elk,輸出為經(jīng)過處理的視頻有效信號和壓縮后傳回FPGA的YUV_DATA、YUV_DA-TA0信號,換后輸出符合ITU—R656的信號DATA,行同步信號HS,幀同步信號VS,DATA的數(shù)據(jù)格式如圖3所示,視頻解碼模塊主要是提取出YUV數(shù)據(jù),即將串行的數(shù)據(jù)轉換為并行的YCrCb數(shù)據(jù),

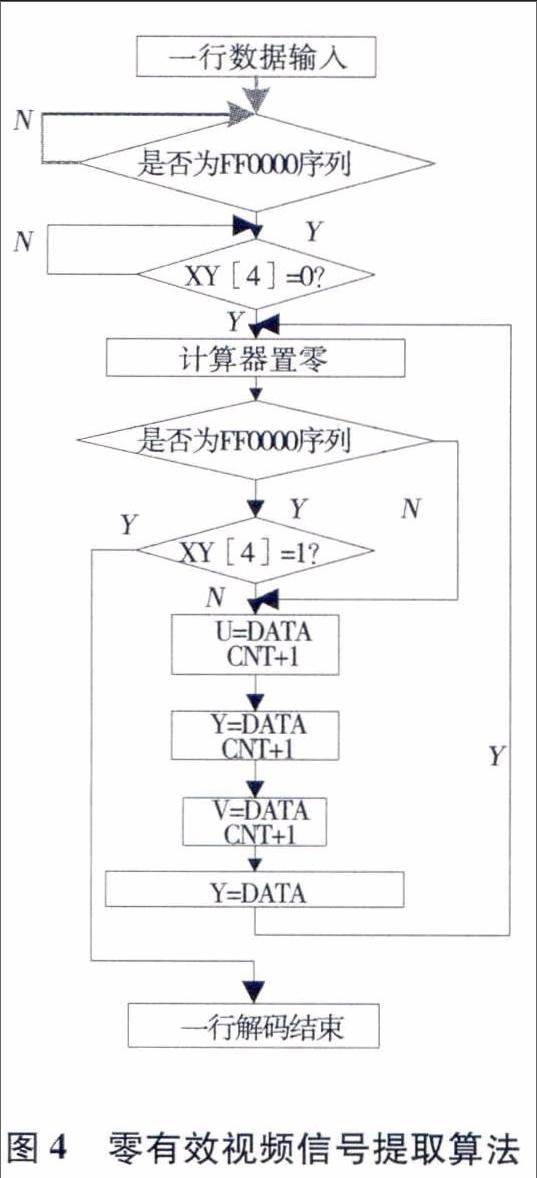

從上圖可以看出AV信號都是以“FF0000”作為開始信號,但SAV的XY[4]=0,EAV的XY[4]

1.利用這點我們構造一個檢測電路來實現(xiàn)YUV數(shù)據(jù)的并行輸出,視頻數(shù)據(jù)提取算法如圖4所示,算法在實現(xiàn)上利用狀態(tài)機完成對“FF0000'數(shù)據(jù)流以及SAV、EAV的識別,識別出有效數(shù)據(jù)后操作設置好的計數(shù)器cnt,算法中YUV數(shù)據(jù)為422格式,當cnt=0時輸出Cb,cnt=1時輸出Y,cnt=2時輸出Cr,cnt=3輸出Y,最終得到YUV有效的視頻數(shù)據(jù),

2.2視頻幀存模塊設計

視頻解碼模塊輸出的YUV信號需要三個緩存器進行緩存,通過軟件自帶的端口RAM的宏模塊把每個緩存定義成雙端口的深度均為1024,每個數(shù)據(jù)端口寬度為8位RAM緩存器,

2.3去除隔行模塊設計

去除隔行模塊采用幀內復制的方法,具體實現(xiàn)方法就是改變視頻幀存模塊中雙端口RAM的讀寫時鐘,使讀時鐘是寫時鐘頻率的兩倍,這樣每行的數(shù)據(jù)讀兩遍,隔行數(shù)據(jù)就變成了逐行數(shù)據(jù),

2.4圖像增強模塊設計

2.4.1圖像增強算法

地下車庫的燈光相對較暗,往來進出的車輛很多而且都開著大燈,在圖像中顯示結果為車燈的部分特別亮,使得周圍的圖像模糊不清,從灰度值方面來說,灰度值為O~125之間和200~255之間的像素特別集中,這時如果直接使用原圖,則圖中的一部分低灰度細節(jié)可能會丟失,由于原圖的灰度動態(tài)灰度值分布范圍不均勻,可能大于顯示設備允許的范圍,使得原圖的一些灰度級顯示不出來,為此將地下車庫的采集圖像做灰度映射,使原圖的動態(tài)灰度值分布變得均勻,對數(shù)形式的壓縮算法可以很好地解決此類問題,其原理為:

利用上式可將原來動態(tài)范圍很大的s轉換為動態(tài)范圍較小的t,從圖5中可以看出,大部分低灰度值的像素經(jīng)過映射后其灰度值會集中到高亮度區(qū)段,總體來說就是同時增大圖像的亮度,對于原來灰度值小的增亮的幅度大些,原灰度值大的增亮的幅度小些,從而達到圖像亮度均勻,細節(jié)不模糊的效果,

2.4.2圖像增強模塊硬件結構設計

圖像增強主要針對于亮度信號,也就是YUV信號中的Y路信號,去除隔行模塊輸出的是YUV三路并行的8位信號,因此在增強模塊中還要保證u、V兩路信號的同步,為此采用與之前模塊同樣的方式設置三個寬度為8位,深度為1024的FIFO,增加一個檢測電路使三路信號完成并行轉換到串行,使輸出給接口控制模塊的數(shù)據(jù)為單路8位寬的有效圖像數(shù)據(jù),從后面仿真對比圖可以看出經(jīng)過圖像增強模塊后圖像對比度明顯增強,從圖6的a)圖可以得出整個處理過程共需O,17 ms,而從b)圖可以看出在MATLAB軟件上完成的時間為1,7s,

2.5接口控制模塊設計

FPGA內部的接口控制模塊通過一個時鐘鎖相環(huán)來控制,F(xiàn)PGA和DSP的數(shù)據(jù)通信接口如圖7所示,為了將處理后的視頻數(shù)據(jù)并行處理,采用8個FIFO寄存器將視頻數(shù)據(jù)進行分塊,第9個FIFO用來接收DSP送回的壓縮數(shù)據(jù),視頻數(shù)據(jù)采集、處理完成之后,F(xiàn)PGA通過FIF08的空信號(empty flag)查看8個FIFO中是否數(shù)據(jù)已滿,如果未滿,則將數(shù)據(jù)在寫時鐘的邏輯控制下,順序寫入到FIFO中;同時將FIF08中滿信號連接到DSP的中斷引腳,滿信號置高,會觸發(fā)DSP的DMA進程,將寄存器中數(shù)據(jù)讀走,DSP壓縮一幀數(shù)據(jù)完成后通過EMIF接口將數(shù)據(jù)送回FPGA。

3.DSP內部設計

3.1圖像壓縮并行算法

為了達到實時性的目的對預處理后的圖像進行并行JPEG壓縮處理,JPEG壓縮編碼主要由預處理、DCT變換、量化、Huffman編碼等流程構成,如圖8所示,

JPEG壓縮編碼時,需先將原始的二維圖像分成8×8的數(shù)據(jù)塊并行處理,然后將各數(shù)據(jù)塊按從左到右,從上到下的順序分別進行DCT變換、量化、“之”字型(Zig-Zag)掃描和Huffman編碼,分別需要量化表和Huffman編碼表的支持,將8×8數(shù)據(jù)塊的DCT轉換為16次一維8點DCT變換,只要提高一維DCT的速度就可以提高二維DCT的速度,利用DSP的專用指令乘累加運算來優(yōu)化DCT算法,DCT變換和Huffman編碼采用和傳統(tǒng)算法一樣的實現(xiàn)方法,用C語言和匯編語言在DSP內部實現(xiàn),

與傳統(tǒng)JPEG算法在DSP芯片上實現(xiàn)有所不同的是,在圖像壓縮模塊中并沒有進行對二維圖像的分塊處理,DSP壓縮模塊接受的是經(jīng)過FPGA分塊處理后的圖像數(shù)據(jù),DSP在經(jīng)過緩存后可以直接對其進行后續(xù)的壓縮處理,這樣既提升了整個系統(tǒng)的處理速度,更好的滿足實時性,又減少了DSP對存儲器的調用,

3.2圖像壓縮結果

經(jīng)過DSP芯片壓縮后的數(shù)據(jù)通過與FPGA接口模塊傳送回FPGA,最終存儲或顯示出來,由圖9(a)(b),可以明顯看出比原圖像更加清晰,由圖9(c)可以看出壓縮后盡管有一些失真,但還是保留了原圖像的細節(jié),達到了要求,

5.結論

利用FPGA和DSP結構能很好地解決圖像采集系統(tǒng)的實時性要求,針對昏暗場所的圖像數(shù)據(jù)采用“對數(shù)拉伸”算法,可有效增強圖像,使得亮度分布不均勻的圖像變得清晰;采用并行JPEG壓縮算法在FPGA發(fā)送數(shù)據(jù)前對二維圖像進行分塊,減少了處理時間;JPEG壓縮雖為有損的圖像壓縮算法,但能使信息傳輸量大大減少的同時有效地保留原始圖像的細節(jié),達到預期處理目的。