一種12bit流水線型模數轉換器的研究與設計

劉 洋

(天津維晟微科技有限公司,300457)

一種12bit流水線型模數轉換器的研究與設計

劉洋

(天津維晟微科技有限公司,300457)

本文設計和研究了一種低功耗12Bit 流水線模數轉換器的結構,其采用了TSMC 0.18um工藝設計,3.3V單電源電壓,5MHz采樣率,動態(tài)范圍為1V,INL為0.5LSB,DNL為2LSB,通過詳細的電路原理分析和軟件Cadence的仿真,并流片測試,性能達到設計初衷。

流水線型模數轉換器(Pipeline ADC);子數模轉換器(Sub-DAC);子數模轉換器(Sub-ADC);余數放大器;MDAC

在大多數的通訊系統中,通常都會應用DSP或MCU數字模塊來處理通訊信息,這種方式必然要求要將模擬信號轉換成可識別的數字信號,也就是需要通過模數轉換器(ADC)來實現。今天,隨著對無線通訊系統的需求爆發(fā)式的增長,對ADC的需求也越來越大,而ADC的高速,低功耗等性能將直接影響通訊系統這方面的指標。

1 Pipeline ADC 系統原理

PipelineADC 主要由采樣保持電路(SH),子數模轉換器(Sub-DAC),子模數轉換器(Sub-ADC),余數放大器,數字校準電路組成,其中最核心的為子級轉換電路MDAC,MDAC是Sub-DAC,余數放大器,減法器組成,它的功耗,精度,速度,將直接影響整個ADC系統的性能。由于本設計用于通訊系統,為了增強抗干擾能力,本設計選擇了差分輸入的電路結構,這樣可以有效的抑制信號的共模噪聲,在功耗方面,在對比了通用的1.5Bit與2.5Bit的 MDAC電路結構后,本設計采用了2.5Bit的結構,使其原本需要9級的stage電路,減少為目前的5級,

流水線模數轉換器工作原理如下:

差分信號經過第一級SH電路,也就是采樣保持電路,將輸入模擬信號采樣,并將其從進第一級stage電路,由stage電路中的子Sub-ADC量化,得到第一級的數字碼,再將得到的數字碼送入Sub-DAC,將其還原成模擬信號值,最后通過最初采樣而來的模擬信號減去sub-DAC的輸出值,所得到的信號幅度差再經過余數放大器放大4倍,傳輸給第二級stage電路,作為第二級的輸入信號,以此類推,當信號經過所有5級stage電路后,會相應的得到所有的數字碼,這些數字碼再經過數字糾錯邏輯和延遲邏輯單元,進而得到并行的12Bit的數字輸出,完成一次模數轉換。

由上述工作原理可知,流水線模數轉化器由多級stage電路組成,每一級都由子Sub-ADC和子Sub-DAC以及余數放大器組成,盡管由系統決定了其中的Sub-ADC和子Sub-DAC的分辨率并不高,但多級stage并行工作的特性卻使流水線模數轉換器的速度得到了優(yōu)化和提升,可以使ADC系統得到很高的分辨率和信號的轉換速度。

2 模塊設計

2.1MDAC模塊設計

在流水線模數轉換器的整個轉換過程中,除了一開始的模擬信號需要經過SH電路進行采樣保持外,并輸入第一級stage電路意外,其余各級的輸入信號都是由上一級的輸入信號保持并減去上一級Sub-DAC的輸出信號,并通過余數放大器的4倍增益得來的,實現數模轉化,減法以及4倍放大的功能,統稱為MDAC,MDAC由Sub-DAC,余數放大器,減法器組成,它使得各級在處理信號時互不干擾,相對工作獨立,也是它的這種特性,使得整個流水線模數轉換器系統得以較快的速度與較大的分辨率。由此可以看出,MDAC的性能將直接決定整個系統的性能,本設計MDAC采用了開關電容電路結構,

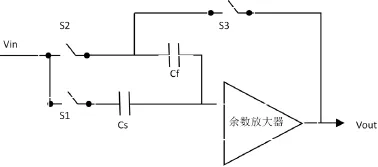

工作原理如下,因為本設計采用差分的結構,如下示意原理圖采用單端示意來說明工作原理

如上圖所示,S1,S2,S3,為mos開關,根據不同開關的閉合和斷開, MDAC分為兩個信號處理的階段,分別為信號的采樣與保持,

第一階段,開始信號的采樣,其中S1,S2,閉合,S3斷開,在Cs和Cf上的電荷總數為Qvin=Vin·Cs+Vin·Cf,

第二階段,將S1,S3閉合,S2斷開,此時,信號輸入為Vref信號,此時在Cs和Cf上的電荷總數為Qref= Vref·Cs+Vout·Cf,根據電荷守恒的原理,Qvin=Qref

可得以下結論

Vout=(1+)·Vin-Vref·

由于本設計采用的是2.5Bit的分級結構,即其中Cs=3Cf,這個比例實現了實現了減法器和對信號相減后差值放大4倍的功能。

2.2余數放大器設計

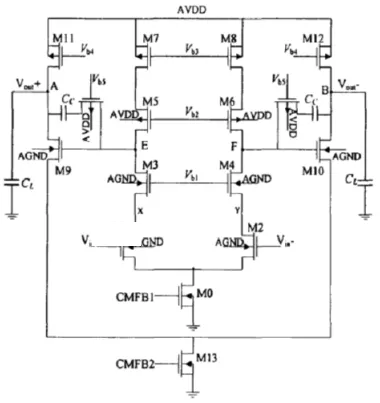

要實現MDAC的功能,其中的余數放大器是其中的關鍵,本系統對放大器的帶寬,功耗,增益等性能指標有較高的要求, 所以對放大器的結構選取也提出了更高的要求,通過對目前常用的為套筒式共源共柵運算放大器,折疊式共源共柵運算放大器,兩級型預算放大器,高增益運算放大器四種結構的性能比較,根據本系統的指標以及對運算放大器的各項關鍵指標的綜合考慮,本設計選擇如下結構,

本運算放大器主要由輸入級,輸出級和密勒補償構成,其中,輸入級采用了傳統的套筒式結構,此結構有著高速低功耗,以及中等輸出擺幅的特點,其中M1和M2為差分輸入NMOS管,M0為電流鏡像NMOS管,為整個輸入級提供電流,M3-M4為NMOS負載管,M3-M8為PMOS負載管,M3-M8提高了M1和M2的輸出阻抗,使其獲得了較高增益,輸出級采用了共源級輸出以獲得較大的電流驅動和輸出擺幅,其中M9,M10為PMOS差分輸出,密勒補償電容Cc采用了零極點抵消的方法,使得運算放大器獲得最大限度的單位增益帶寬和相位裕度,本運算放大器的0dB帶寬為101MHz, 相位裕度為52deg,另仿真電流為369uW,完全符合系統的指標要求

2.3子模數轉換器(Sub-ADC)設計

子模數轉換器存在于每一級stage電路模塊中,其是將采樣信號進行量化,再將量化過后的數字碼輸出到MDAC,再由MDAC進行處理,將其還原成模擬信號值,最后通過最初采樣而來的模擬信號減去sub-DAC的輸出值,所得到的信號幅度差再經過余數放大器放大4倍,傳輸給第二級stage電路,作為第二級的輸入信號,Sub-ADC是通過比較器陣列來實現對采樣信號的量化的,本文采用的2.5Bit的結構, 比較器陣列由6個比較器組成,分別對±Vref,±Vref,±Vref,6個固定電平進行比較,并將比較結果進行邏輯處理后,輸出到MDAC,還原成模擬信號,再進行減法和放大的處理,由上述原理可知,比較器是子模數轉換器的關鍵模塊

2.3.1比較器模塊設計

比較器一般常用的分為兩種,一種是Latch比較器(非連續(xù)時間比較器),一種是運放型比較器(連續(xù)時間比較器),其中運放型比較器比較精度高,但速度較慢,且功耗較大,Latch比較器速度較快,功耗低,但精度不高,根據流水線模數轉換器的原理,其對比較器的速度和功耗要求較高,但對精度要求不高,只需控制在150mV范圍內即可,所以,本設計采用了Latch比較器的結構。

3 回片流片測試結果

本設計使用Cadence,Hspice電路設計軟件,采用TSMC 0.18um工藝設計,并進行流片回片測試

流片回片測試結果

測試所需儀器

對信號發(fā)生器的需求:因為設計指標為12bit ADC ,所以信號源提供的信號信噪比必須要高于12bit,基于此要求的考慮,在本次回片測試中,本文選擇了信號發(fā)生器:Agilent 81150,其可提供信噪比SNR為90dB,14bit精度的信號。

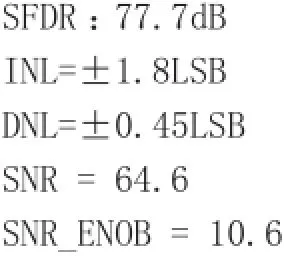

測試方法,由電壓源提供3.3V電源電壓,由信號發(fā)生器提供幅值為1V,頻率為500k的正弦輸入信號,AD采樣頻率4.8MHz,通過邏輯分析儀對回片的輸出16384(2的14次方)個點進行采樣記錄,再將數據導入MATLAB進行fft的計算,得出以下結論

5 結論

本文采用了TSMC 0.18 CMOS工藝,設計了一款12bit,5M采樣率的流水線模數轉換器,電路中采用了分級2.5Bit結構,功耗為2mW,經流片回片測試,實際有效位為10.6bit,完全符合設計初衷

劉洋(1978.3.5)男,漢族,碩士,籍貫:遼寧凌海市,天津維晟微科技有限公司中級工程師,研究方向;自動化

A 12 bit pipeline module is installed in the research and design

Liu Yang

(Tianjin d sheng micro technology co.,LTD,300457)

This paper study and design a kind of low power consumption structure of 12 bit pipeline adc, the adopted TSMC 0.18 um process design, single power supply voltage of 3.3 V,5 MHZ sampling rate and dynamic range of 1 V, INL 0.5 LSB, DNL is 2 LSB, through detailed analysis of the circuit principle and software simulation, Cadence and flow testing, performance meet the design intent.

Pipeline ADC (Pipeline ADC);child digital-to-analog converters(Sub - DAC);analog-to-digital converter(ADC);Sub - MDAC remainder amplifier

[1]李福樂.適宜于系統集成的高速高精度模數轉換電路設計技術研究.清華大學博士學位論文,2003.

[2]龔川 CMOS圖像傳感器中高速,低功耗 Pipelined ADC設計與優(yōu)化.天津大學碩士學位論文,2006.