高集成C波段小型化收發電路的研制

米多斌 厲志強 李靜強

(中國電子科技集團公司第十三研究所,河北 石家莊 050051)

高集成C波段小型化收發電路的研制

米多斌 厲志強 李靜強

(中國電子科技集團公司第十三研究所,河北 石家莊 050051)

本文基于GaAs多功能MMIC高集成度的優勢,采用多層LTCC工藝技術研制了一種小型化C波段收發電路。討論了系統方案的優化設計,建立了各單元電路的參數化模型。在此基礎上采用局部電磁場優化仿真和全局電路系統仿真相結合的設計方法,對收發電路的各項指標進行了優化仿真分析。該電路性能優良,接收增益大于32dB,噪聲系數小于1.4dB,駐波小于1.5,發射功率大于39dBm,電路模塊尺寸為30mm×30mm×8mm,且內部集成了收發電源調制電路、幅相及收發控制電路、電源保護電路等,集成度提高的同時,其體積大幅度減小。

收發電路;小型化;高密度集成;MMIC;LTCC;微組裝技術

0. 引言

近年來,隨著微波單片集成電路(MMIC)和多芯片組裝(MCM)技術的發展與應用,T/R收發電路的發展趨于小型化、輕量化、高集成。國內已陸續研制出了一系列高性能的MMIC器件,MCM工藝技術也逐步發展成熟。因此,基于MMIC器件及MCM工藝技術的復雜電路及系統研究成為電路設計的重要課題。系統級封裝(SIP)利用微組裝和三維互聯技術,可將各種GaAs電路、CMOS電路等有源集成電路以及電容、電阻、濾波器等各類無源器件集成到一起,實現功能復雜電路的小型化。

低溫共燒陶瓷技術(LTCC)是實現系統級封裝的一種較為理想的高密度組裝技術,材料介電常數適中,信號傳輸線采用Au、Ag等良導體,具有損耗小,微波性能好等優點。它采用多層層疊技術可對微波傳輸線、邏輯控制線及電源線進行混合布線設計,并且可將電容、電阻等無源元件集成在多層微波電路基板中,最大限度地減小電路的體積、重量和元器件數量,提高系統性能和可靠性,降低成本。同時,基于LTCC的多芯片系統可以采用氣密封的金屬封裝,滿足苛刻環境條件下使用。因此,基于LTCC工藝技術研制的微波電路具有高密度集成、多種電路功能和高可靠性等技術優勢。

本文介紹的C波段小型化收發電路,在采用LTCC及多芯片組裝技術的基礎上,利用自主研制的GaAs幅相一體多功能MMIC,進一步減小了電路的體積。

1. 收發電路的原理及組成

T/R收發電路作為射頻收發系統前端,在整個系統中起到至關重要的作用。一般是由一接收支路和一發射支路組成,原理框圖如圖1所示。天線接收到的微弱射頻信號進入其接收通道,經過放大,以一定的幅度及相位輸出,進入后級處理。系統對接收前端的基本要求是:較低的噪聲系數,一定的小信號增益,足夠的抗電磁脈沖能力,足夠的帶寬和動態范圍等;經過前級處理的發射信號進入電路發射通道,經過信號放大,以足夠大的功率及相應的相位輸出至天線,由天線輻射到整個空間。系統對發射前端的基本要求是:較高的發射功率,穩定的幅頻特性,足夠的帶寬等。

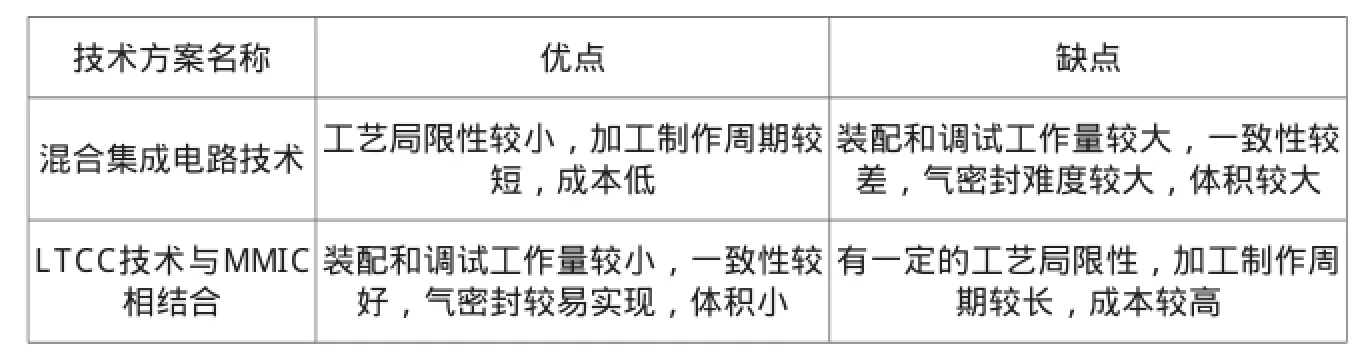

針對目前收發電路小型化和高集成的要求,對常規的采用混合集成電路的技術方案和先進的LTCC與MMIC相結合的技術方案進行對比,其優缺點見表1。

表1 兩種技術方案對比分析

由此可見,LTCC技術與MMIC相結合的技術方案更有利于收發電路的小型化,且有利于提高可靠性及適于大規模生產。因此,采用該技術方案進行收發電路的設計。為進一步提高收發電路的集成度,采用自主研制的GaAsE/D多功能芯片,將其射頻通道主要功能芯片由通常的8片式結構縮減至3片,如圖2所示。該多功能芯片上集成了T/R開關、數控移相器、衰減器、兩級放大器及驅動器。其中,數控移相器、衰減器、兩級放大器為收發共用,由3個單刀雙擲開關完成收發通道的切換。

2. 收發電路的設計

2.1 TR電路及器件建模分析

電路仿真首先需要提取各個元器件的參數化模型。在TR電路模型中,主要分為三大類模型,包括無源元件模型、低噪放電路模型、功放電路模型。無源元件又包含微波開關、幅度均衡器、衰減器、移相器、濾波器等元件。其中無源元件模型參數主要包括插入損耗、端口駐波及隔離度等,這些參數均可用小信號S參數表征;而放大器模型參數主要包括線性增益、噪聲系數、端口駐波、1dB壓縮輸出功率或飽和輸出功率、效率、諧波及三階交調等,除了小信號S參數外,還需要用大信號X參數來表征。

2.2 功放負載牽引仿真設計

常規的微波電路系統中,所有連接微波器件的信號端口均匹配到50Ω,但是對于功率放大器,為了得到最大輸出功率,其主要工作在飽和區,進入非線性區后S參數會隨著輸入信號的增大而不斷變化。這使得阻抗匹配變得較為困難。所以,需要利用負載牽引(Load-Pull)原理找出功率放大器獲得最大輸出功率時對應的負載阻抗ZL,再根據該負載阻抗ZL設計外部的匹配網絡,使阻抗過渡到50Ω信號端口。

針對該收發電路的功率及效率需求,建立功率放大器的負載牽引模型,如圖3所示。經過仿真,選取固定的幾個頻率點,在史密斯圓圖(Smith chart)上,對于某個給定的輸入功率值,得出不同負載阻抗時的等輸出功率曲線和等附加效率曲線,圖4給出了功率放大器在f0頻點時的等輸出功率曲線及等功率附加效率曲線。可以看出,最大輸出功率Pout=39.12dBm對應的負載阻抗值ZL1=58.764+j*9.585,而最高功率附加效率η=38.66%對應的負載阻抗值ZL2=30.289+j*4.902,二者偏離甚遠。因此,需要在各頻點的最大輸出功率和最高功率附加效率對應的負載阻抗之間進行折中考慮,得到最佳外部負載阻抗。

2.3 局部電路的電磁場仿真分析

在整個收發電路中,除上述有源和無源電路模型外,還需要對其微波不連續及較為敏感的局部區域進行三維電磁場仿真分析及優化,如鍵合引線過渡區域、微帶到同軸轉換、帶狀線、輸入/輸出阻抗匹配等,仿真模型如圖5所示。

根據電磁場優化仿真結果的S參數,建立局部電路的參數化模型,將其與MMIC芯片等元器件的參數化模型一起代入系統中進行仿真,從而對整個電路做出更準確的評估。

3. LTCC基板設計和電路制作

該小型化收發電路采用10層LTCC基板,基板材料為Frrro A6M,介電常數5.9,損耗角正切0.002。布線采用的工藝最小線寬、線間距均為100μm,孔直徑150μm,電阻漿料方塊電阻選擇10Ω/□、100Ω/□和1kΩ/□3種,控制精度基板內部為±20%,表面為±5%。LTCC底部要求整板焊接,通孔填充材料為導電金漿,以保證電導率和可靠性。基板設計遵循電磁兼容的原則,對電源層和信號層分層設計,層間由網格地進行電磁屏蔽。此外,還對LTCC基板進行了減小應力的圓弧角設計和防止焊接“析金”的阻焊設計。

收發電路內部采取微組裝工藝進行裝配,封裝外殼使用適合激光密封的新型材料硅鋁CE11,其線熱膨脹系數與LTCC基板相匹配,功放芯片共晶燒結在高導熱率的鉬銅載體上,并直接釬焊在封裝外殼上,一方面提高了功放芯片的散熱效率,另一方面便于拆卸返修。其余MMIC芯片、控制及調制CMOS芯片采用導電膠粘接工藝裝配于LTCC基板或封裝外殼上。圖6為C波段小型化收發電路實物照片,體積為30mm×30mm×8mm。

4. 測試結果及討論

對微組裝完成的收發電路進行了測試,并將測試結果與仿真優化結果進行了對比分析。圖7(a)、(b)、(c)分別給出了接收通道小信號增益、噪聲系數、發射通道飽和輸出功率的對比結果。由圖7(a)可以看出,接收通道增益在應用頻帶內大于32dB,且測試與仿真結果吻合較好,最大誤差0.6dB;同樣由圖7(b)可見,噪聲系數在應用頻帶內小于1.4dB,最大誤差小于0.2dB。這主要是由于LTCC工藝誤差及裝配工藝誤差所致。

在規定的脈沖周期和占空比條件下,對發射通道進行測試,結果如圖7(c)所示。發射通道飽和輸出功率在應用頻帶內大于39dBm,且個別頻點的測試值大于仿真結果,最大誤差約0.2dB。這主要是由于在負載牽引仿真時,各頻點最大輸出功率匹配對應的負載阻抗不同,而且要兼顧功率附加效率,導致個別頻點的輸出匹配稍差,而鍵合線的仿真和實際狀態也存在一定差異,最終導致誤差的形成。

此外,經測試接收通道駐波小于1.5,功率附加效率大于33%,收發通道RMS移相誤差均小于2°,主要技術指標均達到要求,且和仿真結果吻合較好。隨著電路系統日趨復雜,元器件越來越多,這種局部電磁場優化仿真和全局電路系統仿真相結合的設計方法表現出了巨大的優越性,在設計中應繼續探索應用。

結論

本文設計并制作完成了基于GaAs多功能MMIC和LTCC的C波段小型化收發電路。首先采用小信號S參數和負載牽引法對各單元電路進行建模,并對較為敏感的電路結構建立三維電磁場模型進行優化設計,在此基礎上對整個收發電路的增益、噪聲、駐波及功率等指標進行了優化仿真分析。該收發電路采用多層LTCC工藝技術實現,并充分利用GaAs多功能芯片高集成度的優勢,極大地減小了收發電路的體積,并提高了可靠性。通過優化設計及實驗驗證,該小型化收發電路具有良好的電性能指標,且電路仿真與實測結果基本一致,具有較好的推廣應用價值。

[1]胡楊,蔡堅,曹立強,等.系統級封裝(SIP)技術研究現狀與發展趨勢[J].電子工業專用設備,2012(11):1-6.

[2]劉秀博,吳洪江.MMIC在T/R組件中的應用[J].半導體技術,2015(11):810-814.

[3] Ahmad M, Nagar M, Xie W, et al. Ultra large System-in-Package(SIP)module and novel packaging solution for networking applications[C]. Electronic Components and Technology Conference(ECTC), 2013 IEEE 63rd. 2013: 694-701.

[4]過方舟,徐銳敏.系統級封裝關鍵技術研究進展[J].微波學報,2014,S1(6):588-593.

[5]楊邦朝,胡永達.LTCC技術的現狀和發展[J].電子元件與材料,2014(11):5-9.

[6] KULKE R, KLEIN T, MOLLENBECK G, et al. Verification of an LTCC packaging technology on board of the ongoing TET-1 satellite mission[C]. Microelectronics Packaging Conference . 2013, 7(6): 1-6.

[7]許立講,鄭偉,嚴偉.基于LTCC微波多層基板的雙面微組裝技術研究[J].現代雷達,2014,36(10):682-685.

[8]劉曉莉,于明紅.基于LTCC技術的大延遲收發組件[J].現代電子技術,2015,15:66-68.

[9] Block C., Hang P., Hoffmann C., LTCC technology for system in package solutions[C]. Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems. San Diego,California, USA, 2006: 4-7.

[10]胡明春,周志鵬,嚴偉.相控陣雷達收發組件技術[M].國防工業出版社,2010.

[11] Valeria Vadalà, Antonio Raffo, Sergio Di Falco, et al. A load-pull characterization technique accounting for harmonic tuning[J]. IEEE Transactions on Microwave Theory and Techniques, 2013, 61(7): 2695-2704.

[12]徐鑫.LTCC毫米波集成傳輸線的過渡及寄生模式的分析與建模[D].成都:電子科技大學,2009.

TN859

A