一種高速數據存儲系統的優化設計

尉易慶,吳利兵,任勇峰,2*,賈興中,劉興俊(.中北大學電子測試技術國家重點實驗室,太原0005;2.中北大學儀器科學與動態測試教育部重點實驗室,太原0005;.晉中職業技術學院,山西晉中00600)

一種高速數據存儲系統的優化設計

尉易慶1,吳利兵3,任勇峰1,2*,賈興中1,劉興俊1

(1.中北大學電子測試技術國家重點實驗室,太原030051;2.中北大學儀器科學與動態測試教育部重點實驗室,太原030051;3.晉中職業技術學院,山西晉中030600)

針對記錄器高速存儲的需要,對基于FPGA和NANDFLASH的高速數據存儲系統進行了優化設計。該設計通過采用交替雙平面的編程方式,對存儲器的存儲速率進行了優化,使存儲速率達到單片Flash最高存儲速率的兩倍,即60Mbit/s;采用雙絞線和電纜延展芯片組,對傳輸質量進行優化;采用邊擦除邊寫入的方式對存儲邏輯進行了優化。在器件選擇方面,采用LVDS構成接口電路,FPGA控制邏輯電路。該優化設計的可行性和可靠性已通過工程實踐驗證。

FPGA;高速存儲;LVDS;邏輯設計;

高速數據采集系統目前在航天工程中已得到廣泛應用,尤其在衛星工程中的應用更為廣泛[1]。怎樣實現數據實時、高速可靠的傳輸到存儲設備中,成為一個關鍵性問題。

1 總體方案設計

本系統包括電源模塊、主控模塊和存儲模塊。存儲模塊設計作為存儲器的核心組成部分,由中心邏輯控制芯片FPGA,接口電路,配置芯片E2PROM,LVDS均衡器、LVDS解碼器、存儲芯片Flash以及 60 MHz晶振等構成。FPGA通過對LVDS高速接口以及數據的發送和接收來實現邏輯控制[2]。LVDS數據經均衡器、解碼器轉換后傳送給FPGA,FPGA對其緩存處理后,寫入Flash芯片;通過接口串聯電阻保護電路對存儲器數據進行回收;電源模塊為整個電路提供電源,工作時鐘由60MHz晶振提供。

原理框圖如圖1所示。

圖1 高速存儲系統組成原理框圖

2 高速數據存儲系統的優化設計

2.1存儲速率的優化

NANDFLASH以其非易失性、低功耗和單片容量大等優點被廣泛應用于固態存儲器[3]。但由于其基于頁編程、塊擦出進行操作的特點,使其在運行期間其他的相關操作得不到響應,從而大大降低數據存儲速度。

圖2是分時加載方式示意圖。在完成平面1的數據加載之后,平面2的數據加載即開始進行,而此時平面1進入自動編程時間,與平面2操作互不干擾。平面1、平面2、…平面n依次往下進行。在平面1自動編程完成后,再次對平面1進行數據加載,如此循環,使得數據源源不斷地輸入到芯片之中,極大地提高了數據的寫入速度。

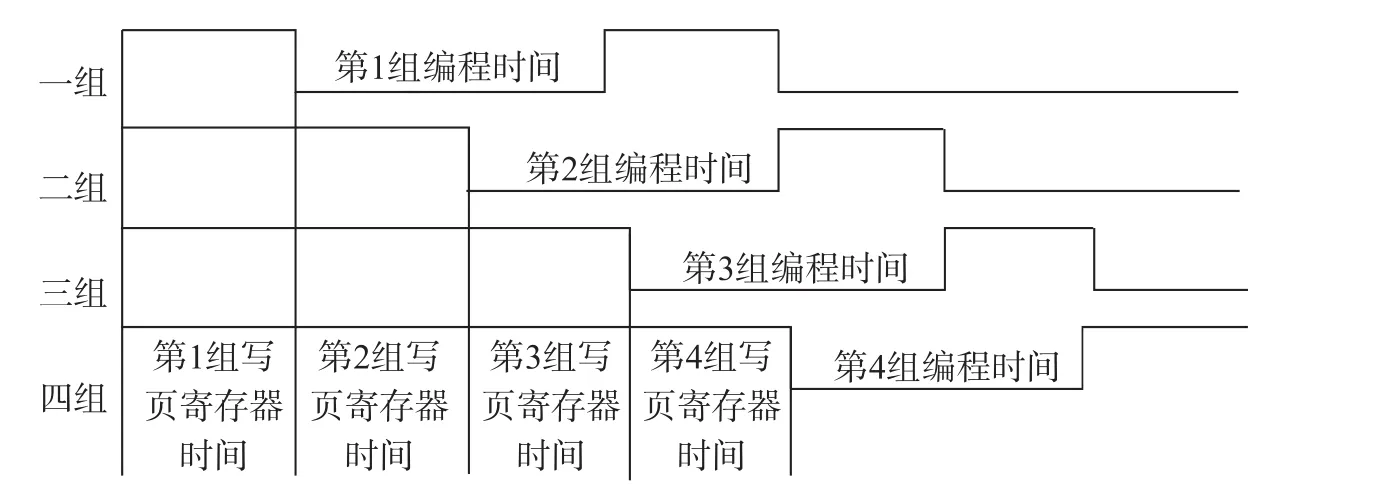

圖3為雙平面交替存儲法[4,5]。這種方法是利用流水線操作思想,分步逐個陣列地完成整個存儲,先完成第1組頁寄存器存儲,等待它進人頁編程時間之后再進行2組、3組、4組的頁寄存器存儲,這樣1組、2組、3組、4組來回交替,就可以高速地完成整個存儲任務。對圖3各個時間進行計算,分析:

第1組加載完成所需頁編程時間約為200μs,此時對 2組~4組加載,加載時間為 Tjiazai=[2(4 kbyte×t+7t)+tDBSY]×3=823.2μs;其中,t=1/30Mbyte/s,tDBSY為1μs等待時間。由此看出,當2組~4組完成加載時,第1組已經完成編程,可以繼續加載。1組~4組的加載時間 T=[2(4 kbyte×t+7 t)+tDBSY]×4= 1 097.6μs,單片 NANDFLASH最大存儲速率為4 096×8 byte/1 097.6μs=29.85 Mbyte/s。采用兩片NANDFLASH并行存儲,存儲速度可達59Mbyte/s。由此可滿足高速數據存儲系統設計要求。時序如圖4所示。

圖2 分時加載方式示意圖

圖3 交替雙平面編程方式示意圖

圖4 交替雙平面編程時序示意圖

2.2存儲邏輯的優化

FLASH的數據存儲可以是先全部擦除,再進行數據寫入。如果FLASH的擦除由手工完成,則記錄數據量需小于FLASH容量;如果自動擦除,全部擦除耗費時間過長,可能會導致連續的待存儲數據丟失[6]。設計邊擦除邊寫入的方式可以有效的解決以上問題,擦除一塊,存儲一塊,以此往復,不僅滿足了數據的自動循環擦寫,也保障了記錄數據的完整性。圖5為存儲邏輯流程圖。

圖5 存儲邏輯流程圖

2.3傳輸質量的優化

在遠距離傳輸高速數據時,高速信號在傳輸介質中的衰減是存儲數據產生誤碼的原因之一[7,8]。因此在高速數據進行較遠距離傳輸時,為保證其傳輸質量,通常采用信號調理技術來針對特定數據速率和傳輸介質,LVDS傳輸時通常采用均衡加重技術。對此,可以在信號發送端采用信號驅動器,接收端采用信號均衡器,以實現信號的長距離穩定傳輸。

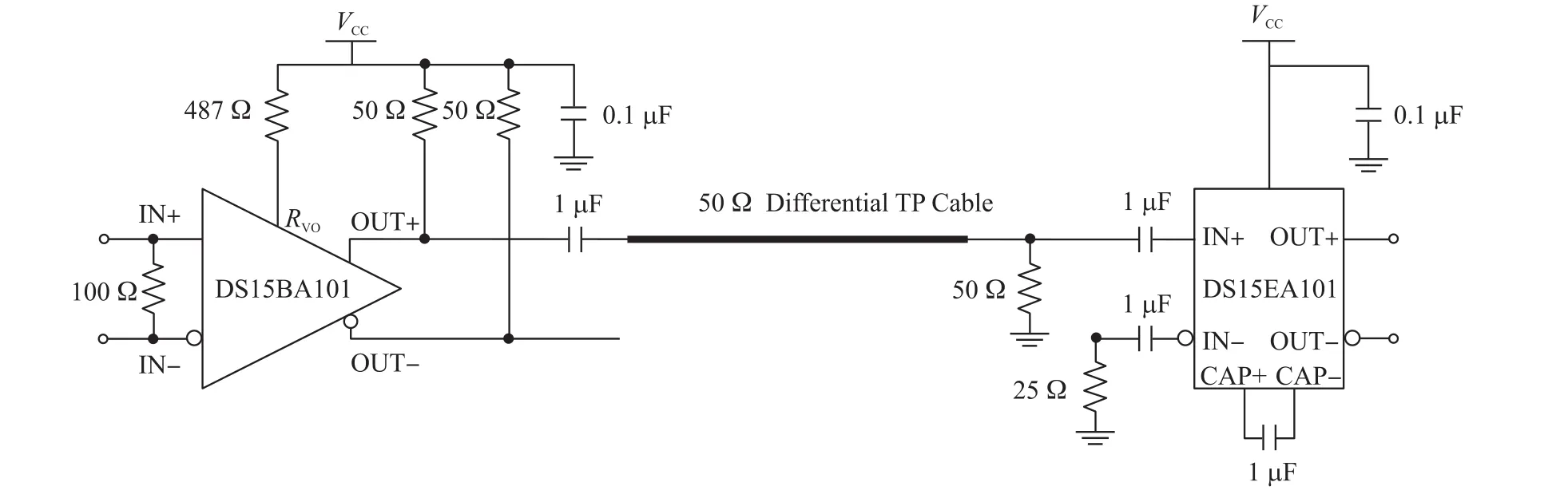

DS15BA101和DS15EA101電纜延展器芯片組可以通過雙絞線及同軸電纜驅動來自FPGA芯片的串行數據流。DS15BA101是一種高速差分緩沖器,可以用于電纜驅動,信號緩沖和轉發等功能;DS15EA101是一種自適應均衡器,可以優化在同軸、雙絞線電纜中傳輸的均衡數據,速度可達150 Mbit/s至1.5Gbit/s。發送器或電纜終端驅動器的信號幅值(發射幅值)決定了自動均衡電路DS15EA101的性能,100Ω差分電纜(雙絞線電纜)的最佳發射幅值是±400mV(800 Vp-p),50Ω的同軸電纜的最佳發射幅值也是800mV[9]。DS15EA101的能量檢測電路能夠對輸入的信號能量進行量化,并將其反饋給自動均衡控制電路。自動均衡控制電路對原始信號和反饋信號進行比較,并根據比較結果來控制均衡濾波器,使信號的高頻分量獲得增益。

圖6是利用雙絞線和電纜延展芯片組進行高速數據傳輸原理圖。圖7為同軸電纜傳輸原理圖。

圖6 雙絞線延長傳輸原理圖

圖7 同軸電纜傳輸原理圖

3 試驗結果

對高速數據存儲系統設計進行改進后,將本系統連接到某高速圖像采集系統后,進行數據的接收和存儲。在數據回收后,由上位機軟件進行分析處理,根據數據的完整程度來驗證存儲系統的功能和可靠性。經過幾十次測試,測試數據量達300Gbyte,接收的數據均完整無誤。存儲單元回讀數據符合設計,并且數據在傳輸、存儲過程中未出現誤碼等現象,并實現了60Mbyte/s的存儲速度。證明設計方案能夠實現采集數據的準確、完整存儲及可靠回收。

4 總結

本次設計的存儲系統采用交替雙平面編程和分時加載的方式,極大地存儲速率;利用均衡加重來提高信號的傳輸質量,保證了數據存儲的準確性和完整性,在數據高速存儲方面具有良好的應用前景。

[1] 車艷霞,任勇峰,劉東海.一種小體積高速數據記錄器的設計與實現[J].自動化與儀表,2011,26(11):9-11.

[2] 盛大鵬.基于FLASH的高速大容量存儲器的研究[D].中國科學院研究生院,2008.

[3] 劉瑞,黃魯,陳楠.基于FLASH的高速大容量固態存儲系統設計[J].測控技術,2009,28(4):1-3.

[4] 吳萌,劉波.高速、大容量視頻數據存儲、傳輸系統設計[J].電子器件,2009,32(3):638-642.

[5] 陳桂生,李志剛.嵌入式FLASH文件系統的設計與實現[J].計算機系統應用,2010,19(5):36-40.

[6] 李玉峰,韓曉紅,劉洋,等.基于FPGA的高速數據采集系統的實現與性能分析[J].電子器件,2012,35(6):709-712.

[7] 陸浩,王振占.高速大容量固態存儲器設計[J].計算機工程,2011,37(15):226-231.

[8] 馬游春,張濤,李錦明.FPGA集成FIFO在高過載存儲測試系統中的應用[J].儀器儀表學報,2006,27(6):2350-2351.

[9] 任勇峰,張凱華,程海亮.基于FPGA的高速數據采集存儲系統設計[J].電子器件,2015,38(1):135-139.

尉易慶(1989-),男,漢族,山西運城人,中北大學,碩士研究生,研究方向為電路與系統,weiyiqing@yeah.net;

吳利兵(1969-),男,漢族,山西太古人,晉中職業技術學院,高級工程師,現從事工業機器人、PLC控制系統等領域的研究;

任勇峰(1968-),男,漢族,山西中陽人,博士,教授,現從事動態測試、高速數據采集等領域的研究;

賈興中(1984-),男,漢族,山西太原人,碩士,工程師,研究方向為微電路系統、電路系統檢測與診斷技術;

劉興俊(1989-),男,漢族,山西太原人,中北大學,碩士研究生,研究方向為電路與系統。

Optim ized Design of a High-Speed Storage System

WEI Yiqing1,WU Libing3,REN Yongfeng1,2*,JIAXingzhong1,LIU Xingjun1

(1.National Key Laboratory for Electronic Measurement Technology,North Uniυersity ofChina,Taiyuan 030051,China;2.Dynamic Testing Laboratory Instrument Scienceand the Ministry of Education,North Uniυersity of China,Taiyuan 030051,China;3.Jin Zhong Vocational&Technical College,Jinzhong Shanxi 030600,China)

For the requirement of data recorder with high-speed storing,it provides an optimizational design to the high-speed system based on FPGA and NANDFLASH.By using the interleaving two-plane program mode to improve its storage speed,the storage rate of the recording device reaches the highestspeed of single Flash,namely 60Mbit/s.By using twisted-pair cables and chipsetwith extended cables,the transmission quality of the system is improved.And that the logical system for storing is optimized is obtained by using erasing and writing pattern at the same time.The logical circuit is controlled by FPGA using LVDS to build interface circuit in choosing devices.And the practicability and reliability of the projecthasbeen tested and confirmed by the engineering practices.

FPGA;high-speed storage;LVDS;logic design

TP301.6

A

1005-9490(2016)04-0816-04

2015-08-11修改日期:2015-10-06

EEACC:7210G10.3969/j.issn.1005-9490.2016.04.013