FPGA的eMMC嵌入式陣列存儲系統設

周珍龍,顧彤,王紅兵

(西安電子科技大學 電子信息攻防對抗與仿真技術重點實驗室,西安 710071)

?

周珍龍,顧彤,王紅兵

(西安電子科技大學 電子信息攻防對抗與仿真技術重點實驗室,西安 710071)

本文實現了一種嵌入式陣列存儲系統,以具有體積優勢、性能優勢以及價格優勢的eMMC嵌入式多媒體卡為存儲介質,基于FPGA使用硬件邏輯實現讀寫控制器,并給出軟件仿真以及硬件測試結果。同時控制8片存儲芯片擴展容量,在速度提高方面使用了GTX高速收發器。和單片存儲系統對比,本設計系統具有海量存儲、高速讀寫等特點。

FPGA;eMMC;GTX高速收發器;陣列存儲系統;讀寫控制器

引 言

eMMC(Embedded Multi-Media Card)是嵌入式多媒體卡的簡稱[1]。當前,移動終端,尤其是手機,平板以及軍用控制器等手持設備,對存儲系統都要求高速以及海量,并且一個重要條件是體積小。設計基于FPGA的eMMC控制器有以下幾個優點:體積小,對便攜性要求嚴格的移動終端有很好的支持力,接口速度達到50 MB,符合便攜設備對訪問速度的要求,滿足大容量系統的需求;控制器采用FPGA硬件邏輯實現,提高系統兼容性。

1 eMMC陣列系統總體方案

該陣列系統主要在Xilinx公司的Virtex 6系列FPGA芯片XC6VLX240中實現控制器模塊,生成各級FIFO,以及為控制器、FIFO、eMMC芯片提供各種需求的時鐘電路。同時,該陣列系統使用GTX收發器作為數據傳輸的工具,使得系統具備高傳輸速率的特點。

本文選擇Micron的eMMC芯片,芯片型號為MTFC64GJV DN-4M IT,該芯片遵循JEDEC標準協議5.0。由于當前eMMC芯片的存儲容量有限,大容量系統必須使用多個eMMC來達到要求,這里選擇8片eMMC芯片,每片eMMC芯片的存儲容量為64 GB。對所有芯片的讀取方式有并行和串行兩種。如果采用串行的存儲方式,對芯片一塊一塊地存儲,勢必對讀寫速度有很大限制,因此本文采用并行的方式,對存儲芯片的數據位寬擴展,同時對8片eMMC芯片讀寫,數據并行位寬由單片8位擴展為8×8位的寬度。

該陣列系統的總體框圖如圖1所示,包括讀和寫兩個過程。

圖1 系統總體框圖

其中,控制器模塊負責對eMMC芯片、GTX、各級FIFO上電復位,負責整個系統工作期間的協調工作。本文需要實現對eMMC的讀和寫的功能。圖1中,寫過程時,左側發送端為數據產生模塊,右側接收端為eMMC;讀過程時,左側發送端為來自eMMC的數據,而右側輸出端則是將讀取自eMMC芯片的數據傳輸給最終申請數據訪問的模塊。整個系統對外部體現為接口,體現嵌入式FPGA的可移植性。

2 各模塊介紹

2.1數據產生模塊

數據產生模塊在數據寫過程中不可缺少[2]。本設計方案針對數據存儲,選擇塊長為512字節的數據存儲方案。故數據產生模塊每次產生的數據為512字節。這里選擇常用遞增碼作為數據源,由于eMMC的數據總線為8位,因此需要兩輪00~FF的遞增碼才能達到512字節的要求。數據產生模塊如圖2所示。

圖2 數據產生模塊

其中,cmd24_recover為控制器模塊在發送所有的寫命令之后發出的命令信號。cmd12_wanted為寫指定塊數據(每塊為512字節)之后反饋給控制器模塊的信號,該信號通知控制器模塊停止對eMMC的寫過程。

CRC即循環冗余校驗碼(Cycle Redundancy Check), CRC校驗碼為16位,生成多項式為17位。數據流左移16位,再除以生成多項式,做不借位的除法運算(相當于按位異或),所得的余數就是CRC校驗碼。CRC16計算框圖[4]如圖3所示。

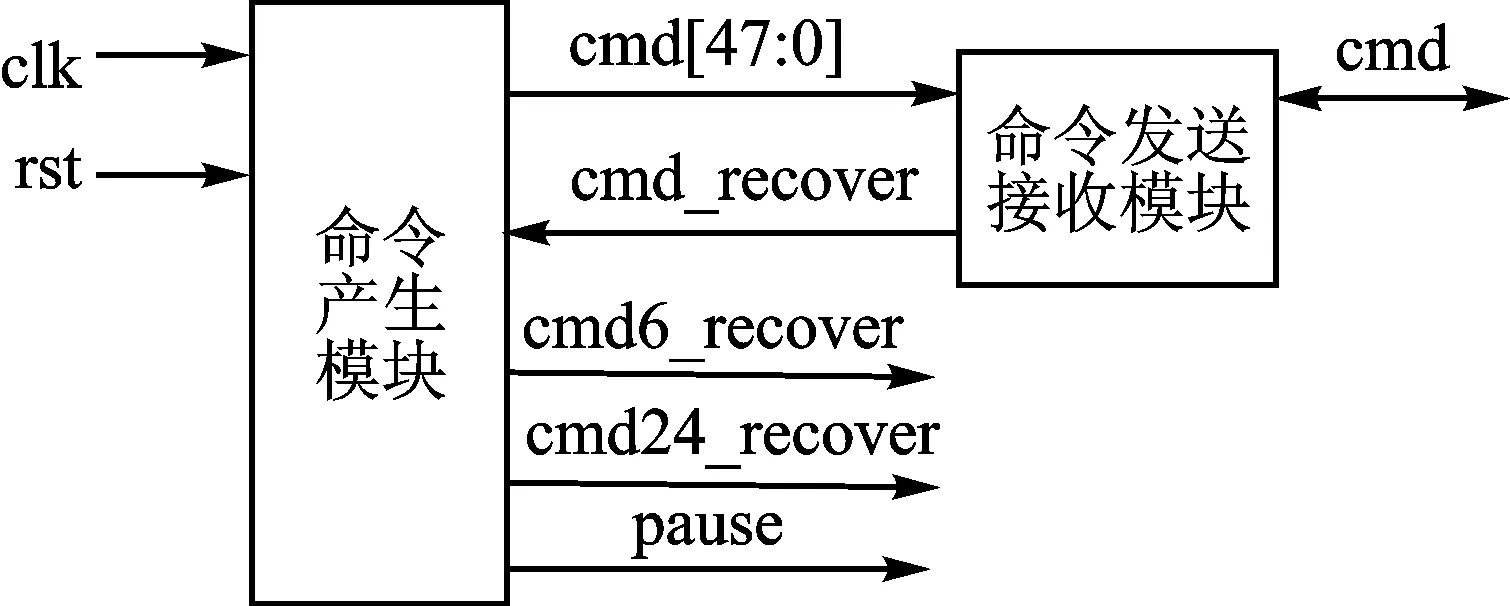

2.2控制器模塊

控制器模塊不僅需要完成對eMMC的命令發送和命令接收任務,實現eMMC的控制器設計,而且需要實現對各個模塊之間數據流動的控制。

命令發送和接收的實現,完全遵照JEDEC標準5.0的設備協議。這里介紹主要的讀寫命令發送順序[5]:讀命令發送為CMD0、CMD1、CMD2、CMD3、CMD9、CMD7、CMD8、CMD6、CMD6、CMD16、CMD23、CMD18;寫命令發送為CMD0、CMD1、CMD2、CMD3、CMD9、CMD7、CMD8、CMD6、CMD6、CMD16、CMD25、CMD12。

圖3 CRC16計算框圖

由于在eMMC寫過程中,芯片有一個編程過程,將數據寫入存儲邏輯,在該過程中數據的發送必須暫停,因此,整個系統的數據流動應該予以暫停,該過程由控制器模塊生成pause信號完成。數據讀寫過程中,需要時刻發送cmd13命令查詢eMMC芯片的工作狀態,寫過程中尤其重要,其響應指示需要判斷產生。控制器模塊具體實現方案如圖4所示。

圖4 控制器模塊實現方案

cmd24_recover代表的是上文提到的所有讀寫命令均發送完畢之后,寫過程中通知數據產生模塊產生遞增碼,讀過程中通知小FIFO開始接收來自eMMC芯片的數據。pause命令,是在讀寫過程中,由于芯片需要編程而對整個傳輸通道暫停的控制命令,該信號傳送給其他所有模塊。cmd6_recover,在控制器發送完cmd6命令并接收回應之后,通知時鐘模塊由低速時鐘切換到高速時鐘。

2.3GTX模塊

引入GTX模塊主要是針對數據傳輸速率。eMMC的工作時鐘在128 kHz~52 MHz,如果使用陣列存儲,使用8片eMMC芯片,要達到50 MHz的要求,每個時鐘傳輸一個位寬的數據,將需要8×8×50 Mbps的傳輸速率,GTX接收,發送端采用串行通信,其數據端使用16位位寬,傳輸頻率為150 MHz,因此,可以達到16×150 Mbps的傳輸速率要求,滿足eMMC陣列系統對速率的要求。

對于GTX的工作原理,這里只做簡單介紹。GTX有收發端,二者通過串行線連接[6],對于系統內的其他模塊,主要表現為數據位寬為16位的數據端口,如圖5所示。

圖5 GTX收發模塊

發送端的data連接在發送端的大FIFO,接收端的data連接在接收端的大FIFO。這里需要注意的是,當pause激活時,GTX收發器之間并沒有停止數據傳輸,而是在data線上一直發送43BC碼,并且將標識信號charisk_i設置為00。

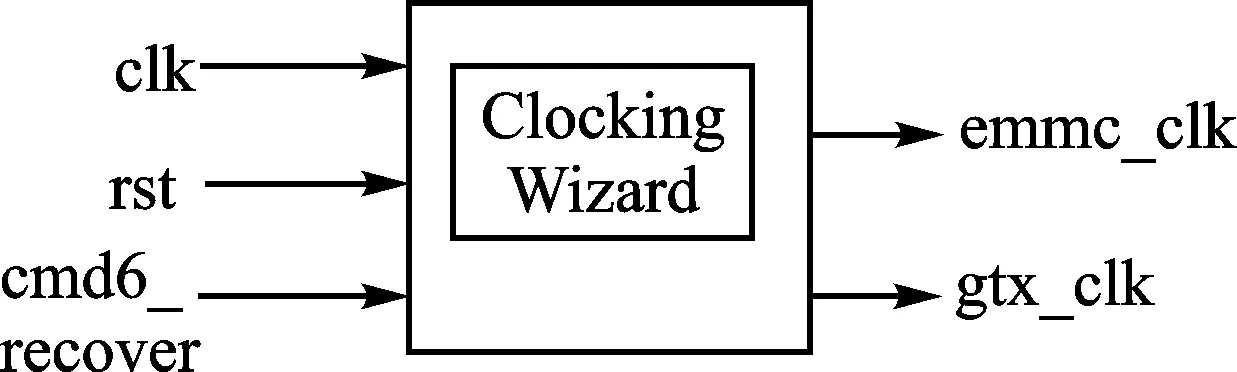

2.4時鐘切換模塊

時鐘源采用FPGA開發板上提供的50 MHz時鐘,然后使用ISE自帶的Clocking Wizard IP核,定制輸出為50 MHz、250 kHz以及150 MHz時鐘。該模塊接收來自控制模塊的cmd6_recover命令,為eMMC芯片提供時鐘電路的信號emmc_clk由初始的250 kHz時鐘切換到50 MHz,為GTX提供時鐘的信號gtx_clk維持150 MHz不變。圖6為時鐘切換模塊的結構框圖[7]。

圖6 時鐘切換模塊

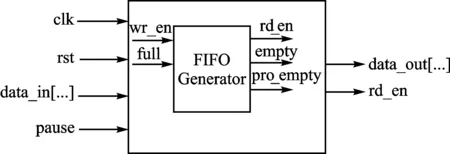

2.5各級FIFO協調工作

FIFO的配置上,讀過程和寫過程大致是一樣的。本文所有FIFO使用ISE自帶IP核FIFO Generator工具生成[8],需要注意的是,應該將FIFO的默認值設置為FF。可以將各級FIFO按照順序分為:第1級FIFO位寬為8進8出;第2級FIFO,位寬為64位進16位出,將數據發送給GTX;第3級FIFO位寬為16位進64位出,接收從GTX發送過來的數據;第四級位寬為8位進8位出。可以從圖1中清楚看到各級FIFO分配。整個FIFO系統以GTX分開為左右鏡像。各級FIFO模板見圖7,這里給出用該模板設計的第1級FIFO在ISE開發工具中的RTL圖。

圖7 各級FIFO模塊

8個第1級FIFO采用邏輯復制,使用ISE自帶的FIFO核定制主要模塊,外加控制電路設計而成。檢測到data[7∶0]為00時(依據eMMC協議,00為數據包的起始位),使能FIFO寫,將數據存入FIFO,在pro_empty不為空時,使能rd_en,如果empty不為空,則一直使能rd_en,該信號作為下一級FIFO的寫使能。下一級FIFO的讀寫使能方案同該級FIFO設計。各級FIFO不同的地方在于輸入和輸出的位寬不同。

3 軟硬件驗證

3.1ISim軟件仿真

ISim軟件驗證可以縮短系統開發的時間[9],能夠直觀地顯示出設計中存在的問題,因此前期使用ISim軟件調試。

(1) crc16模塊驗證

圖8為512的數據包(起始位00+00~FF+00~FF)的crc16計算結果,data最后為結束位FF。

(2) 各級FIFO驗證

從第1級FIFO到第4級FIFO,data1~8為第1級FIFO輸入,data_trans_xch為第1級FIFO輸出拼湊而成的第2級FIFO輸入,gtx_data_trans[15∶0]為第3級FIFO輸入,gtx_1ch_fifo_data[63∶0]為第3級FIFO輸出,emmc_1_dat~emmc_8_dat為第4級FIFO輸出,如圖9所示。

3.2ChipScope在線調試硬件驗證

系統總體驗證:最后使用Xilinx的Virtex 6系列FPGA芯片以及Micron的eMMC存儲芯片,對設計的陣列存儲系統的讀寫功能進行驗證。

寫數據驗證略——編者注。來自emmc_1_dat~emmc_8_dat數據線上的最低位輸出了確認信號0010,表示寫入的數據成功,對8片eMMC的寫數據操作正常。

圖8 crc16模塊驗證

圖9 各級FIFO驗證

讀數據驗證略——編者注。從讀出的第13個512字節的數據開始,系統繼續從eMMC存儲芯片中讀取上述寫功能寫入的數據。

結 語

本文解決單片eMMC對速度以及帶寬的限制,使用了GTX以及FPGA硬件邏輯設計滿足陣列存儲系統的要求。邏輯設計之后通過ISim軟件仿真驗證了電路的可行性,并且隨后將工程生成的二進制文件燒寫到FPGA開發板中,實現了硬件級的eMMC陣列存儲,通過在線調試工具ChipScope驗證讀寫數據全部正常。該系統在Vintex 6系列FPGA上實現讀寫功能,并可通過定制GTX核輕松移植到其他包含GTX硬核的FPGA上。本文的系統也有值得改進的地方,比如可以使用更高速的GTH傳輸數據控制更多的eMMC芯片等。

編者注:本文為期刊縮略版,全文見本刊網站www.mesnet.com.cn。

[1] EMBEDDED MULTI-MEDIA CARD (e?MMC), ELEC TRICAL STANDARD (5.0 Device)[EB/OL].[2015-10]. http://www.jedec.org/sites/default/files/docs/JESD84-B50.pdf.

[2] 周杰,郝立燕.基于FPGA的eMMC控制器及其工作方法:中國,10264666.3[P].2013-09-04.

[3] Tongsheng Zhang, Qun Ding.Design and Implementation of CRC Based on FPGA[EB/OL].[2015-10] http://xueshu.baidu.com/s?wd=paperuri:(7e1382efd173772268d2e 58aa965393c)&filter=sc_long_sign&sc_ks_para=q%3DDesign+and+Implementation+of+CRC+Based+on+FPGA&tn=SE_baiduxueshu_c1gjeupa&ie=utf-8.

[4] 葉懋,劉宇紅,劉橋.CRC碼的FPGA實現[J].重慶工學院學報:自然科學版,2007,21(3).

[5] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2003.

[6] Xilinx.Xilinx Virtex-6 FPGA GTX Transceivers User Guide,2011.

[7] 羅莉,何鴻軍,徐煒遐,等.面向SOC芯片的跨時鐘域時鐘設計和驗證[J].計算機科學,2011,9(9).

[8] 徐光輝,程東旭.基于FPGA的嵌入式開發與應用 [M].北京:電子工業出版社,2006.

[9] 王傳新.FPGA設計基礎[M].北京:高等教育出版社,2007.

周珍龍(碩士),主要研究方向為基于FPGA的高速數據存儲與傳輸;顧彤(碩士),主要研究方向為圖像融合及存儲;王紅兵(碩士),主要研究方向為基于FPGA的A/D采樣及存儲。

31Communications Interface(SCI) Reference Guide,2009.

[4] Texas Instrument.TRSF3221E 3-V TO 5.5-V SINGLE-CHANNEL RS-232 1-Mbit/s LINE DRIVER/RECEVIER WITH ±15-Kv IEC ESD PROTECTION,2007.

[5] 陳杰.MATLAB寶典[M].北京:電子工業出版社, 2011.

陳寶欣、陳林軍(碩士研究生),主要研究方向為檢測技術與自動化裝置;沈艷林(博士),主要研究方向為數字信號處理;劉鵬(講師),主要研究方向為嵌入式控制系統;姜智譯(助理工程師),主要從事油庫自動化工作。

(責任編輯:楊迪娜收稿日期:2015-12-09)

Zhou Zhenlong,Gu Tong,Wang Hongbing

(Key Lab. of Electronic Information Countermeasure and Simulation,Xidian University,Xi’an 710071,China)

In the paper,an embedded array storage system is proposed.The design uses eMMC embedded multimedia card as the storage medium which has the advantages of volume,performance and price,and it uses the hardware logic based on FPGA to implement the read and write controller.The software simulation and hardware testing are given in the paper.Eight memory chips are used to extend the capacity,and the GTX high-speed transceiver is used to improve the speed.Compared with the single chip storage system,the design has the characteristics of mass storage,high-speed reading and writing.

FPGA;eMMC;GTX high-speed transceiver;array storage system;read and write controller

TP273

A

(責任編輯:楊迪娜2015-10-16)