一種新型原邊反饋反激變換器數(shù)字采樣算法設計*

顧新艷,程松林,王 沖

(1.南京工程學院汽車與軌道交通學院,南京211167;2.東南大學國家專用集成電路系統(tǒng)工程技術研究中心,南京210096)

一種新型原邊反饋反激變換器數(shù)字采樣算法設計*

顧新艷1*,程松林2,王沖2

(1.南京工程學院汽車與軌道交通學院,南京211167;2.東南大學國家專用集成電路系統(tǒng)工程技術研究中心,南京210096)

為了實現(xiàn)原邊反饋反激變換器的高精度采樣,提出了一種新型的數(shù)字采樣控制算法。該算法根據(jù)變壓器輔助繞組兩端電壓信息調(diào)整誤差信號大小,并輸入到內(nèi)部控制環(huán)路實現(xiàn)對輸出電壓的穩(wěn)定調(diào)節(jié),相比于傳統(tǒng)的采樣電路,該方法省去了ADC或DAC電路,節(jié)省了控制電路的面積和功率的開銷。本算法通過MATLAB仿真,且在一款5 V/1 A的AC-DC電源樣機上驗證了其有效性,其中恒壓精度達到0.5%,表明該算法有很好的采樣實時性、精確性和實用性。

反激變換器;數(shù)字采樣;誤差信號;原邊反饋調(diào)節(jié)

反激式電源由于電路結構簡單、適合多路輸出、輸入對輸出電壓影響小等優(yōu)點[1-2],廣泛應用于小功率電源適配器中。反激式電源變換器根據(jù)其反饋方式不同可分為原邊反饋PSR(Primary Side Regulation)和副邊反饋。副邊反饋在變壓器原邊和副邊之間引入一個光耦,通過光耦采樣輸出信號,其能夠提供精確的恒流和恒壓控制[3],但電路組件數(shù)目較多、成本較高、可靠性較低,更主要的是光耦在高溫下線性度不好,誤差較大。而PSR則通過在變壓器中引入一個輔助繞組,進行輸出信號的采樣[4]。相比于副邊反饋,原邊反饋省去了采樣光耦、減少了電路組件數(shù)目、降低了電路復雜程度,正逐漸成為未來反激變換器的發(fā)展趨勢,同時也是現(xiàn)在國際上的研究熱點。

采樣技術在PSR反激電源的控制中起到重要作用,現(xiàn)在大致有兩種方案:一是直接利用模數(shù)轉(zhuǎn)換器ADC(Analog to Digital Converter)進行采樣[5-6],二是利用帶有數(shù)模轉(zhuǎn)換器DAC(Digital to Analog Converter)的采樣算法實現(xiàn)[7-8]。但是這兩種方案都會帶來較大的電路開銷,增加控制電路的復雜度和成本。為了降低采樣電路成本,本文提出了一種新型的數(shù)字采樣算法,該方法采用固定基準電壓與輔助繞組電壓比較的結果經(jīng)過數(shù)字運算得到輸出電壓的大小,在省去ADC 和DAC電路的同時,保持了采樣的實時性與準確性。

1 原邊反饋反激變換器原理

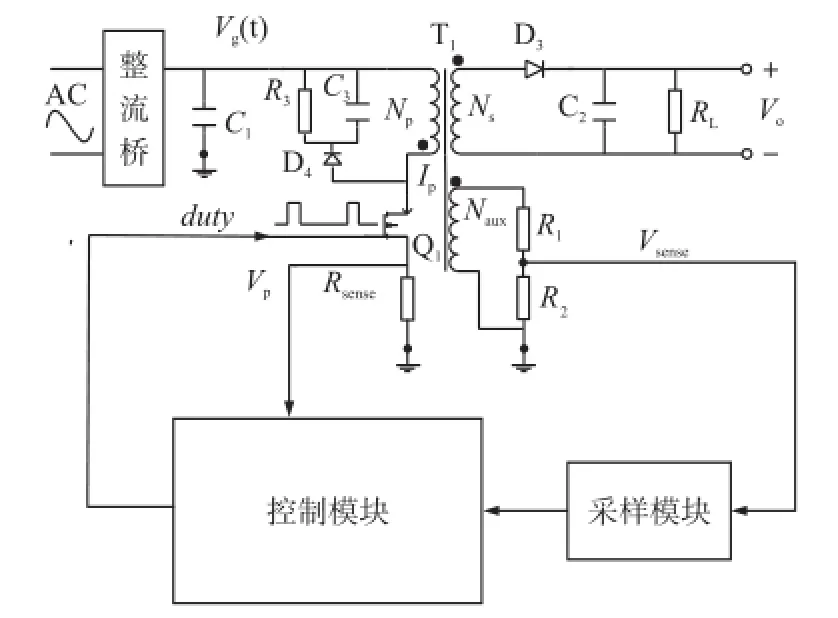

PSR反激變換器的電路主拓撲[9]如圖1所示,輸入交流電源經(jīng)過整流橋到達濾波電容C1,在C1作用下得到一個低頻波動的直流電壓Vg(t)。電阻R3、電容C3及二極管D4組成RCD鉗位電路,防止開關管Q1的漏端電壓過高,因為在Q1的關斷瞬間,其漏端電壓會迅速上升,沒有該鉗位電路,Q1很可能會由于漏端電壓過高而損壞[10-11]。變壓器T1是該電路的核心之一,它有3個繞組,分別為原邊繞組、輔助繞組和副邊繞組,其中副邊繞組和輔助繞組同名端方向相同,并且和原邊繞組同名端方向相反。原邊繞組在Q1導通期間存儲能量,Q1斷開瞬間能量耦合到副邊繞組,副邊繞組通過續(xù)流二極管D3和儲能電容C2把能量供給負載RL。輔助繞組兩端接分壓電阻R1和R2,兩個分壓電阻可取較大阻值以保證低損耗。原邊反饋反激變換器的采樣模塊根據(jù)分壓電阻R2兩端電壓Vsense得到誤差信號e(n),該誤差信號輸入到控制模塊,控制模塊根據(jù)e(n)和電流采樣電阻Rsense兩端電壓Vp通過環(huán)路控制算法進行調(diào)節(jié),從而輸出合適的占空比duty使系統(tǒng)穩(wěn)定輸出。

項目來源:國家自然科學基金項目(51405221)

收稿日期:2015-07-28修改日期:2015-08-30

圖1 原邊反饋反激變換器系統(tǒng)架構圖

2 采樣算法理論分析

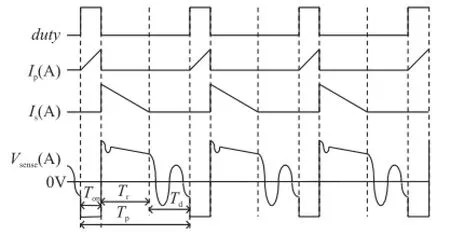

圖2中展示了PSR反激電源中原邊繞組Np電流Ip、副邊繞組Ns電流Is、采樣信號Vsense和占空比信號duty的波形,下面重點分析開關斷開后電壓Vsense的變化情況。

圖2 原邊反饋反激變換器關鍵波形

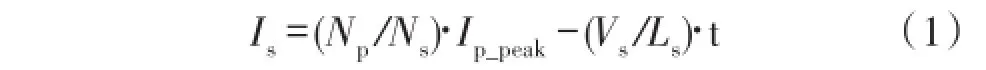

當開關關斷后,原邊繞組存儲的能量會耦合到副邊繞組,續(xù)流二極管D3有電流流過,并且線性減小,直到減小到0,這段時間稱為Tr,在此期間,Is如式(1)所示:

式(1)中,Np為原邊繞組匝數(shù),Ns為副邊繞組匝數(shù),Ip_peak為Ip峰值,Ls為副邊繞組電感,Vs為副邊繞組兩端電壓,Is降為0時刻t的大小如式(2)所示:

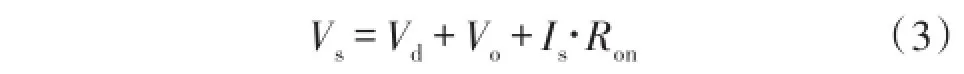

式(2)中t代表圖中時間Tr的大小,副邊繞組兩端電壓Vs滿足式(3):

式(3)中Vd代表D3導通壓降,Ron為其導通電阻。根據(jù)式(1)和式(2)可得到式(4):

式(4)表示了Vs與Vo和t的關系,根據(jù)變壓器的特性,副邊繞組兩端電壓和輔助繞組兩端電壓存在著固定的比例關系,所以當Vs與輸出電壓Vo相等時,采樣電壓Vsense與輸出電壓也有著固定的比例關系,此時t可以用式(5)表示。

通過比較式(2)和式(5)時間的大小關系可知,式(5)表示的t略大于Tr,說明在Is為0的時刻副邊繞組兩端電壓大于輸出電壓,所以在續(xù)流二極管降為0時刻采樣并不是最準確的,如圖3所示。

圖3 數(shù)字原邊采樣方案波形關系圖

當電流Is降為0時,采樣電壓Vsense開始從峰值A處正弦衰減振蕩,并且衰減振蕩的周期固定。此時Vsense的值并不和Vo成固定比例關系,經(jīng)過Δt時間后B處Vsense和Vo呈固定比例關系,并且滿足式(6):

3 采樣算法實現(xiàn)

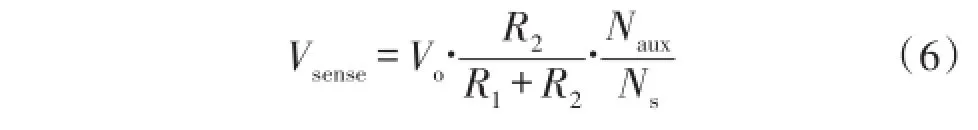

由上節(jié)分析可得,在圖3中的B處進行采樣更為合理,這里給出了一種新型的數(shù)字采樣方案,與現(xiàn)有的數(shù)字采樣方案相比,省去了DAC和ADC,節(jié)省了芯片的面積和功耗,并且更為精確,采樣模塊的架構如圖4所示。

圖4 數(shù)字采樣模塊算法原理架構圖

圖4中Vzvs是0電位電壓,電壓Vr是一個固定電位電壓,其大小可用式(7)表示:

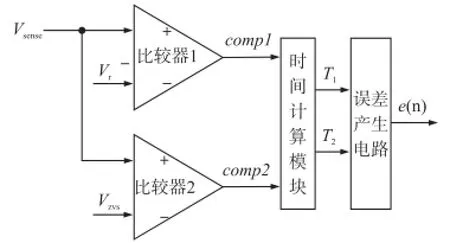

式(7)中Vo代表預期輸出電壓,R1和R2代表采樣分壓電阻,根據(jù)上面分析可知當Vsense和Vr相交于圖3 中B點時代表輸出電壓穩(wěn)定在預期值,當Vsense和Vr相交于圖3中B點下面時代表輸出電壓偏大,當Vsense和Vr相交于圖3中B點上面或沒有交點時,代表輸出電壓偏小,根據(jù)輸出電壓是否偏離穩(wěn)定值,Vsense、Vr和Vzvs不同情況下關系如圖5所示。

圖5 采樣方案中不同情況的工作波形圖

如圖5(a)所示,Vsense和Vr相較于B點,此時輸出電壓穩(wěn)定,比較器1和比較器2的輸出波形輸入到時間產(chǎn)生模塊,時間產(chǎn)生模塊根據(jù)內(nèi)部計數(shù)器得到時間信息T1和T2,在圖5(a)中T1和T2滿足T2/2-T1=Δt,此時誤差產(chǎn)生電路檢測到該狀態(tài),則輸出一個大小為0的數(shù)字誤差信號e(n),表示沒有誤差;在圖5(b)中T1和T2滿足T2/2-T1>Δt,此時誤差產(chǎn)生電路檢測到這個狀態(tài),將輸出一個負的數(shù)字誤差信號e(n),其具體大小根據(jù)T2/2和T1差值來設定,T2/2和T1差值越大,表明輸出電壓偏離的越大,產(chǎn)生的數(shù)字誤差信號e(n)的絕對值則越大;在圖5(c)中T1和T2滿足T2/2-T1<Δt,此時誤差產(chǎn)生電路檢測到這個狀態(tài),將輸出一個正的數(shù)字誤差信號e(n),其具體大小根據(jù)T2/2和T1差值設定,T2/2和T1差值越大,表明輸出電壓偏離越大,產(chǎn)生的數(shù)字誤差信號e(n)的絕對值就越大;在圖5(d)中Vr和Vsense沒有交點,此時表明輸出電壓還很小,誤差產(chǎn)生電路得到一個最大的數(shù)字誤差信號e(n)。采樣模塊除了可以得到誤差信號,還可以得到Tr時間的大小,具體可表示為Tr=T3-T2/2,其中T3表示為開關關斷后comp2的第1個高電平維持時間寬度。

上面闡述了采樣算法的基本原理,但是仍然有一個問題沒有解決,那就是如何確定Δt,根據(jù)正弦波形的特性,在圖3中A點附近的波形斜率最小,在B點附近波形斜率也很小,但是和A處比已經(jīng)偏大了,由于采樣算法的時間信息是通過計數(shù)器計數(shù)得到的,所以采樣波形斜率越小采樣的精度就越高,為了提高采樣精度可以設定Δt為0。但是設定Δt為0,根據(jù)前面理論分析可知輸出電壓不能穩(wěn)定在預期值,而且比預期值小,為了解決這個問題,可以引入一個修正因子a,具體大小可以用式(8)表示:

式(8)中Vo表示預期輸出電壓值,Vo'表示實際輸出電壓值,根據(jù)具體的仿真和測試得到修正因子a,然后通過改變分壓電阻比或變壓器匝數(shù)比來實現(xiàn)對輸出電壓的調(diào)節(jié)。

4 采樣算法仿真驗證

4.1仿真平臺

為了驗證所提算法,這里搭建了一個基于MATLAB的5 V/1 A PSR反激電源仿真平臺,表1給出了反激變換器的主要參數(shù)。

表1 反激變換器參數(shù)

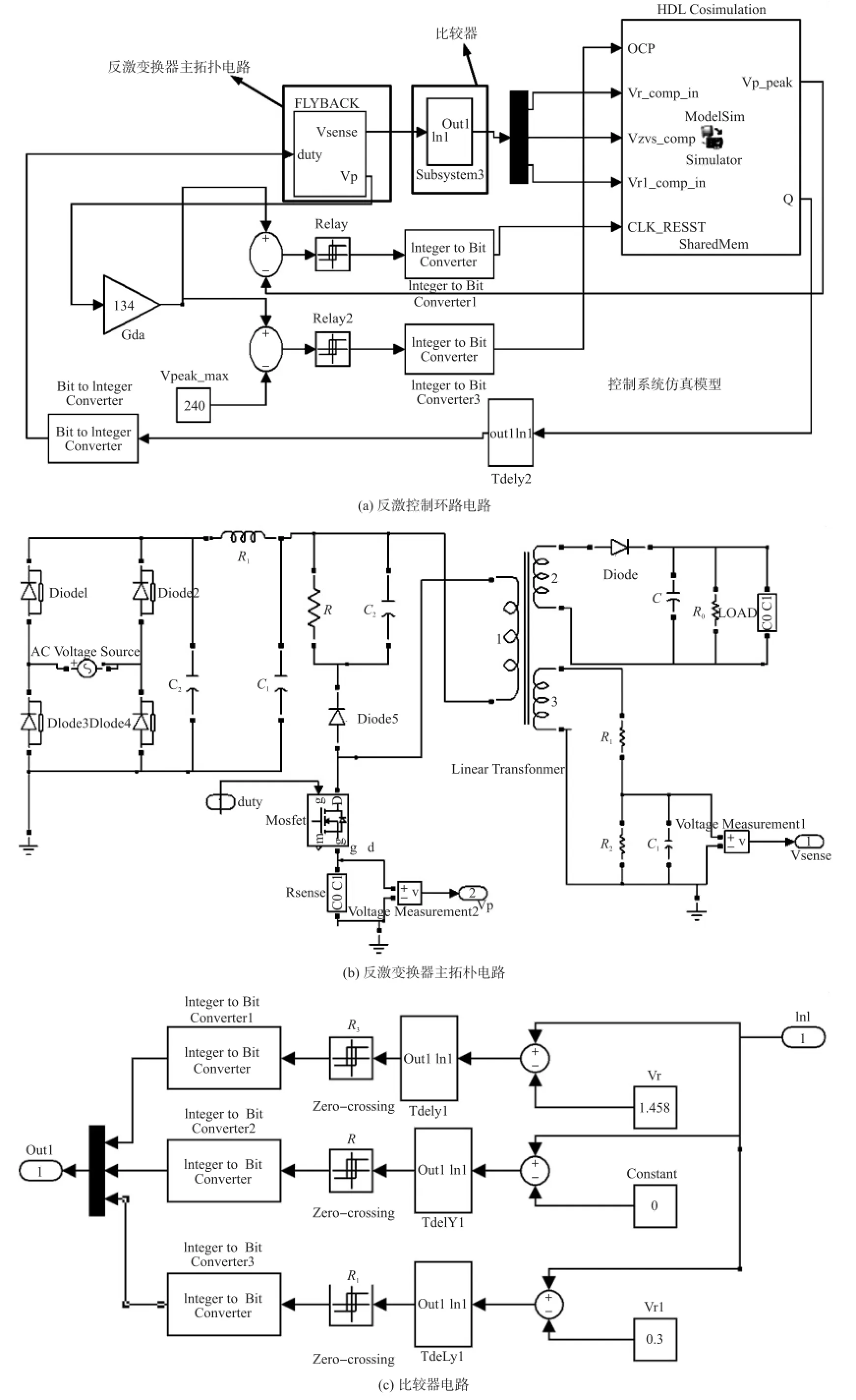

圖6是PSR反激電源的仿真平臺,圖6(a)是反激電源的控制環(huán)路拓撲,圖6(b)是圖6(a)子模塊反激系統(tǒng)的電路拓撲,圖6(c)是圖6(a)子模塊采樣模塊的比較器電路。

為了盡可能獲得較高的采樣精度,整個數(shù)字電路工作時鐘頻率為40 MHz,Δt設定為0。固定電壓Vr的大小為1.458V左右。表2給出了T2/2-T1同e(n)關系。

圖6 PSR反激電源的仿真平臺

表2 T2/2-T1同e(n)關系

4.2仿真結果分析

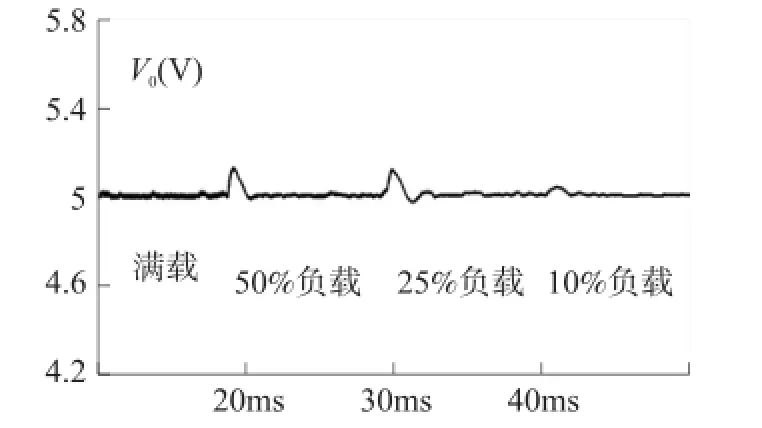

根據(jù)前面分析,將分別仿真修正因子加入前后,輸出電壓Vo穩(wěn)態(tài)變化情況,仿真的輸入電壓為交流220 V,仿真結果如圖7和圖8所示。

圖7 未加修正因子時輸出電壓波形

圖8 加入修正因子時輸出電壓波形

圖7和圖8分別展示了未加入修正因子和加入修正因子時輸出電壓波形,可以發(fā)現(xiàn)整體輸出電壓穩(wěn)壓效果較好,在全負載范圍內(nèi)輸出電壓精度控制在了±0.5%之內(nèi)。此外,同理論分析一致,在未加入修正因子時輸出電壓的穩(wěn)定值小于5 V,加入修正因子之后輸出電壓的穩(wěn)定值控制在了5 V,仿真時修正因子的加入是通過改變采樣電阻分壓比來實現(xiàn)的。

為了驗證所提數(shù)字采樣算法的動態(tài)跟隨特性,對交流220 V輸入電壓下,滿載和10%負載之間切換時Vo動態(tài)特性進行了仿真分析,如圖9所示。

在圖9中,仿真了負載切換時輸出電壓響應波形和電流采樣電阻兩端的電壓Vp波形。滿載切換到10%負載時,響應時間為4.5 ms;10%負載切換到滿載時,響應時間為0.94 ms。同參考文獻[11]相比,本文所提采樣算法在省去DAC的前提下同樣獲得了比較好的動態(tài)跟隨效果。

圖9 滿載和10%負載切換時輸出電壓響應波形

圖10 采樣波形圖

圖10展示了電壓穩(wěn)在5 V時,Vsense、Vr和副邊電流Is波形,可以發(fā)現(xiàn)Vr和Vsense的交點處于副邊電流降為0后的一點。與參考文獻[6-7]相比,本算法的一個優(yōu)點就是省去了DAC電路,在0.18 μm工藝下,一個DAC電路大約要占到整個芯片面積的1/6左右,所以在芯片設計時,芯片的面積和功耗將得到有效減少。

5 結束語

本文針對原邊反饋反激變換器現(xiàn)有采樣算法的缺陷,設計了一種新型的數(shù)字采樣算法,省去了傳統(tǒng)采樣算法所應用的ADC或DAC電路,減小了電路開銷和損耗,通過加入修正因子,在保持實時性的同時做到了更為精確的采樣,最后通過仿真驗證了所提算法的有效性,仿真結果和理論分析一致,所提算法具有一定的理論和工程應用價值。

[1] 普利斯曼,比得斯,莫瑞.開關電源設計[M].第2版.北京:電子工業(yè)出版社,2005:71-72.

[2] 鮑小亮.多調(diào)制模式反激式變換器的研究與設計[D].電子科技大學,2009.

[3] 張偉東,何杞鑫.一種適用于準諧振AC/DC控制芯片的波谷檢測電路[J].電子器件,2008,31(6):1786-1789.

[4] Li Y C,Chen C L.A Novel Primary-Side Regulation Scheme for Single-Stage High-Power-Factor AC-DC LED Driving Circuit[J]. IEEE Transactions on Industrial Electronics,2013,60(11):4978-4986.

[5] Chang C W,Lin Y T,Tzou Y Y.Digital Primary-Side Sensing Control for Flyback Converters[C]//International Conference on Power Electronics and Drive Systems,IEEE,2009:689-694.

[6] Kang S H,Maksimovic D.Simplified Sensing and A/D Conversion for Digitally Controlled Flyback DC-DC Converters with On-Line Efficiency Optimization[C]//Applied Power Electronics Conference and Exposition(APEC),2012 Twenty-Seventh Annual IEEE,IEEE,2012:1075-1082.

[7] Lin A M L,Eason M D,Muegge M R.Power Converter Controller Controlled by Variable Reference Voltage Generated by Dual Output Digital to Analog Converter[P].U.S.Patent 7,589,983. 2009-09-15.

[8] 邱建平,林玲,何樂年.反激式開關電源控制芯片中的高精度原邊反饋技術[J].電路與系統(tǒng)學報,2013,18(1):403-407.

[9] Hwang J T,Jung M S,Kim D H,et al.Off-the-line Primary Side Regulation LED Lamp Driver with Single-Stage PFC and TRIAC Dimming Using LED Forward Voltage and Duty Variation Tracking Control[J].IEEE Journal of Solid-State Circuits,2012,47 (12):3081-3094.

[10]Meng P,Wu X,Yang J,et al.Analysis and Design Considerations for EMI and Losses of RCD Snubber in Flybackconverter[C]//Applied Power Electronics Conference and Exposition(APEC),2010 Twenty-Fifth Annual IEEE,IEEE,2010:642-647.

[11]王沖.基于損耗模型的原邊反饋反激電源數(shù)字多模式設計[D].南京:東南大學,2014.

[12]Qiu J,He L,Wang Y.A Multimode Digital Controller IC for Flyback Converter with High Accuracy Primary-Side Feedback[J]. Journal of Zhejiang University SCIENCE C,2013,14(8):652-662.

顧新艷(1977-),女,漢族,江蘇常州人,南京工程學院講師,工學碩士,主要從事電子電氣自動化方面的教學與研究,zdhxgxiny@njit.edu.cn。

Design of a Novel Digital Sampling Algorithm for Primary Side Regulation Flyback Converter*

GU Xinyan1*,CHENG Songlin2,WANG chong2

(1.School ofAutomotive and Rail Transit,Nanjing Institute of Technology,Nanjing 211167,China;2.National ASIC System Engineering Research Center,Southeast University,Nanjing 210096,China)

A new digital sampling control method is proposed in order to achieve high precision for primary side regulation flyback converter.The output voltage error can be received from the auxiliary winding of the transformer,and then can be used in the internal control loop to keep the output voltage stable.Compared to traditional digital sampling method,ADC or DAC is neglected in order to reduce the spending of circuit and power.Based on simulation,a 5 V/1 A AC-DC prototype of PSR flyback converter is used to verify the validity of the proposed sampling method. The voltage accuracy of constant voltage regulation reaches 0.5%.Which indicated that the algorithm has good realtime sampling,accuracy and practicablity.

flyback converter;digital sampling;voltage error;primary side regulation

TM464.62

A

1005-9490(2016)03-0644-06

EEACC:7210G10.3969/j.issn.1005-9490.2016.03.028