基于FPGA新型視頻光端機模塊的設計

郭娟 耿濤 劉玉珍 張曉鵬 丁鑫

摘 要:為解決模擬視頻光端機傳輸容量小、業務能力少、信號易衰減、易串擾等問題,文中設計了一種基于FPGA的新型視頻光端機模塊。視頻光端機是視頻監控系統中最重要的組成部分之一,該模塊可將硬件設計、軟件設計及信道編解碼等進行綜合運用,并經FPGA對數字視頻信號進行處理,然后使用 Quartus II開發套件實現軟件設計,并對各個模塊輸入相應波形進行測試,然后運用ModelSim10.0 SE對各個模塊以及系統進行功能仿真和時序仿真。通過多次測試證明:該系統性能穩定,可靠性高,圖像質量清晰。該成果目前已應用到實驗教學當中,且收到了較好的教學效果。

關鍵詞:新型;視頻光端機;Quartus II;ModelSim10.0 SE

中圖分類號:TP39 文獻標識碼:A 文章編號:2095-1302(2016)07-00-04

0 引 言

數字視頻光纖傳輸系統是把一到多路的模擬視頻信號通過模數轉換將模擬信號轉換為數字信號,再經過編碼及光電轉換后以光信號在光纖介質中傳輸視頻的一組設備。隨著電子技術的迅速發展,數字視頻光端機的結構更加復雜,其集成化程度也越來越高。而且現今視頻光纖傳輸系統具有更多的功能及更強大的數據傳輸能力,其結構也隨之更加復雜,成本也更高昂。而本設計提供一種簡單、低成本、開放式的數字視頻光端機。通過本設計能夠便捷地觀測視頻信號在整個傳輸系統中的傳輸狀態,并且本設計還包含FPGA、圖像處理、數字信號處理、電路分析及應用等知識點,在設計過程中,能夠基本掌握相關理論知識的應用能力[1]。

1 數字視頻光端機的總體結構設計

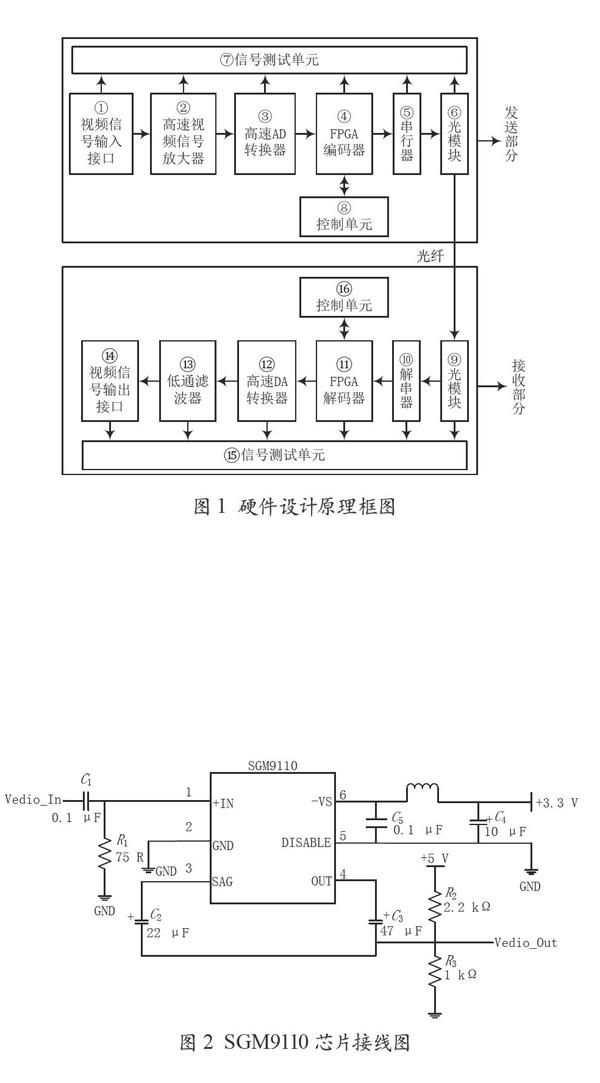

該模塊的硬件設計原理框圖如圖1所示,該視頻光端機模塊即數字視頻光纖傳輸系統,主要分為發送部分和接收部分,發送部分的主要功能是信號采集和信號處理,接收部分的主要功能是信號處理和信號恢復,發送機和接收機采用光纖連接[2]。

發送部分首先將攝像頭采集的視頻信號經過高速視頻信號放大器放大后送至高速A/D轉換,經FPGA對數字視頻信號進行處理、并/串轉換、電/光轉換后送入光纖信道傳輸,信號測試單元可測試各個電路信號狀態并保留FPGA下載接口,提供二次開發功能。

接收部分電路的功能是發送部分的逆過程。由于數模轉換器輸出的模擬信號具有高頻分量且信號很微弱[3],因此需在后級電路中加入濾波及放大電路后才能輸出到視頻輸出接口。

2 硬件電路設計及器件選型

2.1 視頻采集電路

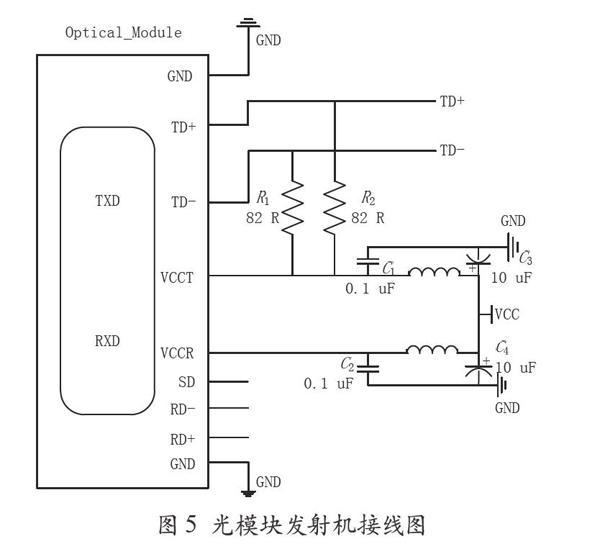

視頻采集電路由彩色攝像頭、低通濾波器、視頻放大器及電平調整電路組成。其功能將模擬視頻信號進行濾波、視頻放大及電平調整后輸出到模數轉換器。本設計采用SGM9110視頻專用放大器芯片,其芯片接線圖如圖2所示。

2.2 模/數轉換和數/模轉換電路

考慮到系統分辨率、功耗和成本,設計中選擇美國德州儀器(TI)公司的TLC5510I并行比較型模數轉換器。采用24引腳的貼片封裝(TSSOP-24),采樣頻率為13.5 MHz;數/模轉換設計采用20引腳的貼片封裝(TSSOP-20)的TLC5602C。

視頻模數轉換電路的功能是把處理后的模擬視頻信號轉化為數字視頻信號[4]。PAL制視頻信號的帶寬為0~6 MHz,由奈奎斯特抽樣定理可知[5],視頻轉換電路的采樣頻率至少為12 MHz才能保證接收端可以完整的恢復視頻信號,否則將出現頻率混迭效應。

數模轉換完成與模數轉換相反的功能,即把數字編碼的視頻信號數據轉換成標準的模擬彩色全電視信號,再經過放大電路后,送入監視器。考慮到本系統中包含多路視頻,因此盡量選擇具有多通道的數模轉換器件。這樣不僅能使系統電路的集成度和可靠性更高,而且也相應地降低了成本。經過多方面的比較和參考,最終選定了美國德州儀器(TI)公司的TL5602C高速數模轉換器。

2.3 主控電路

主控電路主要對模/數轉換后的8位數字信號進行數字編碼,同時為外圍電路提供必要的驅動信號[6]。設計采用Altera公司MAXII系列的EPM570T100C5N芯片。芯片具有570個邏輯單元(LE),用戶Flash存儲量為8.192 Kb,器件引腳到引腳的邏輯延遲固定為4.5 ns,其輸入時鐘頻率最高可達304 MHz,而且可以通過JTAG接口實現在線編程。EPM570T100C5N芯片外圍電路設計如圖3所示。

在PCB的設計中EPM570芯片的每個電源引腳均有一個0.1 μF的瓷片電容去耦,以保證器件的穩定工作。晶振電路采用54 MHz有源晶體振蕩器,將有源晶振輸出的時鐘信號四分頻,即13.5 MHz。

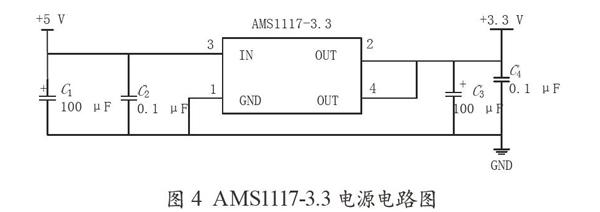

2.4 電源電路設計

EPM570T100C5N的供電分為核心供電VCCINT和I/O供電VCCIO兩種,其核心供電VCCINT為固定電壓3.3 V[7]。I/O供電模塊分為VCCIO1和VCCIO2兩種,分別為EPM570芯片的兩個I/O模塊供電,給I/O模塊提供不同的電壓可以使這兩個I/O模塊適應不同的電平標準。設計中的兩個I/O模塊分別與模數/數模轉換器和并串、串并轉換器連接,其接口電壓平均為3.3 V,因此,VCCIO1和VCCIO2均接3.3 V電源。3.3 V 電源由AMS1117-3.3芯片將5 V電源轉換后得到,再經過100 μF鉭電容和0.1 μF陶瓷電容濾波后供給CPLD。電源轉換電路設計如圖4所示。

2.5 并/串轉換、串/并轉換電路及光/電、電/光轉換電路

本設計采用SN65LV1023A芯片電路并/串轉換和SN65LV1224B串/并轉換電路。

光模塊發射機部分接收外部低電壓差分信號,將其轉換為光信號從光纖輸出。將SN65LV1023的LVTTL電平差分數字視頻信號轉換為PECL電平,使其與光發射機輸入的規定電平相匹配。VCCR和VCCT均接+5 V,并分別接串聯電感和旁路電容,以濾除電源干擾信號。光模塊發射機外圍電路設計如圖5所示。

接收機部分是接收從光纖傳輸過來的光信號,并將其轉換為低電壓差分數字信號。因此接收機差分數據輸入管腳RD±參照典型電路接法與SN65LV1224的差分數據輸出管腳RI±連接。光模塊發射機外圍電路設計如圖6所示。

3 系統軟件設計

3.1 系統軟件設計

軟件設計的實現使用 Quartus II開發套件[8],在 CPLD內部使用 Verilog HDL語言進行硬件描述[9]。發射部分設計方案如圖7所示(接收部分設計方案與發射部分類似,是與發射部分相反的一個過程),軟件設計主要分為數據處理模塊和外設驅動模塊。

信號處理模塊的程序主要為數字信號編、解碼,此程序在發送部分的FPGA中將原有數字信號進行編碼,在接收部分的FPGA中將編碼后的數字信號進行解碼。外設驅動模塊主要是為其它外圍電路提供必須的時鐘、數據及使能等信號。發射部分設計如圖7所示。

3.2 視頻編碼

本設計采用8B10B編碼方案,該編碼方案由IBM公司開發,其目的是平衡并串轉換后串行碼流中 “0”碼與 “1”碼的個數,從而起到平衡直流的作用,通常用HGFEDCBA表示編碼前的8位二進制數,即低五位二進制數為EDCBA,高三位二進制數為HGF。5B6B編碼后的6位二進制數表示為abcdei,而3B4B編碼后的4位二進制數表示為fghj,最后合成的10位二進制碼表示為abcdeifghj。由于設計中未使用控制代碼,信道僅傳輸數據,因此8B10B編碼的對應關系如圖8所示。8B10B編碼程序框圖如圖9所示。

3.3 視頻解碼

8B10B解碼電路的基本原理是將10位編碼數據分為高四位和低六位兩部分,然后分別以映射的方式對其進行解碼[10]。解碼電路除了完成8B10B的解碼功能外,還要檢測接收到的數據是否有誤碼,檢測誤碼的方法主要是8B10B編碼時的極性交替規則和平衡度規則。

4 系統測試及結果分析

4.1 硬軟件測試

硬件測試即分別對各個模塊輸入相應的波形進行測試,其結果工作均正常。軟件測試即利用ModelSim10.0 SE對各個模塊以及系統進行功能仿真和時序仿真。以下主要對8B10B編解碼的仿真結果進行分析。8B10B編碼仿真結果如圖10所示。8B10B解碼仿真如圖11所示。設計中的光纖線路是單向傳輸的,因此解碼程序并沒有實現誤碼檢測、極性判斷等功能。解碼電路僅僅是將10 b的編碼信號通過映射關系轉換為編碼前的原始信號。其仿真結果正確。

4.2 綜合測試

設計最終測試時直接將攝像頭接入信號輸入端,同時在輸出端顯示攝像頭采集的信號,如圖12、圖13所示。

由實際測試可知,圖像質量比較清晰。所設計的視頻監控傳輸模塊性能良好,可靠性強,可對監控目標進行實時監控。

5 結 語

論文對創新實驗教學視頻光纖傳輸系統的設計應用過程進行了探討,通過多次測試及目前在教學中的應用已經證明:該系統性能穩定,可靠性高。該成果的應用,克服了現有市場上視頻光纖傳輸封裝性過強的缺點,使學生掌握了儀器設備的設計方法、使用方法、信號處理過程及編程實現。

該系統經過封裝設計后可用于多種場合的安全監控。也可在本設計的基礎上,通過換用大容量的可編程邏輯芯片,與各種不同的接口芯片相連,實現多路數字視頻輸出和用途的光端機,比如以太網接口的接收機,VGA數字視頻接口的接收機等,具有更廣闊的應用空間。

參考文獻

[1]孔哲,王偉.基于FPGA的32位ALU的設計與實現[J].信息技術,2013(12):121-125.

[2]張新社,劉原華,何華,等.光纖通信技術[M].北京:人民郵電出版社,2014.

[3]郭譯群.光端機的創新發展與應用[J].科技視界,2015(1):124-126.

[4]童詩白,華成英.模擬電子技術基礎[M].北京:高等教育出版社,2007.

[5]管致中,夏恭恪,孟橋.信號與線性系統[M].北京:高等教育出版社,2015.

[6]姚薇,周奎,盧傳浩,等.基于復分接技術的電力專用型視頻光端機的開發與設計[J].電子制作,2014(22):292-293.

[7]汪涵.本安型四路數字視頻光端機的設計[J].常州信息職業技術學院學報,2014(5):13-16.

[8]陳忠平,高金定,高見芳.基于Quartus II的FPGA/CPLD設計與實踐[M].北京:電子工業出版社,2010.

[9]夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2008.

[10]邵寶華.視頻光端機在高速公路監控系統中的應用與選型[J].中國新技術新產品,2009(15):91-92.