基于CPCI系統(tǒng)的高速數(shù)字通信接口電路設(shè)計(jì)與應(yīng)用

李國達(dá)

摘 要: 隨著航空電子系統(tǒng)的迅速發(fā)展,系統(tǒng)間頻繁的信息交換和共享對數(shù)據(jù)傳輸實(shí)時性和可靠性的要求日益提高。針對這一要求,提出了一種基于CPCI系統(tǒng)下實(shí)現(xiàn)AFDX協(xié)議端系統(tǒng)接口功能的方法,為通用信號處理平臺與AFDX網(wǎng)絡(luò)的連接提供接口,實(shí)現(xiàn)AFDX協(xié)議數(shù)據(jù)的高速、可靠性傳輸。給出了采用FPGA實(shí)現(xiàn)該功能的整體方案,詳細(xì)描述了基于FPGA硬件開發(fā)的各個模塊的設(shè)計(jì),介紹了基于MicroBlaze的嵌入式軟件設(shè)計(jì)方法,在EDK中采用C語言實(shí)現(xiàn)AFDX協(xié)議IP層以上的封裝和解封裝。最后經(jīng)過仿真驗(yàn)證和測試,驗(yàn)證了設(shè)計(jì)的正確性。

關(guān)鍵詞: CPCI; 航空全雙工以太網(wǎng); 端系統(tǒng); FPGA; 嵌入式軟件

中圖分類號: TN914.3?34; TM417 文獻(xiàn)標(biāo)識碼: A 文章編號: 1004?373X(2016)07?0075?04

Abstract: In recent years, with the rapid development of avionics system, the requirements of frequent information exchange and sharing among system to real?time and reliable data transmission are increasingly increased. For this issue, a method based on CPCI system to implement the end system interface function of AFDX protocol is proposed, which can provide the interface to connect the general signal processing platform and AFDX network, and realize the high?speed and reliable transmission of AFDX protocol data. The overall plan of using FPGA to implement the function is given, in which the design of each module developed by FPGA hardware is described in detail, and the embedded software design method based on MicroBlaze is introduced. The C language is used to realize the capsulation and decapsulation above IP layer of the AFDX protocol in EDK. The correctness of the design was verified by simulation and test.

Keywords: CPCI; AFDX; end system; FPGA; embedded software

0 引 言

隨著通信技術(shù)的高速發(fā)展,嵌入式系統(tǒng)對數(shù)據(jù)傳輸速率的要求更高。在航空等軍用電子設(shè)備中,實(shí)現(xiàn)信號處理算法的數(shù)字信號處理機(jī),起著至關(guān)重要的作用。CPCI總線技術(shù)有效解決了高速互聯(lián)問題。

20世紀(jì)90年代,PCI總線技術(shù)被廣泛應(yīng)用,但是它可靠性較低,無法滿足對正常運(yùn)行時間要求較高的高可用性系統(tǒng)。加之其主板連接器可靠性低,更換時易被損壞。CPCI的高帶寬特點(diǎn),決定了其適用于高速數(shù)據(jù)通信場合。隨著國外著名計(jì)算機(jī)系統(tǒng)公司基于CPCI產(chǎn)品和方案的推廣及PICMG/PRC對CPCI技術(shù)的宣傳,我國工業(yè)控制領(lǐng)域越來越多地把CPCI應(yīng)用于高性能嵌入式系統(tǒng)之中。本文研究了在CPCI系統(tǒng)環(huán)境下高速數(shù)字通信AFDX協(xié)議端系統(tǒng)接口的電路設(shè)計(jì)與功能實(shí)現(xiàn)。采用Verilog編程實(shí)現(xiàn)基于FPGA的硬件設(shè)計(jì)部分,采用C編程實(shí)現(xiàn)基于MicroBlaze的嵌入式軟件設(shè)計(jì)。

1 基于FPGA的硬件設(shè)計(jì)

1.1 MAC模塊、FIFO模塊和MII模塊

FIFO模塊分為接收FIFO和發(fā)送FIFO,通過調(diào)用IP核來實(shí)現(xiàn)。本文所設(shè)計(jì)的MAC模塊和FIFO模塊的基本結(jié)構(gòu)如圖1所示。MAC核通過MII接口和PHY芯片進(jìn)行外部通信,通過發(fā)送FIFO和接收FIFO進(jìn)行FPGA內(nèi)部數(shù)據(jù)的通信。

1.2 CRC模塊

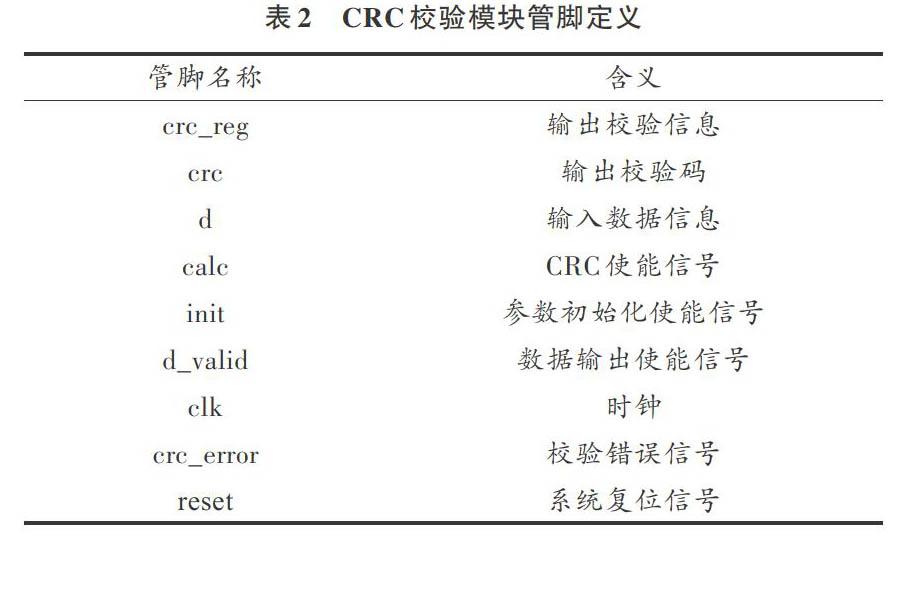

CRC模塊通過檢驗(yàn)數(shù)據(jù)的CRC值,判決接收的數(shù)據(jù)的正確性和有效性。在數(shù)據(jù)包被發(fā)送后,緊接著該數(shù)據(jù)包的4 B CRC也會被發(fā)送。接收者通過數(shù)據(jù)包和CRC數(shù)據(jù)就可以得出新的CRC值。若新CRC值為0,表明接收和發(fā)送的數(shù)據(jù)不一致,crc_error將會置1。其管腳定義如表2所示。

1.3 規(guī)整模塊和冗余管理模塊

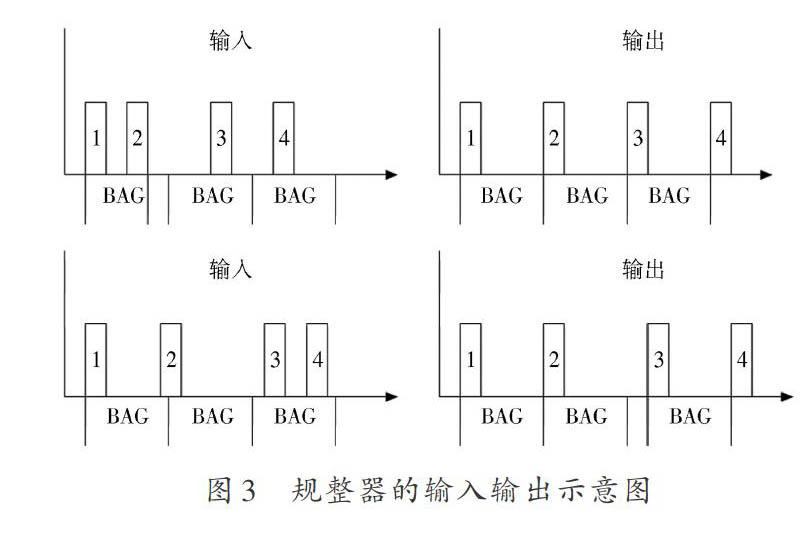

規(guī)整模塊根據(jù)每條VL的BAG,Lmax值,對其數(shù)據(jù)流進(jìn)行規(guī)整。具體方式為:當(dāng)該VL的BAG時間達(dá)到,且Jitter在最大抖動的范圍內(nèi)、幀長小于Lmax,則置FTT標(biāo)識有效,此時多路復(fù)用器模塊會申請對該VL進(jìn)行調(diào)度;反之,不能對該VL進(jìn)行調(diào)度。將固定帶寬分配給每個VL,等價于把接收端與發(fā)送端之間的數(shù)據(jù)傳輸限制在一個BAG內(nèi),即在一個BAG內(nèi)只有一次數(shù)據(jù)傳輸,如果數(shù)據(jù)包過大,將其分為多個幀進(jìn)行發(fā)送,也將會在各自的BAG內(nèi)進(jìn)行發(fā)送。所以,為了保證任意時間段使用的帶寬都是可以被確定的,必須把一個時間段合理地分配給不同的終端系統(tǒng)使用,規(guī)整器的輸入輸出示意圖如圖3所示。

從圖3可看出,兩個數(shù)據(jù)幀之間的長度大于BAG,那么正常接收;當(dāng)兩個數(shù)據(jù)幀之間的長度小于一個BAG,就將后一個數(shù)據(jù)幀移動到第二個BAG的起始位置。

在AFDX網(wǎng)絡(luò)中,通過不同的AFDX網(wǎng)絡(luò)交換機(jī)將兩個互為冗余的幀傳遞到同一個目的端系統(tǒng)。只要交換機(jī)輸出端口的輸入流量大于輸出流量,就必定會產(chǎn)生交換延遲。因?yàn)椴煌慕粨Q機(jī)的交換延遲不是確定值,所以兩個互為冗余的幀到達(dá)目的端的時間間隔也是不確定的。設(shè)計(jì)時,將SkewMax(最大偏斜)用于AFDX的接收冗余管理中以便對冗余幀的接收時間進(jìn)行限制。冗余管理模塊的功能是對接收幀的有效性進(jìn)行驗(yàn)證,并將重復(fù)的有效幀進(jìn)行消除。冗余管理模塊的框圖如圖4所示。

1.4 發(fā)送和接收模塊

發(fā)送數(shù)據(jù)的基本過程如下:要發(fā)送數(shù)據(jù)時,將待發(fā)送數(shù)據(jù)傳輸?shù)組AC的發(fā)送緩存中,發(fā)送緩存接收到的數(shù)據(jù)達(dá)到設(shè)定值時,數(shù)據(jù)發(fā)送模塊開始進(jìn)行幀間隔計(jì)時;發(fā)送幀的前導(dǎo)碼;發(fā)送幀起始定界符;幀長計(jì)數(shù)、CRC校驗(yàn)和計(jì)算,同時將數(shù)據(jù)按半位元組(4 b)發(fā)送給MII接口;在發(fā)送過程中,如果MAC檢測到該幀的長度小于最小幀長(64 B),則進(jìn)行數(shù)據(jù)填充達(dá)到64 B為止。

AFDX發(fā)送部分的狀態(tài)機(jī)如圖6所示,發(fā)送數(shù)據(jù)主要包括等待、數(shù)據(jù)長度檢測、插入前導(dǎo)碼和幀起始界定符、數(shù)據(jù)發(fā)送以及CRC校驗(yàn)結(jié)果狀態(tài)。系統(tǒng)在工作的時候,一直處于wait狀態(tài),當(dāng)需要發(fā)送數(shù)據(jù)的時候,狀態(tài)機(jī)將進(jìn)入下一個狀態(tài)從而開始數(shù)據(jù)的發(fā)送。

接收為發(fā)送的反過程,首先對接收到的4位信息進(jìn)行幀檢測,當(dāng)檢測到前導(dǎo)碼和幀起始定界符的時候,則認(rèn)為一幀數(shù)據(jù)接收到了,然后開始對數(shù)據(jù)幀進(jìn)行解析,得到幀數(shù)據(jù)中的各類數(shù)據(jù)信息。

AFDX接收過程如下:數(shù)據(jù)通過PHY芯片解碼后進(jìn)入到MAC 核,然后進(jìn)入接收FIFO。當(dāng)MAC接收到數(shù)據(jù)有效后,從MII接口讀入數(shù)據(jù)后檢測前導(dǎo)碼和幀起始定界符,當(dāng)檢測到有效的幀起始定界符,就會開始對幀長進(jìn)行計(jì)數(shù)。接收模塊在接收數(shù)據(jù)的過程中將已接收到的幀的前導(dǎo)域,SFD域,CRC域和PAD域進(jìn)行剝離。

2 基于MicroBlaze的軟件設(shè)計(jì)

2.1 設(shè)計(jì)說明

在MicroBlaze中將主要完成AFDX協(xié)議棧中UDP層和IP層的數(shù)據(jù)發(fā)送和接收部分,對數(shù)據(jù)進(jìn)行封裝、解析和控制。發(fā)送部分主要完成以下幾個工作:當(dāng)一個幀數(shù)據(jù)進(jìn)入AFDX端口時,發(fā)送部分就開始對該幀數(shù)據(jù)進(jìn)行封裝,其中UDP層將對數(shù)據(jù)添加UDP頭,包括源和目標(biāo)UDP端口號。IP層將UDP層處理完的數(shù)據(jù)添加IP 包頭和以太網(wǎng)頭,然后送入虛鏈路層并添加序列號。接收部分主要完成如下幾個工作:當(dāng)一個幀信號通過PHY解碼送入MAC后,通過接收FIFO送入AFDX接收模塊,那么接收過程開始。在鏈路層首先對該幀信號進(jìn)行完整性檢測和冗余管理,然后進(jìn)入IP層,進(jìn)行IP 校驗(yàn)和檢查,然后送入U(xiǎn)DP層,通過多路分配器后將對應(yīng)的幀數(shù)據(jù)發(fā)送出去,實(shí)現(xiàn)數(shù)據(jù)的解封裝功能。

2.2 設(shè)計(jì)流程

基于MicroBlaze的系統(tǒng)設(shè)計(jì)需要分別對系統(tǒng)的硬件和軟件進(jìn)行協(xié)同編譯。完成MicroBlaze的軟件設(shè)計(jì)之后,將MicroBlaze作為ISE工程下的一個子模塊進(jìn)行調(diào)用。為了驗(yàn)證程序的正確性,利用ISE調(diào)用ModelSim對其進(jìn)行仿真。具體做法是在ISE工程中添加一個以MicroBlaze處理器為基礎(chǔ)的IP核,并編寫測試文件,為處理器的輸入信號提供激勵,輸出信號提供端口。

3 測試與驗(yàn)證

兩個MAC核的仿真意義是相同的,所以針對第一個MAC核的仿真波形進(jìn)行說明。mii_tx_en_0為幀使能信號,當(dāng)MAC核正常工作時,有數(shù)據(jù)發(fā)送的時候該信號為1;當(dāng)發(fā)送為0的時候,該信號使能為0,mii_txd_0為發(fā)送的數(shù)據(jù)。當(dāng)有接收信號進(jìn)入MAC核時,mii_rx_dv_0為高電平,對應(yīng)的數(shù)據(jù)為接收的數(shù)據(jù);當(dāng)接收的數(shù)據(jù)發(fā)生錯誤時,mii_rx_er_0會出現(xiàn)高電平,如果接收到的數(shù)據(jù)沒有發(fā)生錯誤,那么該信號為低電平。

在接收端,判斷接收數(shù)據(jù)的CRC計(jì)算結(jié)果是否為0,如果為1,則表明接收過程中有CRC校驗(yàn)錯誤。CRC 校驗(yàn)?zāi)K的仿真結(jié)果如圖11所示。由圖11可以看出,對接收到的數(shù)據(jù)以及發(fā)送過來的這些數(shù)據(jù)的CRC 校驗(yàn)值(d19167bc)一起計(jì)算,計(jì)算出來的校驗(yàn)值為0,證明接收的數(shù)據(jù)沒有問題。

規(guī)整模塊的仿真數(shù)據(jù)如圖12所示。此處接收到的數(shù)據(jù)位1,2,3,4,…是不等間隔的,通過規(guī)整之后輸出的數(shù)據(jù)1,2,3,4是等間隔的,這個模塊的初始輸出數(shù)據(jù)是錯誤的,所以會重復(fù)輸出第一幀的數(shù)據(jù),后面將輸出正確的數(shù)據(jù)。

主機(jī)要發(fā)送數(shù)據(jù)時,首先給MAC的發(fā)送緩存中發(fā)送數(shù)據(jù)。發(fā)送緩存接收到的數(shù)據(jù)與設(shè)定值相符時,開始進(jìn)行長度檢測,檢測完成后,數(shù)據(jù)發(fā)送模塊開始進(jìn)行幀間隔計(jì)時。根據(jù)幀計(jì)數(shù)器的值開始發(fā)送幀的前導(dǎo)碼、幀起始定界符,將4位數(shù)據(jù)發(fā)送給MII接口,最后把數(shù)據(jù)從物理層發(fā)送到網(wǎng)絡(luò)介質(zhì)上。發(fā)送模塊的仿真結(jié)果如圖13所示。

此處仿真波形的信號i_start_or_not為高電平時,AFDX 發(fā)送模塊開始工作,i_data為需要發(fā)送的數(shù)據(jù),i_data_number為需要發(fā)送數(shù)據(jù)的個數(shù),i_aim_address 為發(fā)送信號的目標(biāo)地址,i_orig_address為發(fā)送的源地址,i_head_ip為發(fā)送信號的IP頭,i_head_udp為發(fā)送信號。當(dāng)發(fā)送開始時,系統(tǒng)首先檢測需要發(fā)送的數(shù)據(jù)長度,如果數(shù)據(jù)長度大于64,則開始發(fā)送,如果發(fā)送數(shù)據(jù)長度小于64,那么進(jìn)行填充,補(bǔ)充到64為止。通過AFDX發(fā)送模塊,得到發(fā)送的幀數(shù)據(jù)o_AFDX_data以及幀信號對應(yīng)的幀使能信號o_afdx_frame,完成了數(shù)據(jù)的正常發(fā)送。

接收模塊的仿真結(jié)果如圖14所示。當(dāng)外部數(shù)據(jù)通過PHY解碼后進(jìn)入MAC核,接收端開始進(jìn)入接收狀態(tài)機(jī),首先檢測前導(dǎo)碼和幀起始界定符。如果檢測正確,那么系統(tǒng)進(jìn)入下一個狀態(tài)。從圖14的仿真結(jié)果可以看出,當(dāng)檢測完前導(dǎo)碼和幀起始界定符時,current_state將進(jìn)入下一個狀態(tài)。然后開始接收數(shù)據(jù),o_data就為接收到的數(shù)據(jù)。

4 結(jié) 論

本文在對航空全雙工以太網(wǎng)(AFDX)協(xié)議深入研究的基礎(chǔ)上,介紹了一種通用信號處理平臺中的一塊AFDX接口板卡,該板卡扣在相應(yīng)的XMC載卡上應(yīng)用于CPCI系統(tǒng)中。該板卡XMC傳輸速率為3.125 Gb/s,可高速傳輸RapidIO協(xié)議數(shù)據(jù),兼容32 b PCI接口和LINK口協(xié)議。由于該板卡支持多種接口模式的背板,為各種高速板卡之間的互聯(lián)提供了平臺。

基于AFDX接口板卡,采用FPGA設(shè)計(jì)了一種AFDX端系統(tǒng)接口功能的實(shí)現(xiàn)方法,該方法基于FPGA的硬件設(shè)計(jì)和基于MicroBlaze的嵌入式軟件設(shè)計(jì),采用FPGA和PHY芯片實(shí)現(xiàn)End System端的AFDX接口,完成傳輸層(UDP)、網(wǎng)絡(luò)層(IP)、鏈路層(Virtual Link)及物理層(PHY)四層協(xié)議數(shù)據(jù)傳輸,使得該接口具備實(shí)時、可靠傳輸AFDX 數(shù)據(jù)的能力。由于該網(wǎng)絡(luò)協(xié)議比較復(fù)雜,開發(fā)設(shè)計(jì)具有一定難度。本文的設(shè)計(jì)基本實(shí)現(xiàn)了AFDX端系統(tǒng)的接口發(fā)送和接收功能,基本達(dá)到了預(yù)期目標(biāo)。AFDX端系統(tǒng)作為AFDX網(wǎng)絡(luò)協(xié)議的重要組成部分,為航空電子系統(tǒng)提供了安全可靠的數(shù)據(jù)交換服務(wù)接口,今后必會得到更加廣泛的應(yīng)用。

參考文獻(xiàn)

[1] 李亮.淺談航空電子全雙工交換式以太網(wǎng):AFDX[J].飛機(jī)工程,2006(3):48?50.

[2] 沈磊.航空全雙工以太網(wǎng)(AFDX)交換機(jī)關(guān)鍵技術(shù)研究與實(shí)現(xiàn)[D].西安:西安電子科技大學(xué),2009.

[3] 林琳.基于FPGA的雷達(dá)信號處理板設(shè)計(jì)與實(shí)現(xiàn)[J].現(xiàn)代電子技術(shù),2014,37(11):51?56.

[4] PCI Industrial Computer Manufacturers Group. Compact PCI specification: PICMG 2.0 revision 3.0 [R]. US: PCI Industrial Computer Manufacturers Group, 1999.

[5] ARINC. ARINC 664 part 7 specification: aircraft data network part 7 avionics full duplex switched Ethernet (AFDX) network [R]. US: ARINC, 2004.

[6] 田耘,徐文波.Xilinx FPGA開發(fā)實(shí)用教程[M].北京:清華大學(xué)出版社,2008.

[7] 夏宇聞.Verilog 數(shù)字系統(tǒng)設(shè)計(jì)教程[M].北京:北京航空航天大學(xué)出版社,2004.