基于SPI總線FLASH時序控制的FPGA實現

薛宏亮 合肥工業大學儀器科學與光電工程學院 安徽合肥 230009

?

基于SPI總線FLASH時序控制的FPGA實現

薛宏亮 合肥工業大學儀器科學與光電工程學院 安徽合肥 230009

【文章摘要】

FLASH存儲器又稱為閃存,它集合了RAM和ROM的長處,不僅可以快速地讀寫數據,又可以使數據在掉電時不會丟失。所以,近年來,FLASH存儲器在嵌入式系統中扮演著越來越重要的角色,而以FPGA作為控制核心的FLASH存儲系統也受到了越來越廣泛地應用。本文介紹了一種SPI接口FLASH時序控制器的設計過程,并用Verilog硬件描述語言實現整個時序控制功能,將其嵌入到FPGA的設計之中。在Modelsim中對設計進行仿真驗證,結果正確可靠,具有普遍的適用性。

【關鍵詞】

SPI總線FLASH ;時序控制;FPGA

圖1 FLASH數據讀取時序圖

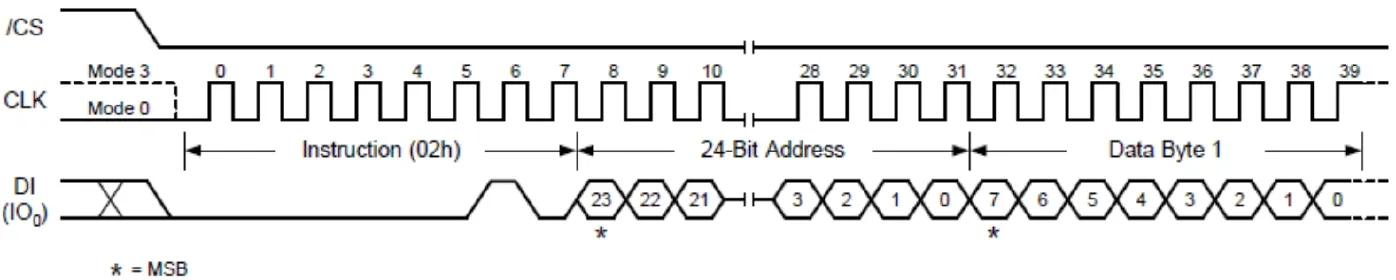

圖2 頁編程命令時序圖

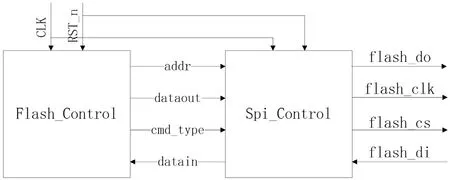

圖3 FLASH讀寫模塊框圖

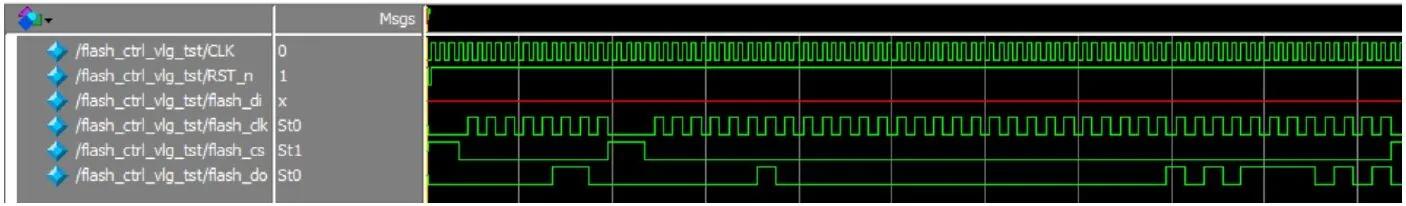

圖4 FLASH控制時序仿真

0 引言

FLASH存儲器作為一類新型存儲器,因具有功耗低、速度快、容量大、成本低和非易失性等優點在各種嵌入式系統中得到越來越廣泛地應用。隨著技術的發展和需求的提高,數據的處理日益向著高速化的趨勢發展,此時,通過普通的處理器來讀取FLASH中的數據已經達不到要求。而利用FPGA控制FLASH存儲器的讀取可以達到較高的處理速度,所以在高速數據處理領域,利用FPGA實現FLASH存儲系統控制的工程應用相當廣泛。本文以winbond公司的SPI接口FLAH芯片W25Q128BV和Altera公司的Cyclone系列FPGA芯片EP4CE6F17C8為例,用Verilog硬件描述語言實現了以SPI總線協議為基礎的FLASH讀取控制時序,實現了FPGA和FLASH存儲器的接口操作。

1 SPI總線協議和W25Q128BV芯片介紹

1.1SPI總線協議

SPI(Serial Peripheral Interface)是一種高速的、全雙工、同步的通信總線。由于其在芯片管腳上只占用4根線,節約了管腳資源的同時也為PCB布局節省了空間,因而越來越多的芯片集成了這種通信協議。

SPI的通信原理簡單,它以主從模式工作,通常需要一個主設備和一個或者多個從設備,需要至少4根線,分別是SDI(數據輸入)、SDO(數據輸出)、SCLK(時鐘)、CS(片選)。其中SDI用于主設備數據輸入,從設備數據輸出;SDO用于主設備數據輸出,從設備數據輸入;SCLK為時鐘信號,必須由主設備提供;CS為從設備使能信號,由主設備控制。SPI是串行通信協議,SDI和SDO 與SCLK同步,是基于SCLK提供的時鐘脈沖完成數據的逐位傳輸。

1.2W25Q128BV芯片介紹

W25Q128BV是winbond公司開發的128Mbit SPI接口的串行FLASH存儲芯片,由于它所需引腳少,功耗低,所以通常作為空間、引腳和功耗有限的系統的存儲設備。它的存儲陣列由65536頁可編程的頁組成,每頁為256字節的存儲空間,它可以一次性被編程。W25Q128BV有4096個可擦除選擇器,每個選擇器可以選擇16頁為一組進行擦除;或者是256個可擦除塊,每塊為64KB。

W25Q128BV不僅支持標準的串行外設接口,而且還支持更高性能的雙向或者四向的輸出。標準的接口時鐘可以高達104MHz。本文介紹標準SPI接口模式的FLASH讀取時序的控制。

2 FLASH控制模塊設計

FPGA對FLASH的控制都是通過命令的方式進行的,不管是讀、寫、擦除或者其他操作,首先在第一個字節要對W25Q128BV寫入命令號。根據命令格式的不同,再寫入地址和數據;或者讀取數據。但是,無論是命令的寫入,還是數據和地址的寫入,亦或是數據的讀取都是按照SPI總線協議進行的。

2.1FLASH讀寫時序分析

FLASH讀取數據命令允許從存儲單元中依次讀取一個或者多個字節的數據。該命令需要先發送命令字03,再發送24位地址,然后接受數據。命令字和地址在時鐘的上升沿被FLASH鎖存,當地址被接收后,對應的存儲單元中的數據在時鐘的下降沿出現在DO引腳。數據讀取命令的時序圖如圖1所示。

FLASH寫入數據必須先發送寫使能命令字(06),再發送頁編程命令(02)。頁編程命令之后需跟隨24位地址,然后寫入256個編程數據。數據都在時鐘的上升沿采樣。也頁編程命令時序圖如圖2所示。

2.2FLASH讀寫模塊設計

為了實現FLASH讀寫控制,必須嚴格按照FLASH讀寫時序進行設計。本次設計的讀寫模塊主要由Spi_Control和Flash_Control兩個子模塊組成。其中Spi_Control模塊主要完成SPI接口時序的產生和命令的譯碼;Flash_Control模塊則主要實現命令的控制。

3 FLASH讀寫時序仿真

為了驗證FLASH控制時序的正確性,將Verilog HDL代碼在Modelsim SE10.0c軟件中進行仿真。由于FLASH讀取需要連接硬件,且其基本時序與FLASH寫入時序類似,故本次設計僅進行FLASH寫入時序仿真。本設計仿真向地址為10的FLASH存儲單元寫入一個字節的數據0xF5,對應的波形仿真圖如圖4所示。

4 總結

FLASH存儲器因其優異的性能在嵌入式存儲系統中得到越來越廣泛的應用。本設計以FPGA為主控芯片,采用Verilog HDL模塊化設計方法,完成了基于SPI接口的FLASH存儲芯片的讀寫控制設計,詳細地介紹了FLASH控制時序及其模塊化設計流程,最后完成了控制時序的仿真,驗證了設計的準確性,具有廣泛的應用價值。

【參考文獻】

[1]鄭文靜,李明強,舒繼武.Flash存儲技術.計算機研究與發展,2010.

[2]陳明義,連帥軍,周建國.基于FPGA的FLASH控制器系統設計及實現.電子科技,2008.

[3]Winbond Corporation.W25Q128BV-3V 128M-BIT SERIAL FLASH MEMORY WITH DUAL AND QUAD SPI.2011.

[4]王誠,蔡海寧,吳繼華.Altera FPGA/CPLD設計(第2版).北京:人民郵電出版社,2011.

[5]夏雨聞.Verilog數字系統設計教程(第二版).北京:北京航空航天大學出版社,2008.