信號完整性量測技術簡介

劉向紅,張時光

(鴻富錦精密電子 天津300462)

信號完整性量測技術簡介

劉向紅,張時光

(鴻富錦精密電子 天津300462)

在產品開發的模型階段,需要通過信號完整性量測來確定產品高速信號傳輸品質。因此從事數據處理和數據傳輸設計任務的工程師,必須了解信號完整性基礎知識,掌握必要的信號量測技能。以主板QPI和DMI信號完整性量測為實例,介紹了如何進行相關技術量測。

高速信號 信號完整性 數據傳輸

0 引 言

信號完整性是指信號按照設計標準,完整到達接收端并被接收。研究信號完整性的目的就是要確保傳輸的信號被準確接收,避免信號在傳輸中被吸收降解,同時確保信號不損壞任何設備以及不污染電磁頻譜。

1 信號完整性概述

1.1 高速信號傳輸線效應

信號在低速傳輸時,如果傳輸介質不是特別長,一般來說頻率響應對信號的影響很小。然而,隨著速度的增加,高頻效應也隨之增加,較短的傳輸線路也可以發生如振鈴、串擾、反射和地彈等問題,嚴重阻礙了信號的完整性效果。

因此,傳統意義的數字電路設計不會受到傳輸線效應的影響,因為在較低頻率的傳輸線路中,信號傳輸能夠達到所期望的數據特征。但是,隨著系統速度的提升,較高的數據傳輸頻率就意味著信號不僅具有數字屬性,還會產生系統內的模擬效應等問題。典型情況如:為了提高I/O接口和存儲器接口的數據傳輸速率,特別是被嵌入到FPGA中的高速收發器,就會發生此類傳輸效應。

1.2 如何解決信號傳輸線效應

傳輸線效應在發送數據時表現得非常顯著,但可以通過遵循良好的設計技巧和簡單的布局指南來克服這類信號傳輸問題。

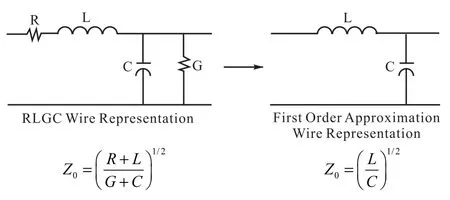

傳輸線可以被定義為一個在發送機和接收器之間載有信號的導體。傳統意義上,傳輸線也可以被看作是基于電信電纜的長距離操作。但是,伴隨高速數字信號的傳輸,即便最短的被動式印刷電路板(PCB)的走線也會受到傳輸線效應的影響。低頻率的傳輸線或PCB走線是無電阻、電容或電感的理想電路,但在高頻率下,受交流電路特性支配,引發阻抗、電感和電容效應的情況非常普遍。通過電路模型可以計算這類效應(見圖1),也可以用于確定傳輸線或PCB走線的特性阻抗。這個導線阻抗是非常重要的,因為任何傳輸路徑內的不匹配都將導致信號質量的降低。

圖1 傳輸線電路示意圖Fig.1 Schematic of the circuit of transmission line

1.3 阻抗失配和信號完整性

輸出源(ZS)、線(ZO)和接收器或負載(ZL)的不相等阻抗,導致信號傳輸線路阻抗失配。這意味著發送的信號沒有完全被接收器所吸收,多余的能量被反射回發射機。這個過程繼續往復多次,直至所有的能量被吸收。高速率數據傳輸過程能引起信號上沖、下沖、振鈴和階梯波形,從而產生信號誤差。阻抗失配可以通過為收發緩沖器選擇適宜且匹配的傳輸介質來克服。如果是印刷電路板,可以通過仔細選擇在介質材料和通過使用終端方案來消除這種阻抗的失配性。用于克服阻抗失配的終端方案取決于實際應用情況。該方案包括簡單的并行終端(見圖2)和更復雜的RC終端電路,終端在一個電阻電容網絡提供了一個低通濾波器,以消除低頻率的影響。

圖2 簡易并行終端Fig.2 A simple parallel terminal

雖然簡單的外部組件并行端有助于解決阻抗不匹配,但這依賴于電路板的穩定性。此外,如果缺少線路補償,可能會導致進一步的訊號反射。Altera?高速I/O解決方案提供了集成于設備上的可編程控制終端,用于減少對外部組件的依賴。Stratix? II、Stratix和Stratix GX設備則可提供集成于設備一體化的終端技術解決方案。這一技術可為接收器和發射器提供串聯、并聯和差分I/O高速的驅動阻抗匹配。在高速收發器電路內部,Stratix GX器件收發模塊還提供一個可編程控制終端方案,以支持最高速I/O標準。

1.4 訊號衰減與信號完整性

高頻訊號傳輸線的損耗使接收機難以準確地解釋信息。從傳輸介質方面考慮,以下兩種原因會引起傳輸線損耗。

1.4.1 介電吸收

高頻訊號激發絕緣體內的絕緣分子,使絕緣子吸收訊號能量,從而降低了信號強度。介電吸收與印刷電路板材料有關,通過選擇材料可以減少信號的能量損失。

1.4.2 皮層效應

因交流和高頻訊號產生的各種電流波形會在導體的表面傳導引發材料的自感,產生新的高頻率電感電抗,迫使電子運動到材料的表面,這可以有效減少導電面積,但會額外增加電阻,致使訊號衰減。雖然增加導線寬度可以減少皮層效應,但并不適用于所有的情況。圖3展示了一個印刷電路的橫截面視圖Board(PCB)板。

圖3 皮層效應示意圖Fig.3 Schematic of skin effect

選擇合適的絕緣材料和進行合理的線路布局可以有效降低信號的衰減。此外,以下特性也會降低信號衰減:

①可編程差分輸出電壓(VOD):通過VOD編程設置,確保阻抗和線路長度產生的驅動力相等。通過增加差分驅動電壓,提高接收機的信號強度。②預強調:為減少高頻信號的衰減,只通過提高信號強度是不夠的,因為噪聲和抖動也會得到加強。預強調的目的是只提高高頻信號分量,通過增加第1個發送符號的強度水平,后續的符號強度水平是不變的。例如,如果信號傳輸一個高層次上的3個符號,只有第1個符號會得到加強,接下來的兩個符號則在通常的水平上傳輸。圖4說明了預強調的原理。如果單個符號在高電平狀態傳輸,則這個符號也會得到加強。預強調也是克服相關抖動造成的振幅損失、時間位移和圓形信號邊緣等影響的關鍵模式。③接收機均衡:用于補償線路損耗導致的低頻分量信號的衰減。

圖4 預強調示意圖Fig.4 Schematic of Pre-emphasis

1.5 串擾和信號完整性

當信號沿著線路傳輸,導線周圍就會產生磁場。如果兩個導線相鄰,則兩個磁場就有可能相互作用,造成信號之間的交叉耦合,這種現象稱為串擾。互感和互容兩種類型的能量耦合是產生串擾的主要原因。

1.6 減少串擾的技術

以下的電路板(PCB)設計技術可以顯著減少細微帶線路或帶狀線布局的串擾:①在布局允許的條件下,擴大信號線間的距離;②設計輸電線路時,使導線盡可能接近地層,有助于從相鄰的信號中去除耦合;③如果布局條件允許,盡可能使用差分技術,關鍵網絡尤為如此;④如果不同層信號有顯著的耦合,則可能讓線路在不同層正交;⑤減少信號并行長度,縮短路由平行段的長度,并盡量減少網絡間的長耦合區段。

1.7 同步開關輸出(SSO)對信號完整性的影響

隨著數字電路速度的提升,輸出開關的次數逐漸減少,導致內部輸出時負載電容放電產生更高的瞬態電流。如果多個輸出開關同時從高邏輯到低邏輯,會導致存儲在I/O負載電容的電荷流入裝置充電,形成一個電壓,這種低電壓信號被稱為地面反彈。相對于設備工作狀態中的高電位,反彈效應會引發低輸出。接地反彈效應可通過一系列的PCB設計進行降低,如Altera公司發布的《AN 224:高速電路板布局準則》中提出的解決方案是針擺率控制,從而減少地面反彈。

2 信號完整性量測過程

2.1 選擇判定標準

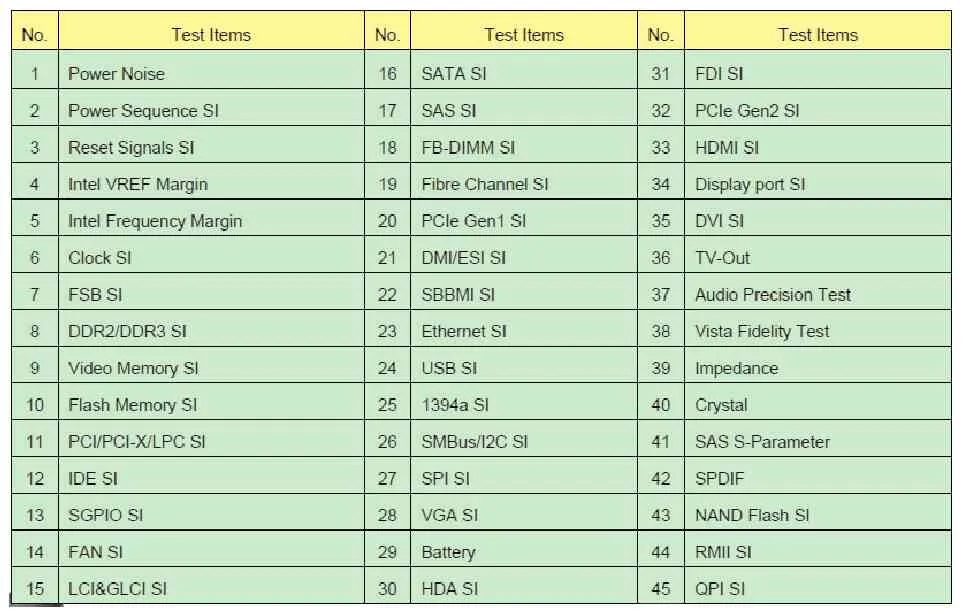

表1為各類接口界面的功能信號,均有業界定義的傳輸標準。用戶可根據所要量測的信號頻率,選擇適合帶寬的示波器。

表1 接口界面功能信號分類Tab.1 Categorization of functional signals at interface

2.2 選擇適合的量測方法(見圖5)

圖5 信號測試方法示意圖Fig.5 Schematic of signal measuring methods

3 信號品質分析

3.1 電壓參數

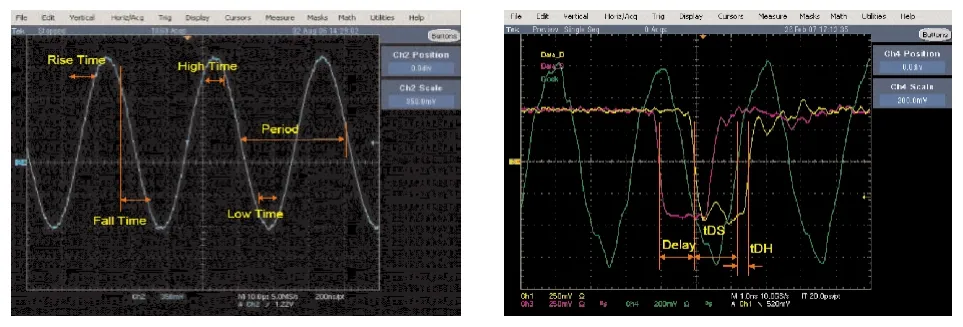

通過電壓波形的波幅,上升下降和高低點、均值或均方根等參數指標來判斷電壓是否存在超出、不足或回彈,發生過于接近邊界值、波紋或脈沖干擾,發生波形下垂及異常壓降等情形,如圖6所示。

圖6 電壓波形示意圖Fig.6 Schematic of voltage waveforms

3.2 時序參數

通過上升下降時序、高低時序、周期和頻率,或設定時間、保持時間、占空比、延遲、偏離、抖動及轉換、瞬變等來判定信號品質,如圖7所示。

圖7 時序信號示意圖Fig.7 Schematic of sequence signals

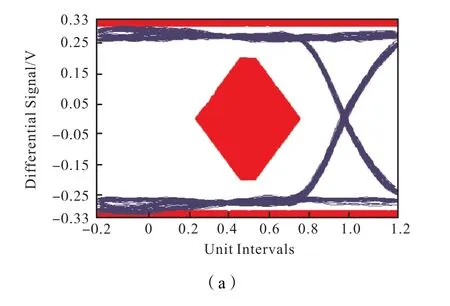

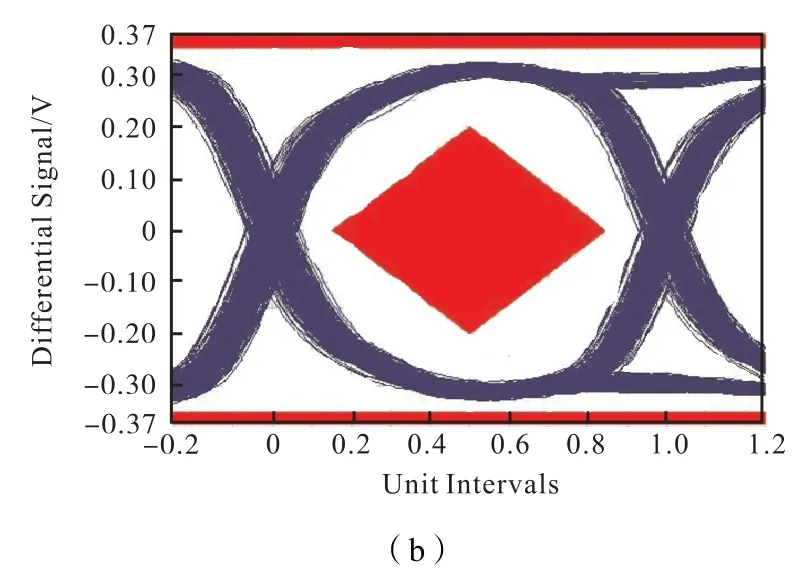

3.3 眼圖分析

3.3.1 眼圖定義

為了衡量基帶傳輸系統的性能優劣,在實驗室中,通常用示波器觀察接收信號波形的方法來分析碼間串擾和噪聲對系統性能的影響,這就是眼圖分析法。如圖8所示,如果將輸入波形輸入示波器的Y軸,當示波器的水平掃描周期和碼元定時同步時,適當調整相位,使波形的中心對準取樣時刻,在示波器上顯示的圖形很像人的眼睛,因此被稱為眼圖(Eye Map)。

圖8 眼圖示意圖Fig.8 Schematic of Eye Map

3.3.2 眼圖分析

通過眼圖的高度和寬度、上升下降時間、差分電壓、去加重、單位間隔、共模電壓、比特率等參數,分析信號質量。二進制信號傳輸時的眼圖只有一只“眼睛”,當傳輸三元碼時,會顯示兩只“眼睛”。眼圖是由各段碼元波形疊加而成的,眼圖中央的垂直線表示最佳抽樣時刻,位于兩峰值中間的水平線是判決門限電平。在無碼間串擾和噪聲的理想情況下,波形無失真,每個碼元將重疊在一起,最終在示波器上看到的是跡線又細又清晰的“眼睛”,“眼”開啟得最大。當有碼間串擾時,波形失真,碼元不完全重合,眼圖的跡線就會不清晰,引起“眼”部分閉合。若再加上噪聲的影響,則使眼圖的線條變得模糊,“眼”開啟得小。因此,“眼”張開的大小表示了失真的程度,反映了碼間串擾的強弱。由此可知,眼圖能直觀地表明碼間串擾和噪聲的影響,可評價一個基帶傳輸系統性能的優劣。此外,也可以用此圖形對接收濾波器的特性加以調整,以減小碼間串擾和改善系統的傳輸性能。

通過眼圖可以看出:①眼圖張開的寬度決定了接收波形可以不受串擾影響而抽樣再生的時間間隔。顯然,最佳抽樣時刻應選在眼睛張開最大的時刻。②眼圖斜邊的斜率,表示系統對定時抖動(或誤差)的靈敏度,斜率越大,系統對定時抖動越敏感。③眼圖左(右)角陰影部分的水平寬度表示信號零點的變化范圍,稱為零點失真量,在許多接收設備中,定時信息是由信號零點位置來提取的,對于這種設備零點失真量很重要。④在抽樣時刻,陰影區的垂直寬度表示最大信號失真量。⑤在抽樣時刻,上、下兩陰影區間隔的一半是最小噪聲容限,噪聲瞬時值超過它就有可能發生錯誤判決。⑥橫軸對應判決門限電平。

4 測試結果及改進設計案例

4.1 Clock slew rate fail

如圖9所示,通過信號完整性測試結果發現,HAD_BCLK比特率低于標準值1~3,V/ns,需要工程師分析原因。如果是因為輸入信號線路阻值不匹配,則可以通過調整輸入阻值來改進設計,使信號下降過程的比特率符合標準。這樣就能確保產品通訊功能的正常。

圖9 比特率示意圖Fig.9 Schematic of bit rate

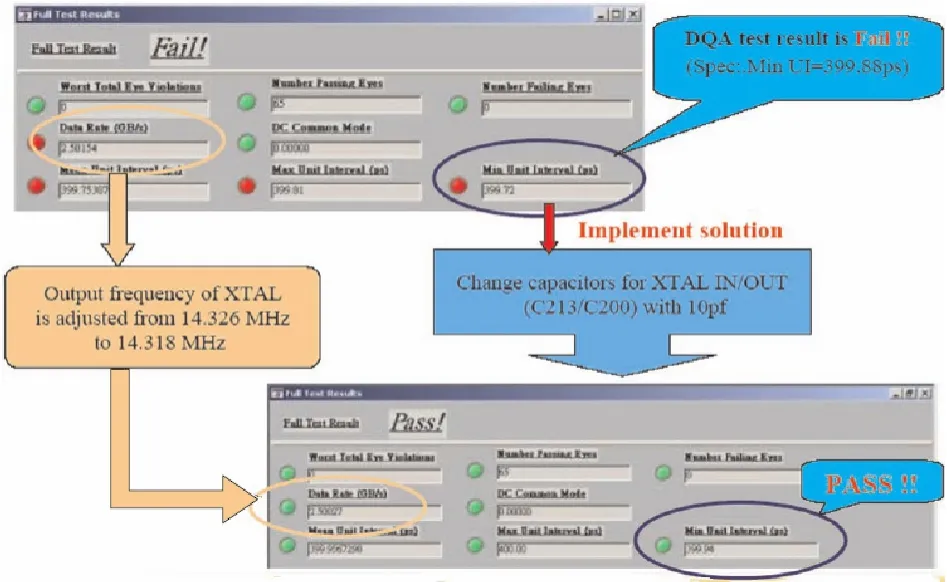

4.2 PCIe signal fail

如圖10所示,當量測到PCIe內部傳輸速率最大值略低于規格標準值399.88,ps時,則通過調整晶振14.326,MHz到14.318,MHz,同時調整晶振配對的電容值到10,pf,再次測試后結果符合標準。

圖10 PCIe測試及改進Fig.10 PCIe test and improvement

4.3 SATA signal fail

如圖11所示,SATA信號測試時,發現眼圖開度太大,裕量超出規格值,則首先檢查示波器帶寬和探頭的選擇是否合適。通過調整電路的誤碼率,即減少碼間串擾和噪音,得到理想眼圖,即高品質數字信號。

圖11 眼圖示意圖Fig.11 Schematic of Eye Map

5 結 論

高速信號的設計工作需要面對額外的挑戰,以確保信號的完整性。設計人員需遵循一些簡單的模擬設計規則并應用印刷電路板布局技術。Altera公司的高速可編程邏輯設備支持高速設計。在Stratix GX的帶寬范圍內,可編程轉換速率范圍控制技術和設備終端技術在標準高速I/O起到增強功能,如可編程驅動強度、預強調、高速和接收器均衡收發器接口等,這些功能可以為設計師的工作提供便利。

[1] AN 75:High Speed Board Design [EB/OL]. www. altera. com/literature/an/an075. pdf.

[2] AN 224:High-Speed Board Design Guidelines Using Stratix Devices[EB/OL]. www.altera.com/literature/an/ an224. pdf.

[3] Dally W J,Poulton J W. Digital Systems Engineering[M]. Cambridge:Cambridge University Press,1998.

[4] Johnson H,Graham M. High-Speed Board Design[M]. Upper Saddle River:Prentice Hall,Inc.,1993.

[5] 眼圖的定義與測量方法[EB/OL]. http://wenku.baidu. com/link?url=epMz751XsB-zBeUCoT0LpNDDxSQT7 aowiqZ5h_Fo03jqm4pDjV1gyU6bDv4l5wLlJlGWko1cS rm4eOidoSnB5q2f-kkz2GxB1tHWaeOJCDi.

A Review of Signal Integrity Measurement Technology

LIU Xianghong,ZHANG Shiguang

(HongFuJin Electronic Precision,Tianjin 300462,China)

To ensure the transmission quality of high-speed signal,electronic engineers need to carry out signal-integritymeasurement to determine the high-speed transmission quality in the model stage of product development.Therefore,engineers specializing in data processing and data transmission need to understand the basis of signal integrity and grasp necessary signal measurement skills.This paper takes main board QPI and DMI signal integrity measurement as an example to briefly introduce how to carry out relevant measurements.

high speed signal;signal integrity;Eye Map

U228.2

:A

:1006-8945(2016)09-0077-05

2016-08-08