高速信號抽取抗混疊濾波器的設計

李漢陽

摘要:在通信系統中,常見數字接收機解調器中經常會遇到高速信號抽取的問題,這就會用到多速率數字信號處理技術。在抽取前,需要設計合適的抗混疊濾波器對信號進行濾波處理。在抽取倍數較大的情況下,濾波器階數較多,其延遲時間和硬件消耗較大。本文提出了一種級聯濾波結構,按照文中的參數,在同樣的濾波效果下,方案復雜度降低了90.7%。

關鍵詞:高速率信號 抗混疊 濾波器

中圖分類號:TP274 文獻標識碼:A 文章編號:1007-9416(2016)05-0000-00

通信系統中,常見數字接收機解調器中經常會遇到高速信號抽取的問題,這就會用到多速率數字信號處理技術。在抽取前,需要設計合適的抗混疊濾波器對信號進行濾波處理。在抽取倍數較大的情況下,濾波器階數較多,其延遲時間和硬件消耗較大。本文提出了一種級聯濾波結構,在同樣的濾波效果下,降低了信號處理的方案復雜度。

1參數設置

為了更好地描述上述問題,本文以以下的參數為例進行分析。令接收端接收到載波頻率為30MHz的模擬信號,ADC芯片以24MHz的采樣頻率對模擬信號進行帶通采樣,采樣數據進入解調器,進行的6MHz的數字正交下變頻,信號帶寬為50KHz,正交下變頻后信號采樣率為24MHz。24MHz的信號需要經過100倍降采樣后采樣率為240KHz的信號,處理后再次經過40倍采樣用于其他處理。

2 100倍抽取方案設計

解調器涉及到多速率數字信號處理技術,100倍降采樣及40倍降采樣都需要考慮信號的混疊問題,需要設計合適的抗混疊濾波器在抽取前對信號進行濾波處理。首先討論100倍降采樣濾波器設計。抽取前采樣率為24MHz,抽取比例100,抽取后采樣率為240KHz。由s上節的參數可知,倍抽取前抗混疊濾波器阻帶頻率不能大于120KHz,從而保證抽取后信號不會發生混疊。利用Matlab濾波器設計和分析工具fdatool對濾波器進行設計,參數設置見表1。

由表1可知,在24MHz的采樣率下,一次性實現100倍降采樣需要抗混疊濾波器階數為1716,意味著輸入數據要與濾波器系數做1716次乘法及加法,硬件資源消耗大,濾波器延遲時間長。

為了解決上述的多次乘法的問題,可將抽取過程分解為5*5*4倍抽取的級聯實現100倍降采樣過程:第一次倍抽取無需抗混疊濾波器(信號截止頻率為2.4MHz,噪聲最大帶寬為0.5MHz,小于截止頻率);第二次倍抽取僅需要39階濾波器;第三次倍抽取僅需要69階濾波器;對比以上兩種方案,第二種級聯方案實現簡單,資源消耗小。其參數設置見表2。通過計算可知,采用級聯結構后,所需的乘法次數為39+69=108次,其方案復雜度降低了93.7%。

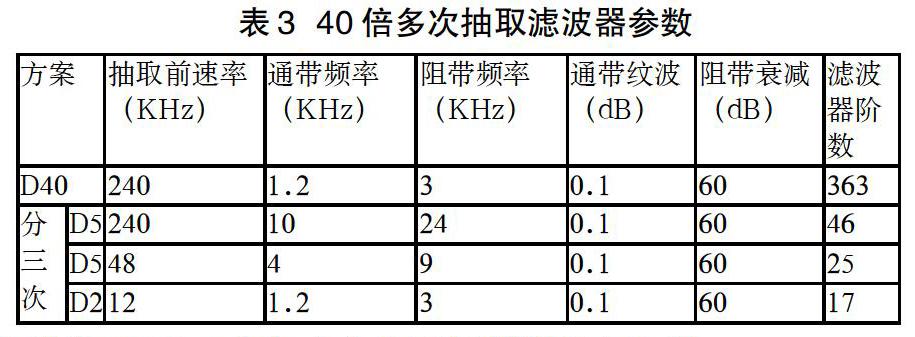

3 40倍抽取過程

從以上可以看出,采用級聯結構的濾波器比直接抽取濾波器階數小,設計簡單,節省硬件資源。100倍抽取采用5*5*4倍抽取級聯的形式完成,40倍抽取則采用5*5*2倍抽取級聯的形式完成,其參數設置見表3所示。可知,40倍的抽取采用多級級聯結構后,方案復雜度降低了(363-46-25-17)/363=75.7%。總體方案復雜度降低了90.5%。

4 其他降低復雜度的方案

此外,可以將5倍、4倍、2倍抽取利用多相濾波實現,不僅降低對實時處理的要求因此,而且模塊可以實現復用,提高效率。工程應用中,當系統設計對資源要求比較高時,可以選擇使用半帶濾波器和CIC濾波器實現濾波及抽取過程。對于40倍抽取來說,可以采用CIC濾波器實現5倍抽取,三級半帶濾波器級聯實現8倍抽取,每級濾波器系數10階左右,資源消耗低,計算速度快;若系統對實時處理要求很高,則建議采用多相濾波結構,增加系統的實時處理能力及吞吐量。

5結語

本文提出了一種級聯濾波結構,在同樣的濾波效果下,將100倍抽取采用5*5*4倍抽取級聯的形式完成,40倍抽取采用5*5*2倍抽取級聯的形式完成,對兩種抽取分別降低了93.7%和75.7%,總體方案復雜度降低了90.7%,很好地減少了資源的消耗并降低了信號處理的延遲時間。

參考文獻

[1]嚴慧,于繼明.基于Matlab的IIR數字濾波器設計[J].軟件導刊,2013,01:110-113.

[2]呂幼新,鄭立崗,王麗華.基于多相濾波的寬帶數字化接收機技術[J].電子科技大學學報,2003,02:133-136.

[3]尚文明. Sigma-Delta ADC數字抽取濾波器的設計與優化[D].電子科技大學,2013.

[4]姜巖峰,張東,于明.數字接收機中CIC濾波器的設計[J].電子測量與儀器學報,2011,08:671-675.

[5]韓計海,吳炳洋.基于MATLAB的高性能半帶濾波器設計[J].信息化研究,2009,06:24-28.