嵌入式控制系統的串口擴展設計方法

西南技術物理研究所 楊光海 彭曉樂 張 川 王 海 孫 海 徐 丹 王之昊

?

嵌入式控制系統的串口擴展設計方法

西南技術物理研究所 楊光海 彭曉樂 張 川 王 海 孫 海 徐 丹 王之昊

【摘要】本文以工程應用為出發點,闡述了在嵌入式控制系統中,兩種不同的實現UART擴展的方法,從而實現不同方式的多串口擴展,以供工程開發者進行選用。 嵌入式;UART;多串口

0 引言

嵌入式系統(Embedded system),是一種“完全嵌入受控器件內部,為特定應用而設計的專用計算機系統”,根據英國電氣工程師協會( U.K. Institution of Electrical Engineer)的定義,嵌入式系統為控制、監視或輔助設備、機器或用于工廠運作的設備。與個人計算機這樣的通用計算機系統不同,嵌入式系統通常執行的是帶有特定要求的預先定義的任務。由于嵌入式系統只針對一項特殊的任務,設計人員能夠對它進行優化,減小尺寸降低成本。

嵌入式控制系統是一個控制程序存儲在ROM中的嵌入式處理器控制板。嵌入式控制系統的核心是由一個或幾個預先編程好以用來執行少數幾項任務的微處理器(DSP或單片機)組成。事實上,所有帶有數字接口的設備,如微波爐、錄像機、汽車等,都使用嵌入式控制系統,大多數嵌入式控制系統都是由單個程序實現整個控制邏輯。

在嵌入式控制系統中,各部件間的計算機微控制芯片(DSP或單片機)都需要進行數據交換建立通訊聯系,使用串行通訊手段是其中一種重要、常用的通訊方式。串行通訊工作方式分為同步方式和異步方式兩種,在實際工作中,異步方式用得最多,本文主要討論異步方式,其包括三個常用的總線標準:RS-232、RS-422、RS-485。

串行通信接口(串口)在嵌入式控制系統數據通信中一直扮演極重要的角色, 具有線路簡單、應用靈活、可靠性高等優點,它不僅沒有因為技術的進步而被淘汰,反而呈現向速度等極限挑戰的趨勢。 串口已成為許多高端C PU和低端單片機的標準配置。但是目前的嵌入式芯片,包括單片機或DSP芯片中,目前最多二個串口,幾乎沒有超過這個數目的,因此,軟件模擬串口的收發工作往往是此類系統的擴展多串口的首選方案,但該方案不僅占用資源,且應用效果并不理想,如何在此類系統中擴展串口,以滿足其具體應用,無疑具有現實意義。

1 串口實現方法

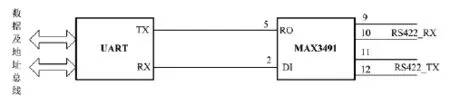

從硬件的角度來說,串口的實現方法是串口驅動芯片配上異步串口收發器UART(Universal Asynchronous Receiver/Transmitter)即可實現。如圖1所示,以MAXIM公司的RS422驅動器MAX3491為例,說明一路異步串口實現的方式。實現多路串口,即實現圖1所示串口的疊加。

圖1 異步串口實現示意圖

一般來說,嵌入式系統中實現多路串口的瓶頸在于微控制芯片(DSP或單片機)的UART端口較少,所以,實現串口擴展的關鍵在于UART的擴展,串口驅動器。實現UART擴展的方法有兩種,一種是利用串口擴展芯片實現,這類芯片較多,例如TI公司的UART擴展器16C550、16C552、16C554、16C754等芯片,一片最多能擴展4路串口,本文以TI公司的TL16C554為例,講述利用UART擴展器擴展串口的方法,另一種是利用FPGA芯片進行串口擴展,在FPGA芯片內以Verilong為硬件描述語言,實現串行通訊的接收模塊和發送模塊,一顆FPGA芯片可實現多路串口的接收模塊和發送模塊。上述兩種方法的基礎上搭配串口驅動芯片,從而實現多路串口的擴展。

2 利用UART擴展器擴展UART的方法

2.1 TL16C654功能特點

TL16C654是TI公司的異步通訊芯片,其主要特點如下:

●具有4通道異步通訊收發器(UART);

●最高可達1Mbits/s的波特率,波特率發生器可軟件編程設置;

●16字節的先進先出存儲器(FIFO),FIFO均可設置觸發中斷字節數;

●標準的異步通訊狀態位,包括起始位,停止位,校驗位;

●每個通道獨立控制發送、接收、線態和數據裝置中斷

●具有可編程的數據格式

數據位長度為5、6、7、8;

可設置為奇校驗、偶校驗、無校驗模式;

停止位長度可設置為1、1.5、2;

●缺省的數據起始位檢測;

●每個通道的數據和控制總線采用三態TTL驅動;

●中斷優先控制系統;

●Modem 控制功能;

TL16C554的主要引腳的功能說明如下:

A0~A2:片內寄存器的選擇信號;

D0~D7:雙向8位數據線信號;

CSA、CSB、CSC、CSD:輸入片選信號,分別能使4個串行通道讀寫操作;

XTAL1、XTAL2:晶振或外部時鐘輸入輸出端,該腳可接外部晶振或時鐘信號;

INTA、INTB、INTC、INTD:4個串行口中斷輸出;

RXA、RXB、RXC、RXD:串行數據輸入引腳;

TXA、TXB、TXC、TXD:串行數據輸出引腳;

RESET:復位信號輸入引腳;

IOR、IOW:輸入/輸出讀/寫選通脈沖。

TL16C554的每路串行UART通道均有10個寄存器可被CPU訪問,這些寄存器分別用于通訊參數的設置、FIFO的控制、對線路及Modem的狀態訪問、數據的發送和接收、中斷管理等功能。編程人員可由A0、A1、A2三條片內寄存器選擇線和線路控制寄存器的除法數鎖存器訪問位LCR及IOR、IOW一起通過多路復用進行訪問或控制TL16C554的任何一個寄存器。表1給出了訪問這些寄存器的LCR、A0、A1、A2以及讀寫的狀態。

2.2 串口擴展的實現

以TL16C654與其他設備進行串行通訊相關的寄存器作簡單介紹。

兩個8位波特率因子寄存器以一個16位的二進制格式存貯波特率因子。波特率因子可通過下列算式求出:

波特率因子=基準時鐘頻率/(16×波特率)

表1 TL16C554的片內寄存器

根據串口波特率,選擇合適的晶振頻率給16C654芯片提供基準時鐘頻率,根據上式計算出波特率因子,以便在軟件編程時設置。寫入波特率因子前必須置線路控制寄存器(LCR)的bit7位為1,寫入波特率因子后應將線路控制寄存器(LCR)的bit7位恢復為0。

將TL16C554芯片的串行串行數據輸入、輸出引腳接在串口驅動芯片的串行數據的輸出、輸入引腳上,如MAXIM公司的MAX3491芯片的DI、RO引腳上,即可以實現串口的擴展。

3 利用FPGA擴展UART的方法

3.1 概述

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

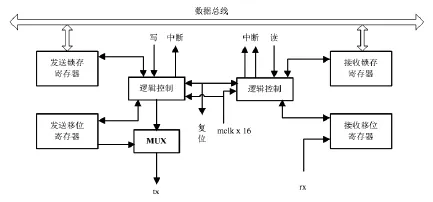

完整的UART接口包括發送鎖存器、發送移位寄存器和邏輯控制組成的發送模塊,以及由接收鎖存器、接收移位寄存器和邏輯控制組成的接收模塊,其UART接口結構圖如圖2所示。

UART的幀格式,一般包括空閑狀態(高電平)、起始位(低電平)、5~8位數據位、校驗位(可選,高電平或低電平)和停止位(高電平,位數可為1、1.5、2位)。

UART包含一個可編程的波特率發生器,可按照需求配置波特率。波特率發生器給串口數據發送模塊和接收模塊提供發送數據和接收數據的基準時鐘信號,其產生的時鐘mclk x 16 是串行數據波特率的16倍,它對系統時鐘的n分頻,n=系統時鐘/波特率 x 16,可根據需要的波特率設置相應的數值。

圖2 UART接口結構

3.2 發送模塊設計

當數據總線上并行的8位數據從總線寫入發送模塊后,發送模塊將并行數據裝入鎖存器中,然后在位移寄存器中將數據移位,產生完成的發送序列(包括起始位,數據位,校驗位和停止位),以相應的波特率從tx發送。

發送模塊部分Verilong程序如下:

.cpu_clk(cpu_clk),

.send_clk(clk_out),

.rst_n(rst_n),

.cpu_write(cpu_write),

.cpu_ce(cpu_ce),

.cpu_data(cpu_data),

.cpu_add(cpu_add),

.send_flag(send_flag),

.uart_txdata(uart_txdata),

.s_full_bit(s_full_bit),

.s_empt_bit(s_empt_bit)

3.3 接收模塊設計

接收模塊首先捕捉起始位,在mclk x 16時鐘下不斷檢測從rx端輸入數據的起始位,當檢測到起始位后,接收模塊由空閑模式轉換為移位模式,并且16分頻mclk x 16產生rxlk時鐘的上升沿位于串行數據每一位的中間,這樣接下來的數據在每一位的中點采樣。然后由rxclk控制在上升沿將數據位寫入移位寄存器rsr的rsr[7]位,并且rsr右移1位,依次將8位數據全部寫入rsr,并且停止產生rxckl波特率時鐘。判斷檢驗位、幀結構正確后,rsr寄存器中的數據寫入數據鎖存寄存器中,最后由8位數據總線輸出轉換完成的數據。

接收模塊部分Verilong程序如下:

.rst_n(rst_n),

.rx_clk(clk_16_out),

.rx_data_ready(rx_data_ready),

.rx_data (rx_data),

.num_to_int(num_to_int),

.aclr(aclr),

.int_choose(int_choose),

.cpu_clk(cpu_clk),

.cpu_read(cpu_read),

.cpu_add(cpu_add),

.cpu_ce(cpu_ce),

.cpu_int(cpu_int),

.r_fifo_bit(r_fifo_bit),

.r_over_bit(r_over_bit)

4 結束語

通過UART的擴展實現了串口的擴展,采用UART擴展器的方法具有工作穩定,具有一定FIFO深度,不需額外增加軟件開發、管理的成本,但是使用的靈活不夠。采用FPGA擴展UART的方法使用靈活性強,但需額外增加軟件開發、管理的成本。用戶可以根據實際使用情況選用UART的擴展方法,以提高工作效率。

參考文獻

[1]朱學明,丁萬山.一種基于TL16C554A的DSP多串口擴展方法[J].微處理機,2006,6:24-27

[2]田紅霞,戴彥,鹿玉紅.基于FPGA的RS232串行接口設計[J].煤炭技術,2010,9(29):194-196.

[3]李金力,劉文怡,彭旭峰.基于FPGA的RS232異步串行口IP核設計[J].電子設計工程,2009,8(17):31-31,35.

[4]Texas Instruments.TL16C554,TL16C554I ASYNCHRONOUS COMMUNICATIONS ELEMENT.

[5]MAXIM,3.3V-Powered,10Mbps and Slew-Rate-LimitedTrue RS-485/RS-422 Transceivers.

楊光海(1978—),大學本科,工程師,研究方向:嵌入式控制。

作者簡介: