基于FPGA的CMOS線陣圖像傳感器數據采集系統設計

樊紅星+張小超+劉磊+周鵬+趙博

摘 要: 針對日本濱松公司的CMOS線陣圖像傳感器G9214?512S,設計基于FPGA的同步工作模式的圖像數據采集系統,使用VHDL語言對此系統進行描述,并用Xilinx ISE Design Suit自帶的ISim軟件對設計的時序進行仿真。采用Xilinx公司的Spartan 3 XC3S200A?4VQ100進行FPGA配置和驗證,仿真結果表明該數據采集系統的時序正確,具有較高的實用價值。

關鍵詞: FPGA; CMOS傳感器; 數據采集系統; 模/數轉換器

中圖分類號: TN98?34 文獻標識碼: A 文章編號: 1004?373X(2015)14?0129?04

0 引 言

近紅外(NIR)光譜儀是一種測量物質對近紅外輻射的吸收率或透過率的分析儀器,由于其檢測過程綠色,無損,快速等特點,已經廣泛應用于農業、食品工業、石油化工、生物化工、制藥業地質學等領域,近紅外光譜儀也因此成為近年來分析儀器的熱點研究領域之一[1]。作為近紅外光譜儀核心器件的光電傳感器的發展,對高性能光譜儀的研發起到了重要的推動作用。過去,光譜儀的光電傳感器采用CCD傳感器,但由于CCD型傳感器耗電量大、工藝復雜、成本較高、驅動程序復雜,因此,基于CCD的近紅外光譜儀的發展緩慢。隨著半導體技術的進一步發展,CMOS傳感器誕生,相對于CCD傳感器來說,CMOS圖像傳感器具有成本低、功耗低,集成度高、體積小的優點,已經逐漸替代CCD應用于各種光電檢測系統中,因此,開發基于CMOS傳感器的光譜儀,發展前景廣闊,具有較高的市場價值與實用價值[2]。

本文分析了G9214?512S圖像傳感器的工作模式 ,采用FPGA技術完成了其數據采集系統,使用VHDL語言對所設計系統進行描述,最后用Xilinx ISE Design Suit軟件自帶的ISim仿真軟件對其進行仿真和驗證,結果證明該數據采集系統的時序正確性。

1 系統簡介

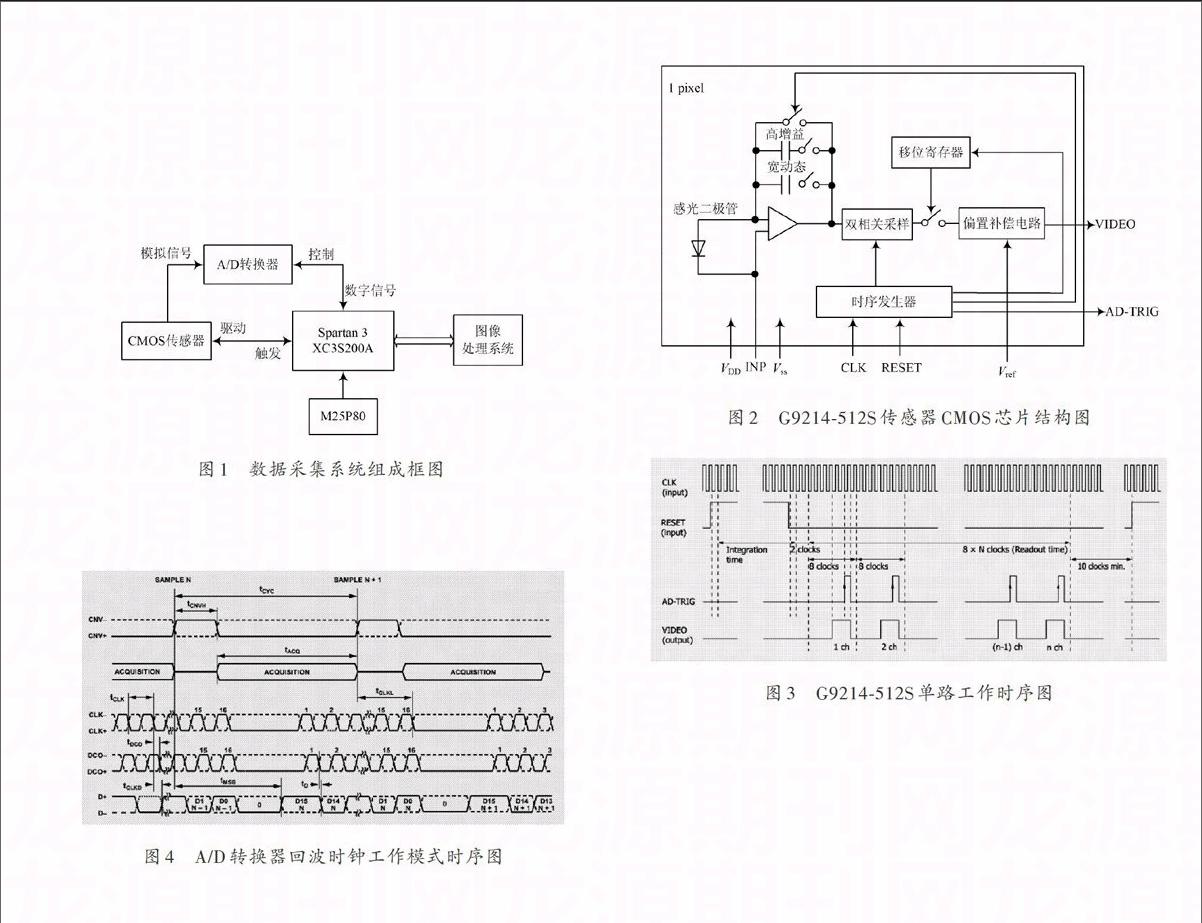

該數據采集系統由FPGA主控模塊,CMOS圖像傳感器模塊和A/D模數轉換器模塊組成,其系統框圖如圖1所示。FPGA主控模塊提供系統所需要的時序和控制指令,外存儲器M25P80存儲FPGA配置信息,FPGA內部的FIFO緩存模塊采用IP核產生,用來存儲采集到的數據,以便后續圖像處理系統進行數據處理,其數據緩存容量為10K×16 b,一次可以緩存20幀圖像信息。CMOS圖像傳感器將光信號轉換成模擬電壓信號,輸出給模/數(A/D)轉換器進行模/數轉換。A/D轉換器模塊將采集到的模擬數據轉換成16 b串行數字信號,將其存入到FPGA內部移位寄存器,然后存入FIFO緩存器,完成一次數據采集[3]。

圖1 數據采集系統組成框圖

2 G9214?512S圖像傳感器

2.1 傳感器參數

G9214?512S傳感器是濱松公司專為近紅外多通道光譜儀而設計的InGaAs線性CMOS圖像傳感器。具有動態范圍高、像元小、分辨率高、暗電流小的特點,該傳感器參數如下[4]:感光波長為0.9~1.7 μm;像元數目為512;像元尺寸為25 μm×25 μm;動態范圍為16 666;工作時鐘為0.1~4 MHz。G9214?512S傳感器像元分為具有為奇、偶2路,每路256像元,外部信號對這兩路像元的工作進行單獨控制,使其工作于同步工作模式或者異步工作模式。同步工作方式驅動方案簡單,因此本文所述數據采集系統采用同步工作方式。CMOS芯片的信號處理電路提供了2種工作方式:寬動態范圍和高增益模式,在傳感器CfSECLECT引腳加高電平實現高增益工作模式,加低電平即可實現寬動態范圍工作模式。G9214?512S傳感器CMOS芯片結構圖如圖2所示。G9214?512S片上CMOS電路集成了時序產生電路,因此其時序驅動簡單,外部提供給傳感器時鐘信號和復位信號即可,雙相關采樣電路可以有效地減小復位噪聲,移位寄存器電路可以保證信號準確有效的移出。

2.2 傳感器工作時序圖

傳感器單路工作時序圖如圖3所示。可以看出,同步工作模式下,傳感器需要2個外部輸入時序信號:時鐘信號CLK和復位信號RESET。本文所述數據采集系統采用同步積分模式:在一個復位周期中,RESET信號保持一段時間高電平,變為低電平,積分結束,等待2個時鐘CLK,傳感器將256個像元電荷信號以模擬電壓形式VIDEO輸出,VIDEO的信號周期是主時鐘CLK頻率的[18],輸出VIDEO信號的同時,傳感器輸出一個觸發外部操作信號TRIG,用于啟動外部A/D轉換器的操作,電荷輸出結束,進入等待階段[5]。

圖2 G9214?512S傳感器CMOS芯片結構圖

圖3 G9214?512S單路工作時序圖

3 模/數轉換器

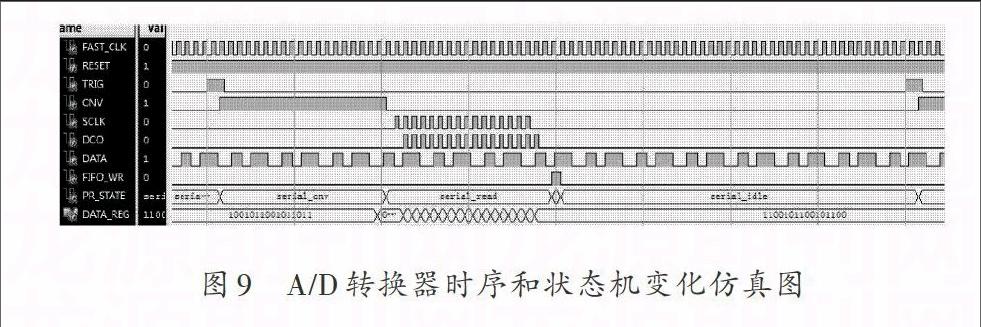

AD7961是Analog Device公司生產的16 b,5 MSPS,電荷再分配逐次逼近型(SAR)接口的模/數轉換器,具有結構緊湊、功耗低、轉換精度高和抗干擾性強的優點。AD7961具有差分輸入接口、差分輸出接口和差分控制接口,所有轉換結果通過一個LVDS自時鐘或回波時鐘串行接口傳送給FPGA[6]。本文采用回波時鐘工作模式,其工作模式時序圖如圖4所示。

圖4 A/D轉換器回波時鐘工作模式時序圖

如圖4所示,在CNV信號上升沿,ADC初始化,傳感器開始進行采樣,CNV信號高電平保持一段時間后,變為低電平后,開始有數據輸出。FPGA在CNV信號上升沿一段時間后,給A/D轉換器一個獲取數據時鐘AD_CLK,A/D轉換器給FPGA一個回波時鐘DCO,轉換后的16 b數據與DCO同步,在每個DCO上升沿,FPGA獲取轉換后的16 b數字信號。