計算機聯鎖中安全編碼編程器的設計與實現

劉培頂,陳榮武,王黎敏,陳 忱

(西南交通大學 信息科學與技術學院,成都 610031)

計算機與通信信號

計算機聯鎖中安全編碼編程器的設計與實現

劉培頂,陳榮武,王黎敏,陳 忱

(西南交通大學 信息科學與技術學院,成都 610031)

在部分計算機聯鎖系統中,輸入和輸出采用安全編碼的方式來保證采集和驅動的安全性。安全編碼需事先固化到安全輸入/輸出板的Flash存儲器中,輸入/輸出板通過讀取安全編碼的狀態來判斷系統是否正常工作。為此設計了使用C8051F020單片機作為控制器的編程器,并基于Qt設計了上位機程序來實現對輸入/輸出板上28F128J3F75 Nor Flash的操作,包括自動識別輸入/輸出板、讀/寫安全編碼等。在文中詳細介紹了系統結構、硬件連接、軟件設計以及上位機讀/寫安全編碼的數據格式定義。

計算機聯鎖;安全編碼;C8051F020;28F128J3F75;Qt

計算機聯鎖系統在保障行車安全上起著至關重要的作用,必須符合“故障—安全”原則。為確保聯鎖機與監控對象之間信息的傳送安全,在通道設計上須采用安全輸入/輸出接口,通常采用光電隔離技術、安全編碼以及表決來實現。在光耦輸入端施加特定的安全編碼信號,在另一光耦輸出端對信號進行回采,若輸出與預期不符,則表明有故障,由安全電源控制板控制安全重力繼電器切斷輸出電源,實現故障導向安全。每一路對應的安全編碼應事先固化到安全輸入/輸出板的板載Flash存儲器中,出于安全考慮,系統在啟動后只能在線讀取Flash中的編碼,而不能擦寫Flash,即不支持在線編程,這就需要一個離線編程器專門給安全輸入/輸出板進行編碼。該編程器設計的好壞,直接關乎聯鎖系統安全編碼的正確率和以后的工程配置效率。

1 芯片選型及性能介紹

為了提高計算機聯鎖系統可靠性和隨機讀取速度,安全地輸入/輸出板上的Flash存儲器采用Intel公司的28F128J3F75 Nor Flash。為了減少系統功耗并縮短開發周期,設計了一種以C8051F020高性能單片機為主控制器的編程器,并基于Qt設計了上位機程序,通過RS232串口通信來控制編程板對Flash存儲器實現讀、寫、擦除等操作。

1.1 Flash芯片28F128J3F75

根據編碼理論,利用n位二值碼元可生成2n種狀態的碼字或代碼的集合。在這2n種狀態的代碼組合中,僅有一種狀態代表危險側碼字,其余均為安全側碼字。在鐵標《TB/T 3027-2002計算機聯鎖技術條件》中規定:

(1)有相同意義的與行車安全有關的變量及其同一變量不同取值的信息編碼的漢明碼距應不小于4;

(2)與行車安全有關的信息編碼,在其碼集中合法碼字、非法碼字或安全側碼字和非安全側碼字的不對稱比率必須不小于255:1[1]。故在設計安全編碼時,碼位至少為8,從安全冗余以及方便軟件編程的角度出發,通常設計為16 bit或32 bit。經過正確的合理編碼,完全可以保證編碼的漢明距大于4[2]。

基于以上原因,聯鎖系統中,安全輸入/輸出板上的Flash存儲器一般采用16 bit I/O 口的Flash芯片。安全編碼從16 bit變為32 bit時,使用2片Flash,增加片選信號線,分時對Flash進行操作。本設計針對的安全輸入/輸出板上,Flash存儲器為28F128J3F75 Nor Flash芯片,芯片采用分塊結構,非常適合于要求高密度的代碼或者數據存儲的低功耗系統。它具有以下特點:

(1)速度快:異步頁模式讀取25 ns/8 word;在256 byte緩沖器寫模式下有效編程時間為1.41 us。

(2)低功耗:其供電電壓為2.7 V~3.6 V,根據手冊擦寫功耗最大為80 mA×3.3 V。

(3)具有通用Flash接口,用戶可根據需要配置為x8或者x16模式;具有128個128 kbyte/64 kWord的可擦除塊,該特性允許用戶對其中任意一個塊數據進行擦除或者編程。

(4)可靠性高:工作溫度為–40℃~+85℃;Vpp=GND時可實現完全寫保護,具有靈活的塊上鎖,電壓跳變時可中止擦除/寫入操作;每塊循環擦寫次數為10萬次以上。

1.2 編程器主控制器C8051F020

編程板設計時采用5 V的USB接口供電,考慮到一般計算機USB口供電能力為300 mA左右,所以元器件選擇以及設計時需要考慮降低功耗。安全輸入/輸出板編程時主要功耗為FLASH,根據28F128J3F75數據手冊,3.3 V供電電壓下,其擦寫功耗最大為80 mA。其它板載電路如CPCI和邏輯控制電路等都處于待機狀態,功耗可以估計為10 mA左右,即在編程時安全輸入/輸出板最大電流為90 mA,功耗約為300 mW,在設計編程板上電路時總功耗盡量保持在1.2 W以內。考慮到以上原因,同時為了方便系統開發,在設計時采用C8051F020芯片作為編程器主控制器。

C8051F020是完全集成的混合信號系統級芯片(SoC),具有功能全面、應用廣泛、性價比高等優點。它具有與8051兼容的CIP-51微控制器內核,指令系統完全相同,熟悉MCS-51系列單片機的工程技術人員可以很容易地掌握C8051F[3]。與Flash安全編碼相關的特性如下:

(1)采用流水線結構,與標準的8051結構相比指令執行速度提高了大約10倍;最大系統時鐘頻率為25 MHz,峰值速度達到25 MIPS。

(2)擁有8個8 bit的I/O端口,大量地減少了外部連線和器件擴展,有利于提高可靠性和抗干擾能力。

(3)工作電壓為2.7 V ~3.6 V,與Flash工作電壓兼容;支持多種節點休眠和停機方式,每個端口I/O引腳都可以被配置為推挽或漏極開路輸出,在標準8051中固定的“弱上拉”可以被總體禁止,這為低功耗應用提供了進一步節電的能力。

(4)自帶4 K XRAM,讀/寫Flash時可提供足夠大的數據緩沖區。

(5)支持JTAG調試和邊界掃描,可以進行非侵入式、全速的在系統調試[4]。

2 系統結構及硬件接口設計

近年來新開發的計算機聯鎖硬件平臺均采用CPCI總線,因此設計編程板時要加入CPCI接口。編程板由5 V USB供電,通過CPCI接口與安全輸入/輸出板的J2口相連,上位機通過RS232接口與編程板進行串口通信,發送讀、寫、擦除等命令,控制編程板上的主控制器C8051F020單片機對安全輸入/輸出板上的Flash芯片執行相應的操作。JTAG接口用于燒寫程序至單片機,并提供在線調試。在編程板上設計有狀態燈,用于顯示電源和工作狀態。系統結構如圖1所示。

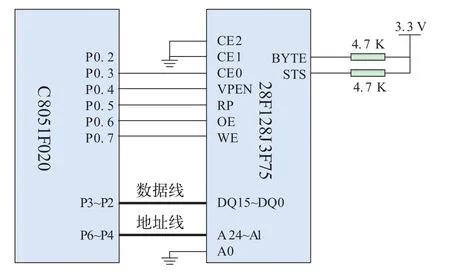

C8051F020有8個8 bit的I/O端口,低端口(P0、P1、P2 和 P3)既可以按位尋址也可以按字節尋址,除作通用I/O口外,可作為其他功能模塊的輸入輸出引腳,通過交叉開關配置器選擇并控制。高端口(P4、P5、P6和 P7)只能按字節尋址[4]。根據交叉開關譯碼表,P0.0和P0.1腳分別作為串口通信的TX0和RX0,并且位置不能互換。在硬件電路設計時,為充分利用單片機I/O口,P0.2~P0.7作為Flash芯片的控制線,控制片選信號(P0.2、P0.3分別控制兩塊Flash芯片的CE0片選信號,實現32 bit編碼)、寫保護、復位信號、讀使能、寫使能,P1預留,P3、P2作為數據線,與 Flash的DQ15~DQ0相連,P6、P5、P4作為地址線,與Flash的A24~A1相連,P7接狀態燈。由于采用16 bit數據位,因此Flash芯片上的BYTE接VCC,硬件置1,A0接地。在此,給出C8051F020與28F128J3F75相關部分連接圖,如圖2所示。

圖1 安全編碼編程器的系統結構

圖2 C8051F020與28F128J3F75硬件接口電路

3 軟件設計

軟件設計時,為了程序的可移植性和易用性,將程序分為3個層次。第1層是硬件抽象層,第2層是實現訪問Flash的命令層,第3層是應用層,提供給用戶或文件系統的接口函數。

3.1 硬件抽象層

硬件抽象層包括訪問Flash的硬件環境配置以及單片機與Flash接口實現通訊的基本函數。硬件環境配置包括C8051F020系統時鐘初始化、I/O端口配置、串口初始化、Flash芯片初始化。與Flash接口實現通信的基本函數即為Flash的讀/寫函數:從給定的24 bit地址,讀取一個字的數據,或往該地址寫一個字的數據或命令。對Flash芯片的所有操作均基于這兩個函數。C8051F020是8 bit的系統,而讀/寫Flash時數據線為16 bit,地址線為24 bit。為了提高程序運行效率,避免地址操作時的溢出和進位判斷,定義了一個unsigned long型變量F_Addr表示地址(C8015中為32 bit),設置宏定義,通過指針和取地址的方式,取其低24 bit分成3個8 bit分別賦值給C8051F020的P6~P4口,如下所示:

#define h_long(x) (*((unsigned char *)&x+1)) #define m_long(x) (*((unsigned char *)&x+2)) #define l_long(x) (*((unsigned char *)&x+3))經測試,使用該方式讀取Flash數據的效率高于定義全局變量或使用移位操作符賦值的方式。通過研究28F128J3F75芯片數據手冊中的單字異步讀時序圖和異步寫時序圖,使用_nop_()指令延時及控制讀/寫信號、片選信號電平高低來模擬Flash的讀/寫時序,即可封裝成最基本的讀/寫函數void Flash_WR(unsigned long F_Addr, unsigned int Data_h, unsigned int Data_l)、int Flash_RD (unsigned long F_ Addr)供命令層函數使用。其中,Data_h、Data_l分別表示數據的高8 bit和低8 bit賦給單片機的P3口和P2口。

3.2 命令層

調用硬件抽象層的基本讀/寫函數生成Flash的命令函數,包括讀取狀態寄存器狀態、清除狀態寄存器狀態、CFI查詢、讀Flash芯片ID號和設備號、按塊擦除、按字寫、緩沖器寫、讀陣列等。在Flash芯片數據手冊中,每一個命令操作均有詳細的流程圖供開發者參考使用。

3.3 應用層

提供用戶程序訪問Flash的高級接口函數,包括寫安全編碼、讀安全編碼、自動識別安全輸入/輸出板、擦除整塊Flash芯片等函數。用戶不需要知道Flash的內部結構和接口協議,單片機所有初始化完畢后即進入while(1)循環,等待用戶程序發來的命令,進而執行相應的操作。

4 上位機及數據格式定義

在工程應用中,安全編碼一般以十六進制存放于.dat文件中,為了方便讀/寫安全編碼,基于Qt軟件設計了上位機程序,其界面如圖3所示。除具有串口助手的基本功能外,增加了許多安全編碼編程器相關的功能,包括加載.dat文件、讀Flash信息、擦除Flash芯片、燒寫安全編碼數據、讀安全編碼數據、數據管理等。

圖3 編程器上位機程序界面

上位機與編程器之間使用RS232串口通信,C8051F020單片機使用UART0的方式一,即異步工作,8 bit數據位,一個起始位,一個停止位。

安全編碼使用大端存儲方式,即數據的低字節存放在內存的高地址,數據的高字節存放在內存的低地址。讀/寫安全編碼時均按此種方式。

讀/寫安全編碼時,以1 kbyte數據為單位進行讀/寫,為保障安全性,數據格式定義如表1所示。

表1 讀/寫安全編碼數據格式

Flash芯片基地址定義為0x000000,上位機寫數據時,編程板根據編號值來確定安全編碼數據的存儲位置;上位機讀數據時,編程板根據地址計算編號值。安全編碼為16 bit時,F_addr=512 N,安全編碼為32 bit時,F_addr=256 N。校驗值采用最簡單實用的方式,即將編號N與安全編碼數據共1 002 byte的數據累加。上位機與編程板均需要計算校驗值,將收到的校驗值與計算的校驗值進行比較,若相等則表明收到的數據是正確的,執行相應的讀/寫操作;若不相等,則顯示警告信息,并在編程板上以流水燈的形式表現,提示用戶數據有誤,中斷讀/寫操作。

5 結束語

在輸入/輸出采用安全編碼的聯鎖系統中,安全編碼編程器的設計必須要有非常高的安全性和可靠性。通過認真分析功能需求及電氣技術要求,設計了以C8051F020為主控制器的編程器及上位機程序。編程器設計緊湊,輕便小巧,使用一臺筆記本即可進行測試與調試。在115 200波特率下,安全編碼讀、寫速度分別為7 kbyte/s、3 kbyte/s,完全滿足工程應用需求。目前整套系統已應用于國內某自主研發的計算機聯鎖系統硬件平臺中。

[1]中華人民共和國鐵道部. TB/T 3027-2002.計算機聯鎖技術條件 [S].北京:中國鐵道出版社,2002.

[2]陳學侄, 陳洪亮.數據庫原理與工程應用[M].合肥:中國科學技術大學出版社,1996.

[3]孫立香,趙不賄,劉星橋. C8051F020與80C51單片機的異同點[J]. 國外電子元器件,2007(5):31-35.

[4]潘琢金,施國君. C8051Fxxx高速SoC單片機原理及應用[M].北京:北京航空航天大學出版社,2002.

[5]李長有,武學東,孫步勝,馬齊爽. 基于C8051F020的SD卡主控制器設計[J]. 微計算機信息,2007(26):120-122.

責任編輯 徐侃春

Secure coding programmer for Computer-based Interlocking System

LIU Peiding, CHEN Rongwu, WANG Limin, CHEN Chen

( School of Information Science and Technology, Southwest Jiaotong University, Chengdu 610031, China )

In some kinds of Computer-based Interlocking System, secure coding was used for input and output to guarantee the safety of acquisition and driving. Secure coding should be programmed into the safety input/output board’s Flash memory previously. According to the state of security coding, the input/output board determined whether the system worked properly. The paper designed a programmer which used 80C51F020 single-chip microcomputer as its controller, and also designed the PC program based on Qt to implement the operation of 28F128J3F75 Nor Flash chip, including input / output board of automatic identif i cation, read / write secure coding, etc. It was described the system architecture, hardware connections, software design and the data format def i nition of PC program reading or writing secure coding in detail.

computer-based interlocking; secure coding; C8051F020; 28F128J3F75; Qt

U284.3∶TP39

A

1005-8451(2015)10-0047-04

2015-01-24

劉培頂,在讀碩士研究生;陳榮武,高級工程師。