基于FPGA的TFT液晶顯示時序控制器設計

陳建軍,金強寧*,章鵬,劉凱麗

基于FPGA的TFT液晶顯示時序控制器設計

陳建軍1,2,金強寧1,2*,章鵬1,2,劉凱麗1,2

(1.國家平板顯示工程技術研究中心,江蘇南京210016; 2.中國電子科技集團公司第五十五研究所,江蘇南京210016)

針對某些僅綁定柵源驅動芯片而沒有時序控制電路的液晶顯示面板,設計了一款基于FPGA的SOPC嵌入式系統的時序控制器。它利用FPGA的邏輯電路實現LVDS視頻信號的解碼、灰階擴展、RSDS信號編碼、顯示控制時序轉換等功能,并通過FPGA中Nios II軟核的串行口設置參數,編程GAMMA及VCOM電壓,參數具有掉電保護功能。時序控制器中還增加了BIT檢測電路,可實時査詢電路運行狀態。該時序控制器電路集成度高、功耗低,結構簡單,適合特殊應用,具有較高使用價值。

TFT液晶顯示;時序控制器;FPGA;SOPC;BIT

1 引言

在當今信息社會,彩色TFT(Thin Film Transistor)液晶顯示器已經廣泛地應用在我們生活的各個方面,液晶顯示面板的制造技術不斷完善成熟,已形成標準化、規范化的電氣接口形式,如低電壓差分信號LVDS(Low Voltage Differential Signaling)、bit位數字RGB信號等。近來,隨著液晶顯示面板集成度越來越高,柵源驅動芯片Source driver與Gate driver均綁定在玻璃面板上,導致與面板的電氣接口發生根本性改變。時序控制器(Timing controller)作為液晶顯示器的核心部分之一,對液晶顯示系統的正常工作起著關鍵的作用,它為液晶顯示器前級電路與液晶面板之間提供橋接,接收并處理前級電路輸出的標準數字視頻信號,產生特定的時序信號控制液晶面板正常工作。目前,國內、外各液晶面板廠商設計的時序控制電路通常采用商用專用控制芯片,這樣時序控制電路只適合專一的液晶面板使用。本設計采用工業級FPGA(Field Programmable Gate Array)來實現商用控制芯片的所有功能,同時集成了狀態BIT (Built In Test)檢測及參數可編程設置等功能,能滿足特殊應用場合苛刻環境下的可靠性要求。而且,硬件電路的通用化設計可以適應不同廠商、不同規格的液晶面板。

2 液晶顯示面板

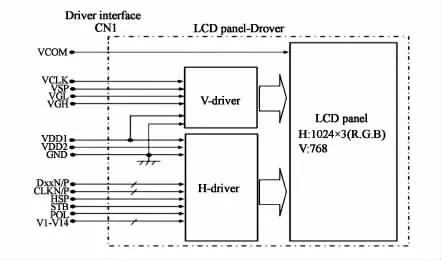

圖1為一款典型的僅綁定柵源驅動芯片而沒有時序控制電路的彩色液晶顯示面板結構,本文針對該款顯示面板展開時序控制電路設計[1]。

圖1 液晶顯示面板的結構框圖Fig.1Block diagram of LCD panel

液晶顯示面板基本參數:

分辨率:1 024(H)×768(V)

顯示顏色:RGB

顯示灰階:每色64級,262144級色階

電氣接口:

·數據、掃描及控制通道:RSDS(Reduced Swing Differential Signaling)低擺幅差分信號,掃描時鐘、水平垂直掃描起始脈沖、水平垂直方向控制、差分信號極性控制、數字鎖存脈沖等;

·芯片支持電壓;

·VCOM電壓和GAMMA電壓(Vγ1~Vγ14)。

3 時序控制電路設計

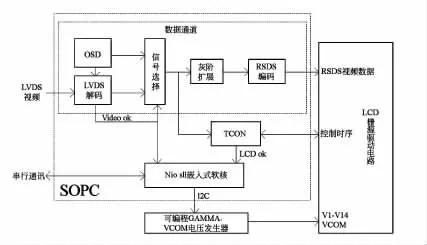

圖2為時序控制電路結構框圖。

圖2 時序控制電路結構方框圖Fig.2Block diagram of timing controller circuit

時序控制電路[2-4]采用基于Altera公司FPGA的SOPC(System On Programmable Chip)技術來實現[5-6],它由數據處理通道、顯示控制時序變換、驅動電壓發生器及嵌入式NiosII軟核[7]等部分組成。

3.1數據處理通道

數據處理通道在FPGA內實現,它由LVDS解碼電路、灰階擴展及RSDS輸出接口電路等部分構成。

3.1.1LVDS解碼電路

LVDS接口是為了解決TTL電平方式傳輸寬帶高碼率數據時功耗大、電磁輻射大等缺點,由美國國家半導體公司研制的一種數字視頻傳輸方式,在液晶面板上得到了廣泛的應用。本文所設計的時序控制器接收單路四通道8 bit LVDS視頻信號,同時兼容VESA LVDS信號格式和JEIDA LVDS信號格式。

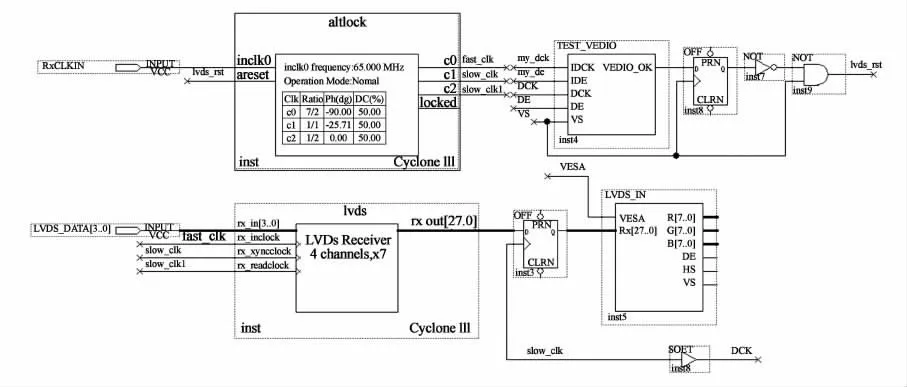

圖3 LVDS解碼電路Fig.3Decoding logic for lvds

LVDS解碼電路如圖3所示。

外部65 MHz的LVDS時鐘RxCLKIN接入鎖相環(PLL)IP核,根據LVDS時鐘與數據的相位關系,產生3個時鐘:

fast_ck:頻率為227.5 MHz,相位為-90°。

slow_ck:頻率為65 MHz,相位為-25.71°。

slow_ck1:頻率為32.5 MHz,相位的為0°。

四通道LVDS視頻數據接入LVDS解串行化器(LVDS SERDES),設置數據通道為4,SERDES因子為7,選擇外部鎖相環。分別將PLL產生的fast_ck接至解串行化器的rx_inclock,slow-ck接至解串行化器的rx_syncclock,slow_ck1接至解串行化器的rx_readclock。解串行化器輸出28位含有視頻數據和時序信號的并行數據,slow_ck作為輸出的點時鐘DCK。

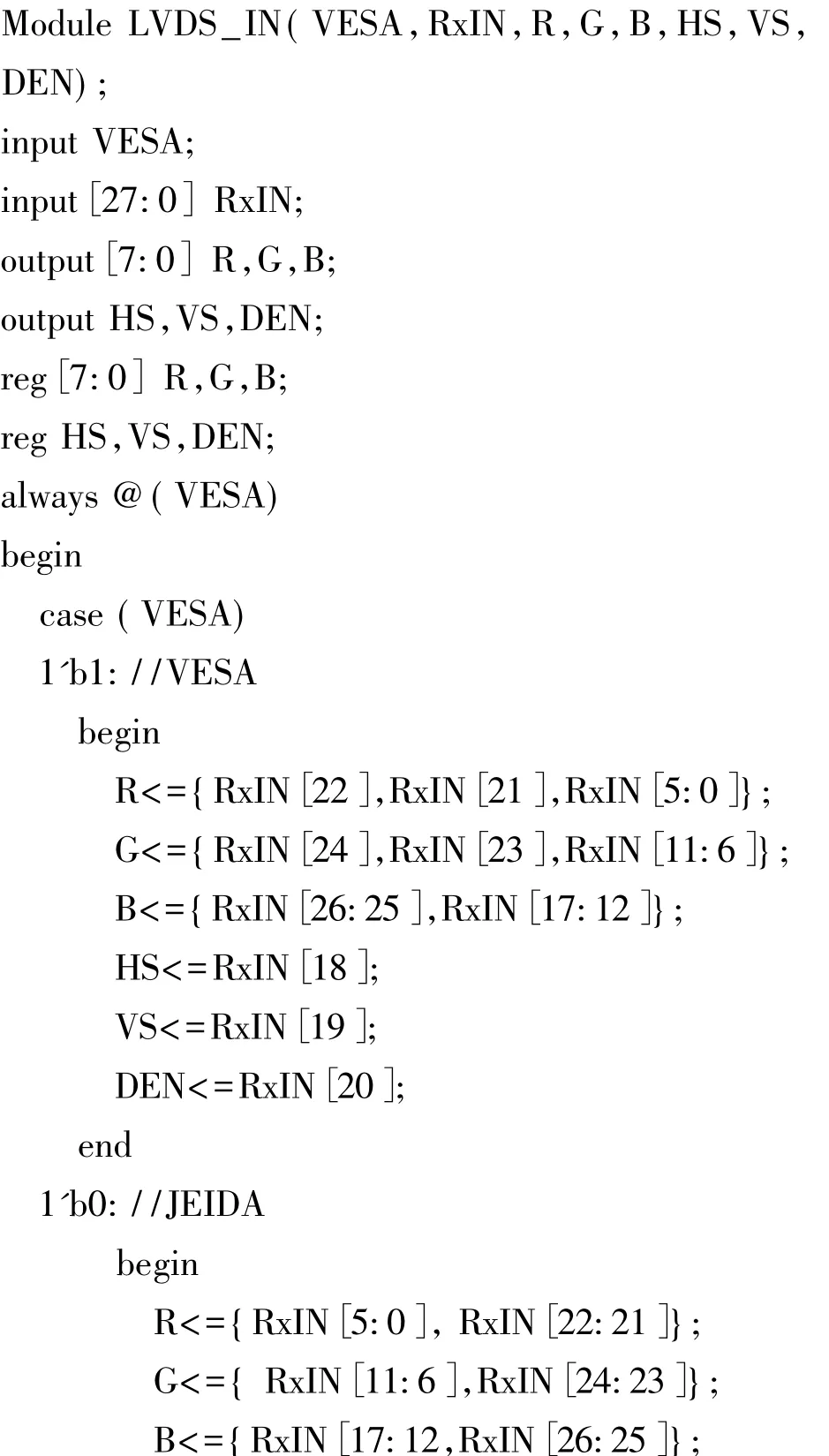

目前有兩種流行的LVDS編碼格式,一種是VESA標準[8],另一種為JEIDA標準[9],兩種編碼的Data Mapping不同。LVDS_IN模塊根據外部輸入信號格式標準,從28位并行數據中譯碼出紅,綠,藍視頻數據和時序信號HS,VS,DE。為了使時序控制器可以兼容6 bit8 bit VESA及8 bit JEIDA三種視頻輸入格式,在LVDS_IN模塊的設計中,當VESA腳電平為高時,采用8 bit VESA編碼,VESA腳為低電平時采用6 bit VESA或8 bit JEIDA編碼,6 bit VESA與8 bit JEIDA編碼是兼容的,當外部輸入的第四對LVDS差分數據線使用時是8 bit視頻數據,否則是6 bit數據。

LVDS_IN模塊用硬件描述語言Verilog編寫,程序清單如下:

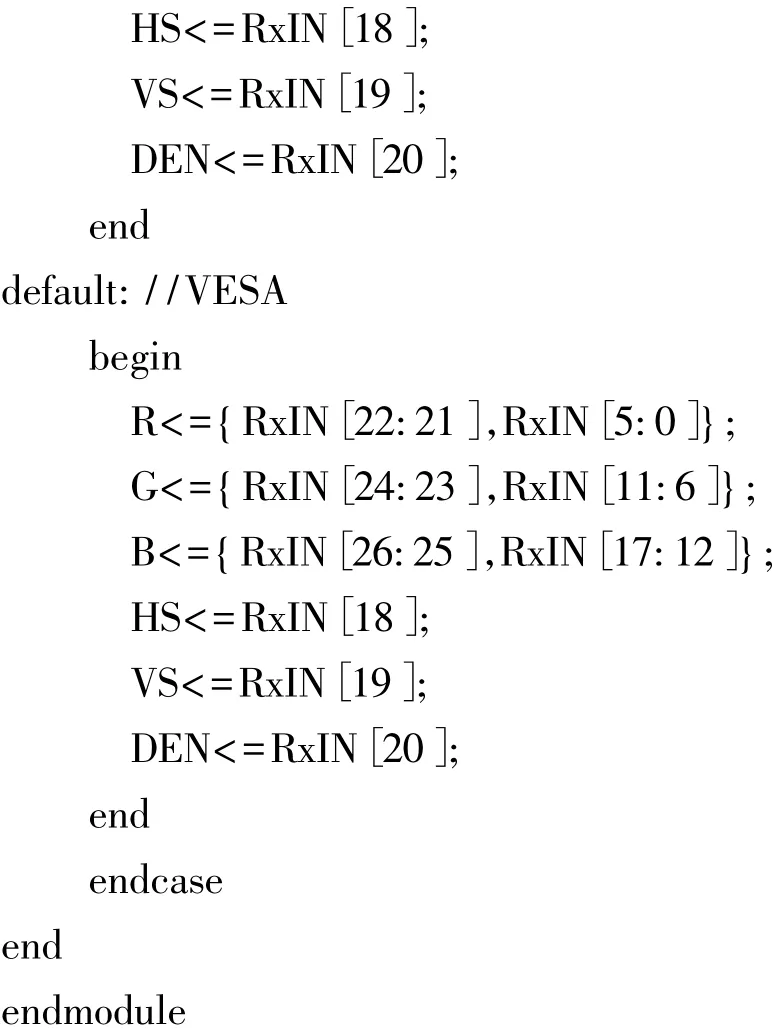

3.1.2灰階擴展

時序控制器的外部接口為RGB各8 bit視頻數據,而顯示屏的源驅動器為6 bit,我們采用了PD+FRC算法來實現顯示器的灰階擴展[10-13],使顯示屏具有253×253×253種顏色體現能力。

PD(Pixel Dithering)技術是指用交替的點圖案去模擬在顯示器中不能使用的顏色的過程。采用不同的真實灰階實現亮度融合,產生感應灰階。

FRC(Frame Race Control)是為了消除靜態抖動算法引起的條紋效應,更好地還原圖像質量,使顯示的圖像平滑柔和,利用人眼視覺惰性而實現的動態抖動算法。算法示意圖如圖4所示。

圖42 bit Bayer動態抖動矩陣Fig.42 bit Bayer dynamic dithering matix

由圖4可以看出,動態抖動算法為了消除固定抖動模板引起的條紋效應,采用隔幀變換抖動模板的方法,在時域上,由于抖動矩陣的循環變換而導致不同幀在抖動后的圖案中同一位置處的像素明暗輪換出現,但圖像的灰度保持不變,條紋效應被平均。

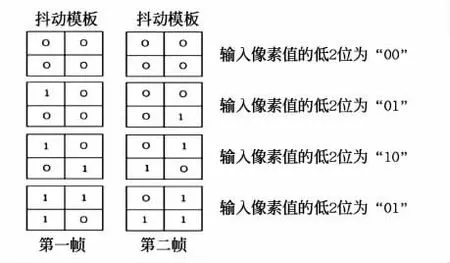

根據上述算法,在FPGA內用圖形輸入法實現的電路如圖5所示。

圖5 用FPGA實現FRC+PD算法的電路圖Fig.5Logic in FPGA for implementing FRC+PD algorithm

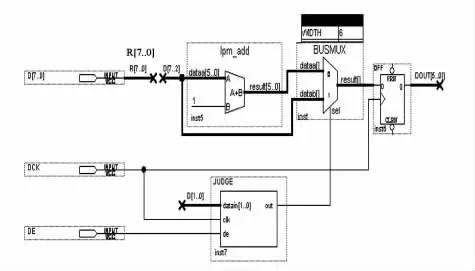

3.2RSDS編碼

時序控制器采用RSDS接口驅動液晶面板的源極驅動器。RSDS接口有諸多優點,包括低功耗、低壓差分擺幅以及低電磁輻射等。RSDS按串行模式傳送數據,信號觸發是雙沿的,數據應進行倍速編碼。根據面板的接口要求,每種基色的6 bit數據編碼成三對RSDS差分對,全彩色視頻數據編碼成9對差分數據信號及一對時鐘信號。數據倍速編碼電路如圖6所示。

圖6 數據倍速編碼電路Fig.6Double data rate logic for image data

電路中采用了Altera的雙數據速率I/O IP核Altddio_out。Altddio_out核是參數可配制的,并針對Altera FPGA結構進行了優化,在參考時鐘的上升沿和下降沿發送數據。

差分輸出時鐘與參考時鐘理論上相差90°,在實際電路中用鎖相環調整輸出時鐘的相位,抵消內部電路和布線延時,使輸出時鐘在數據跳變的中心位置,確保接收電路的時序裕度。

3.3顯示時序轉換

時序控制器的顯示時序轉換電路將外部輸入的符合VESA標準的視頻信號轉化為顯示屏工作所需的時序信號。為了提高時序控制器的通用性,采用DE Only控制方式,即僅使用外部視頻信號的DE和DCLK兩個時序信號來產生顯示屏柵源驅動器等所需的所有控制信號。

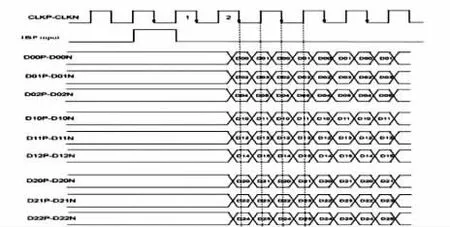

源驅動器主要信號的時序關系如圖7所示。

圖7 源驅動器主要信號的時序關系Fig.7Timing sequence of source-driver’s signals

與源驅動器相關的信號有:

(1)HSP1/2:源驅動器的啟動脈沖輸出或輸入。

(2)CLKN,CLKP:RSDS標準的移位時鐘。

(3)DXXP,DXXN:RSDS標準的視頻數據。

(4)STB:數據鎖存脈沖。

(5)POL:極性控制信號。

(6)R/L:左右移位方向控制。

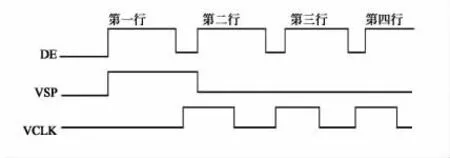

柵極驅動器主要信號的時序關系如圖8所示。

圖8 柵極驅動器主要信號的時序關系Fig.8Timing sequence of Gate-driver’s signals

與柵極驅動器相關的信號有:

(1)VSP1/2:柵驅動器的啟動脈沖輸出或輸入。

(2)VCLK:柵驅動器的時鐘。

(3)U/D:上下移位方向控制。

3.4驅動電壓產生電路

時序控制器外部供電為直流+3.3 V,通過DC/DC變換,產生FPGA工作所需的+2.5 V、+1.2 V以及液晶面板工作所需的VDD1(+3.3 V),VDD2(+10 V),VGH(+20 V),VGL(-8 V)。GAMMA電壓有14路,分別是Vγ1~Vγ14,1路公共電極電壓VCOM,采用TI公司的BUF16821來實現[14]。BUF16821是可編程的GAMMA電壓發生器和VCOM校準器,它能提供16條可編程GAMMA電壓通道,以及2路可編程VCOM電壓通道。所有GAMMA和VCOM通道提供一個軌到軌輸出,此輸出在10 mA負載時,通常在任一電源軌的150 mV內擺動,具有較高的精度。NiosII軟核通過一個I2C接口對所有通道進行編程,最終的GAMMA和VCOM設定值可被存儲在時序控制器上非易失性存儲器中。

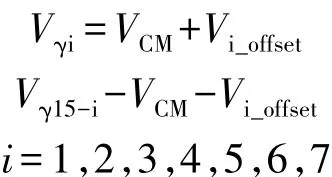

3.4.1GAMMA電壓的設置

GAMMA電壓Vγ1~Vγ7與Vγ8~Vγ14以中點電壓VCM為中心在高低電壓區對稱分布,VCM固定設置為VDD2的一半。NiosII軟核程序中以7個偏移量V1_offset~V7_offset為變量來調整14組GAMMA電壓。

GAMMA電壓值設定公式為:

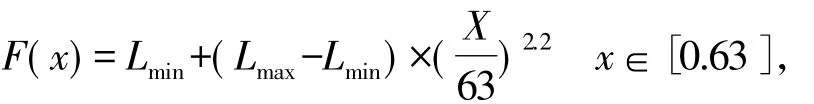

通過對7組對稱的GAMMA電壓的設定,使LCD面板滿足GAMMA=2.2的要求。

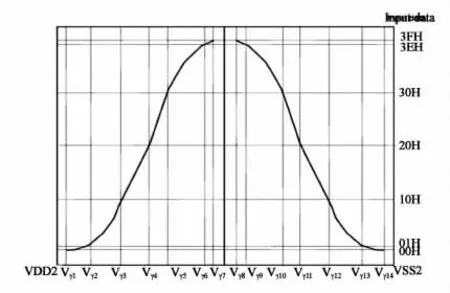

如圖9所示GAMMA電壓與視頻數據關系: Vγ1,Vγ14對應灰階00H,Vγ2,Vγ13對應灰階01H,Vγ3,Vγ12對應灰階10H,Vγ4,Vγ11對應灰階20H,Vγ5,Vγ10對應灰階30H,Vγ6,Vγ9對應灰階3EH,Vγ7,Vγ8對應灰階3FH。

GAMMA為2.2時亮度與灰階的關系為:

其中x為灰階值,F(x)為其所對應的亮度,Lmax最高亮度值,Lmin最低亮度值。

我們先將信號源的灰階設為最高(3FH),通過調整V7_offset變量值使LCD面板達到最高亮度Lmax,再將信號源的灰階設為最低(00H),通過調整V1_offset使LCD面板達到最低亮度Lmin。確定Lmax和Lmin后便可以調整其他GAMMA電壓的偏移量,使各灰階亮度滿足公式的要求,從而使LCD面板的GAMMA特征為2.2。

圖9 GAMMA電壓與視頻數據關系[1]Fig.9Relationship between GAMMA voltages and image data

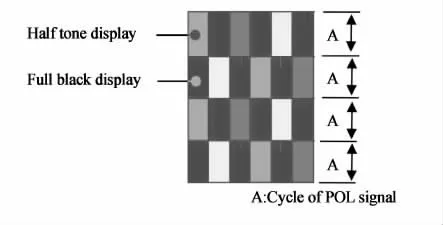

3.4.2VCOM電壓的設置

從理論上看,VCOM應設定在GAMMA電壓的對稱中心,即VCOM應等于中點電壓VCM,然而實際上LCD面板內的TFT寄生電容,會產生電壓耦合效應,使像素電壓在TFT關閉時,受到柵極電壓變化的影響,而偏離由數據線所寫入的電壓。為了補償這個電壓變化,VCOM必須調整到低于中點電壓的某一值。

根據面板驅動的反轉模式,采用如圖10所示的按亞像素反轉的測試畫面作為顯示信號源,PC機通過串行口發送指令和參數給NiosII軟核,通過一個I2C接口調整VCOM值,用專用儀器測量其“flicker”值,當畫面的“flicker”值最小時VCOM值為最佳值。

GAMMA電壓和VCOM電壓的設置參數值被存入可掉電保存的存儲器中。在上電復位后被讀出來設定GAMMA電壓和VCOM電壓。

圖10 “flicker”測試畫面Fig.10Image for flicker testing

4 BIT檢測電路設計

為了提高時序控制器的可檢測性,設計了若干嵌入式檢測電路。檢測狀態可通過NiosII軟核經由串行通訊口送出。

4.1外部視頻信號有效性檢測

為了提高LVDS解碼電路的可靠性,在圖3所示電路的TEST_VIDEO模塊中設計了外部視頻檢測電路,通過檢測外部輸入的DCLK和DE信號的頻率來判斷外部視頻信號有效性。當外部視頻中的DCLK和DE的頻率特征符合VESA標準時序時,便判定為有效視頻,不符合則判外部視頻失效,并置標志位,供軟核讀取,此時將內部產生的藍底“無信號”白字視頻的警示信息切換至視頻數據處理電路,通過時序控制電路在TFT液晶面板上顯示,并同時定時復位鎖相環,以保證定時判斷DCLK和DE信號的頻率,當滿足標準時,TFT液晶面板恢復顯示外視頻。

實際應用中在極端低溫環境下,PLL常失鎖且不能恢復,造成顯示器顯示失效,該電路的應用保證了顯示屏的可靠性。

4.2驅動電路工作狀態檢測

在液晶面板的柵源驅動電路中都有一組雙向移位寄存器,寄存器的位數與所控制的行列驅動線數一致,柵驅動電路中有768個寄存器,源驅動電路中有1 024×3個寄存器。移位寄存器的數據端接行列啟動脈沖,雙向移位寄存器的移位方向分別決定了顯示屏的左右倒向和上下倒向顯示。驅動電路按照特定的時序運行,柵驅動電路的啟動脈沖頻率與場頻一致,移位時鐘為行同步脈沖,移位寄存器周而復始地逐條開啟/關閉掃描線,在逐行掃描768行后,移位寄存器末端輸出被送入到時序控制電路。源驅動電路的啟動脈沖頻率與行頻一致,移位時鐘為數據時鐘,移位寄存器重復逐條開啟/關閉數據鎖存器,使數據鎖存器順次接收顯示數據,在逐點掃描1 024點后,移位寄存器末端輸出被送入到時序控制器。

從上分析可知,柵源驅動電路在正常工作時都會輸出一個與行列啟動脈沖頻率一致,相位相異的信號到時序控制器,通過檢測此信號的有無便能知悉面板驅動電路是否正常工作。

5 設計結果

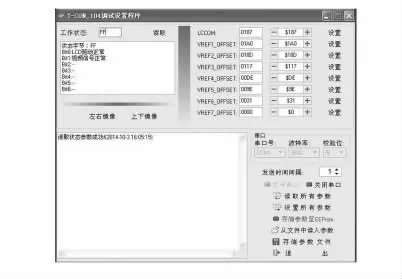

我們所設計的時序控制器連接LCD面板的產品實物圖如圖11所示,PC機上運行的調試軟件界面如圖12所示。

圖11 TCON產品實物圖Fig.11Performance of the TCON board

圖12 調試軟件界面圖Fig.12Interface of debug software

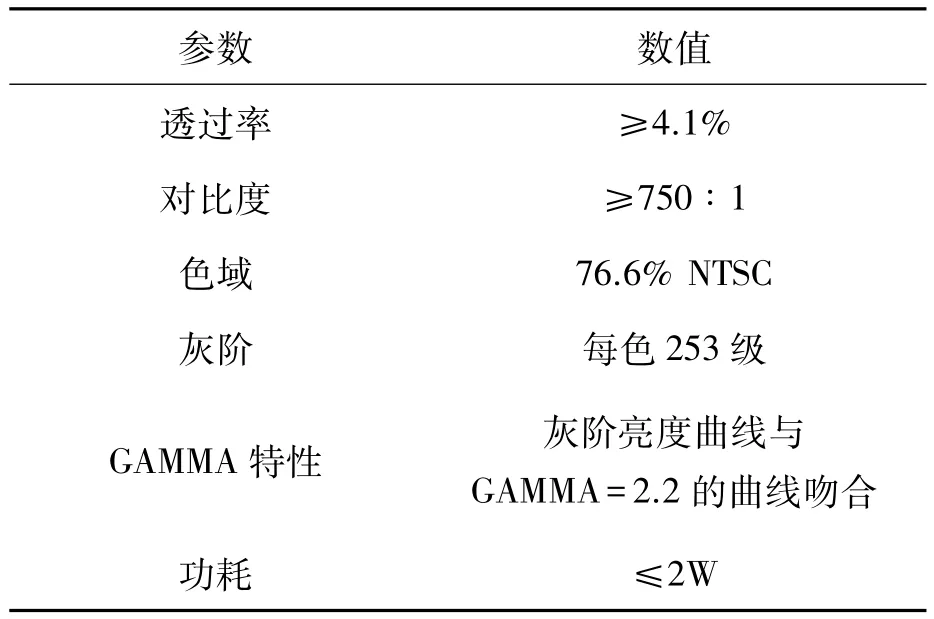

使用本文所述的時序控制器后,液晶顯示面板的主要光電性能指標如表1。

表1 主要光電參數Tab.1Major optical parameters

6 結論

使用該時序控制器,液晶顯示面板的灰階體現正確,畫質穩定,功耗比常規產品要低。

時序控制器所具有的嵌入式檢測功能,提高了產品的可檢測性;采用數字編程的GAMMA及VCOM電壓,數據位達10 bit,調整精度高,穩定性可以得到充分保證。

時序控制器還可由跳線設定轉入顯示其自產生的老練畫面,簡化了產品老練工序。

時序控制器所有元器件、原材料均按工業級標準嚴格選用、篩選,設計上充分考慮參數的冗余度,核心芯片采用了工業級FPGA作為主控芯片進行設計,提高了可靠性,經實驗驗證,產品可以在-55~+75℃的溫度范圍內穩定工作,具有良好的環境適應性。

該時序控制器已廣泛應用在輪船、車輛、飛行器使用的各種液晶顯示設備中,其集成度高、功耗低,結構簡單等特點,獲得了較高的使用價值。

[1]NLT Technologies,Ltd.NL10276HC20-39 Preliminary Data Sheet[CD].USA:NEC,2012.

[2]金強寧,洪乙又,李慧芝,等.基于mini-LVDS技術的TFT-LCD彩色液晶顯示屏的驅動研究及應用[J].光電子技術,2009,29(3):196-200.

Jin Q N,Hong Y Y,Li H Z,et al.The application and study of Color TFT-LCD panel driver based on mini-LVDS technology[J].Optoelectronic Technology,2009,29(3):196-200.(in Chinese)

[3]劉杰,程松華,張永棟,等.基于Mini-LVDS技術的TFT-LCD時序控制器的設計[J].液晶與顯示,2014,29(2): 238-244.

Liu J,Cheng S H,Zhang Y D,et al.Design of TFT-LCD timing controller based on mini-LVDS technology[J].ChineseJournal of Liquid Crystals and Displays,2014,29(2):238-244.(in Chinese)

[4]戴亞翔.TFT LCD面板的驅動與設計[M].北京:清華大學出版社,2008:42.

Dai Yaxiang.Design and Operation of TFT LCD Panel[M].Beijing:Tsinghua University Press,2008:42.(in Chinese)

[5]楊軍,張偉平,趙嘎,等.面向SOPC的FPGA設計與應用[M].北京:科學出版社,2012.

Yang J,Zhang W P,Zhao G,et al.FPGA Design and Application for the SOPC[M].Beijing:Science Press,2012.(in Chinese)

[6]宋躍,盧俊平,雷瑞庭,等.基于Nios II的液晶屏控制器SOPC設計[J].液晶與顯示,2014,29(1):48-54.

Song Y,LU J P,Lei R T,et al.SOPC design on LCD controller based on Nios II[J].Chinese Journal of Liquid Crystals and Displays,2014,29(1):48-54.(in Chinese)

[7]劉東華.Altera系列FPGA芯片IP核詳解[M].北京:電子工業出版社,2014:344-365.

Liu D H.Altera IP core series FPGA Chip Comments[M].Beijing:Electronic Industry Press,2014:344-365.(in Chinese)

[8]VESA.TV Panels Standard[S].USA:VESA,2006.

[9]JEIDA.JEIDA-59-1999 Digital Interface Standards for Monitor[S].Japan:JEIDA,1999.

[10]陳建軍,周旭,張小蕓.感應灰階的產生技術及其在液晶顯示器上的應用[J].光電子技術,2013,33(2):113-114.

Chen J J,Zhou X,Zhang X Y.An algorithm of spatial grey-scale and application for liquid crystal display[J].Optoelectronic Technology,2013,33(2):113-114.(in Chinese)

[11]Limb J O.Design of dither waveforms for quantized visual signals[J].Bell System Technical Journal,1969,48: 2555-2582.

[12]Floyd R W,Inberg L S.An Adaptive Algorithm for spatial grey scale[C].Proceedings of the SID,Los Angeles,1976,17 (2):75-77.

[13]Robin S H.Process for producing shaded colored images using dithering techniques:USA,5757347[P].1998-05-26.

[14]Texas Instrument Incorperated.Programmable Gamma_voltage generor and Vcom calibrator with integrated two-bank memory[CD].USA:TI,2011.

FPGA-based TFT LCD timing controller design

CHEN Jian-jun1,2,JIN Qiang-ning1,2*,ZHANG Peng1,2,LIU Kai-li1,2

(1.National Engineering Research Center for FPDs,Nanjing 210016,China; 2.The 55thResearch Institute of China Electronics Technology Group Corporation,Nanjing 210016,China)

A FPGA-based SOPC embedded system timing controller is designed for some LCD panel driver chips which only bonding with source and gate circuits.It uses FPGA logic circuits to implement the functions such as LVDS video signal decoding,grayscale expansion,RSDS signal encoding,and control timing conversion display.Through the serial port setup parameters in FPGA soft-core Nios II,GAMMA and VCOM voltage can be programmed.Those parameters have power-down protection.The timing controller also adds BIT detection circuit which check the operation status in real-time.This high integration,low power consumption,simple structure timing controller circuit is suitable for special applications with high use value.

TFT-LCD;timing controller;FPGA;SOPC;BIT

TN141

A

10.3788/YJYXS20153004.0647

陳建軍(1966-),男,江西高安人,高級工程師,長期從事圖像處理方面的研究。E-mail:nedichen@aliyun.com

金強寧(1962-),男,江蘇南京人,研究員,長期從事平板顯示、光電子技術方面的研究。E-mail:jqn2004@126.com(聯系人)

1007-2780(2015)04-0647-08

2014-12-06;

2015-01-21.

*通信聯系人,E-mail:jqn 2004@126.com

章鵬(1987-),男,安徽滁州人,碩士,助理工程師,從事平板顯示技術方面的研究。E-mail:zpzone5971@ 163.com

劉凱麗(1988-),女,江蘇泰州人,碩士,助理工程師,從事平板顯示技術方面的研究。E-mail:kelly07050505@ 126.com