基于FPGA的DDR3多端口讀寫存儲管理設計※

吳連慧,周建江,夏偉杰

(南京航空航天大學 電子信息工程學院,南京 210016)

?

基于FPGA的DDR3多端口讀寫存儲管理設計※

吳連慧,周建江,夏偉杰

(南京航空航天大學 電子信息工程學院,南京 210016)

為了解決視頻圖形顯示系統中多個端口訪問DDR3時出現的數據存儲沖突問題,設計了一種基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR3讀寫操作。DDR3用戶接口仲裁控制模塊將中斷請求分成多個子請求,實現視頻中斷和圖形中斷的并行處理。幀地址控制模塊確保當前輸出幀輸出的是最新寫滿的幀。驗證結果表明,設計的DDR3存儲管理系統降低了多端口讀寫DDR3的復雜度,提高了并行處理的速度。

存儲器控制;多端口;幀地址;DDR3;FPGA

引 言

本文以Xilinx公司的Kintex-7系列XC7K410T FPGA芯片和兩片Micron公司的MT41J128M16 DDR3 SDRAM芯片為硬件平臺,設計并實現了基于FPGA的視頻圖形顯示系統的DDR3多端口存儲管理。

1 總體架構設計

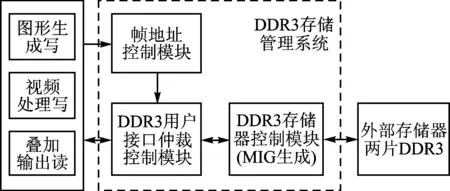

機載視頻圖形顯示系統中,為了實現多端口對DDR3的讀寫訪問,設計的DDR3存儲管理系統設計框圖如圖1所示,主要包括DDR3存儲器控制模塊、DDR3用戶接口仲裁控制模塊和幀地址控制模塊。

圖1 DDR3存儲管理系統設計框圖

DDR3存儲器控制模塊采用Xilinx公司的MIG[4](Memory Interface Generator)方案,通過用戶接口建立FPGA內部控制邏輯到DDR3的連接,用戶不需要管理DDR3初始化、寄存器配置等復雜的控制邏輯,只需要控制用戶接口的讀寫操作。

DDR3用戶接口仲裁控制模塊將每一個數據讀寫請求設置成中斷,借鑒中斷處理思想來進行仲裁控制,從而解決數據存儲的沖突問題。

幀地址控制模塊控制幀地址的切換。為了提高并行處理的速度,減少數據讀寫沖突,將圖形數據和視頻數據分別存儲在不同的DDR3中。

2 DDR3存儲器控制模塊設計

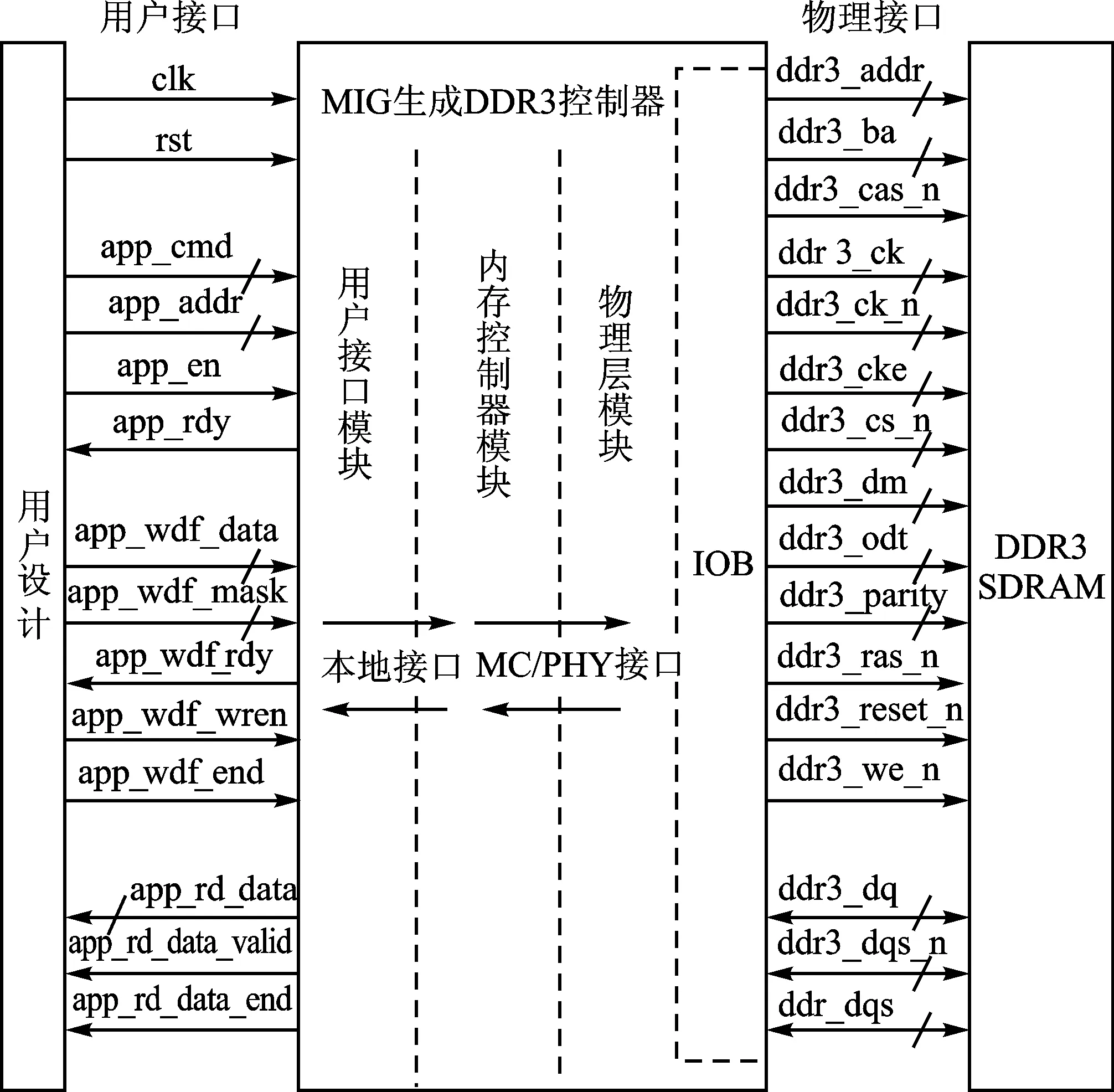

MIG生成的DDR3控制器的邏輯框圖[5]如圖2所示,只需要通過用戶接口信號就能完成DDR3讀寫操作,大大簡化了DDR3的設計。

圖2 DDR3控制器的邏輯框圖

2.1 DDR3控制模塊用戶接口寫操作設計

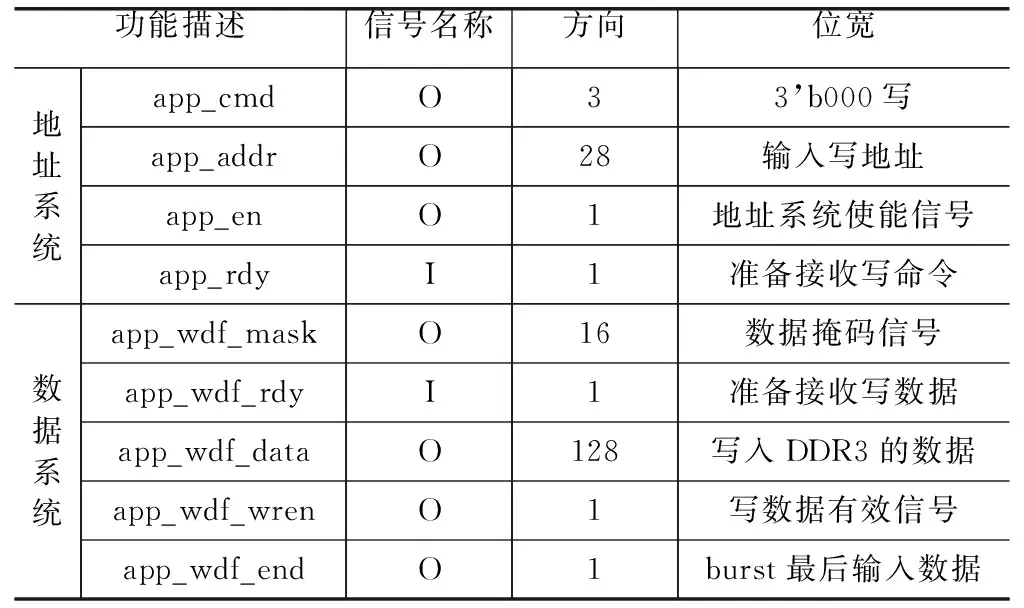

DDR3存儲器控制模塊用戶接口寫操作有兩套系統:一套是地址系統,另一套是數據系統。用戶接口寫操作信號說明如表1所列。

表1 DDR3控制器用戶接口寫操作信號說明

地址系統的內容是app_addr和app_cmd,兩者對齊綁定,app_cmd為000時為寫命令。當app_rdy(DDR3控制)和app_en(用戶控制)同時拉高時,將app_addr和app_cmd寫到相應FIFO中。數據系統的內容是app_wdf_data,它在app_wdf_rdy(DDR3控制)和app_wdf_wren(用戶控制)同時拉高時,將寫數據存到寫FIFO中。

為了簡化設計,本文設計的用戶接口寫操作時序如圖3所示,使兩套系統在時序上完全對齊。

圖3 DDR3寫操作時序圖(突發長度BL=8)

2.2 DDR3控制模塊用戶接口讀操作設計

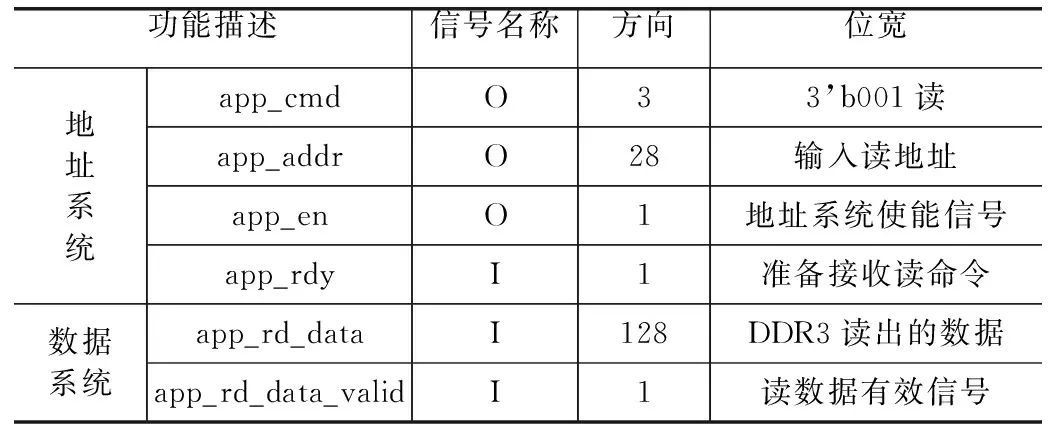

用戶接口讀操作也分為地址系統和數據系統。用戶接口讀操作信號說明如表2所列。

表2 DDR3控制器用戶接口讀操作信號說明

地址系統與寫操作相同,在時鐘上升沿且app_rdy為高電平時,用戶端口同時發出讀命令(app_cmd=001)和讀地址,并將app_en拉高,將讀命令和地址寫到FIFO中。對于數據系統,當app_rd_data_valid有效,則讀數據有效,讀回的數據順序與地址/控制總線請求命令的順序相同。

讀操作地址系統和數據系統一般是不對齊的,因為地址系統發送到DDR3后,DDR3需要一定的反應時間,讀操作時序如圖4所示。

圖4 DDR3讀操作時序圖(突發長度BL=8)

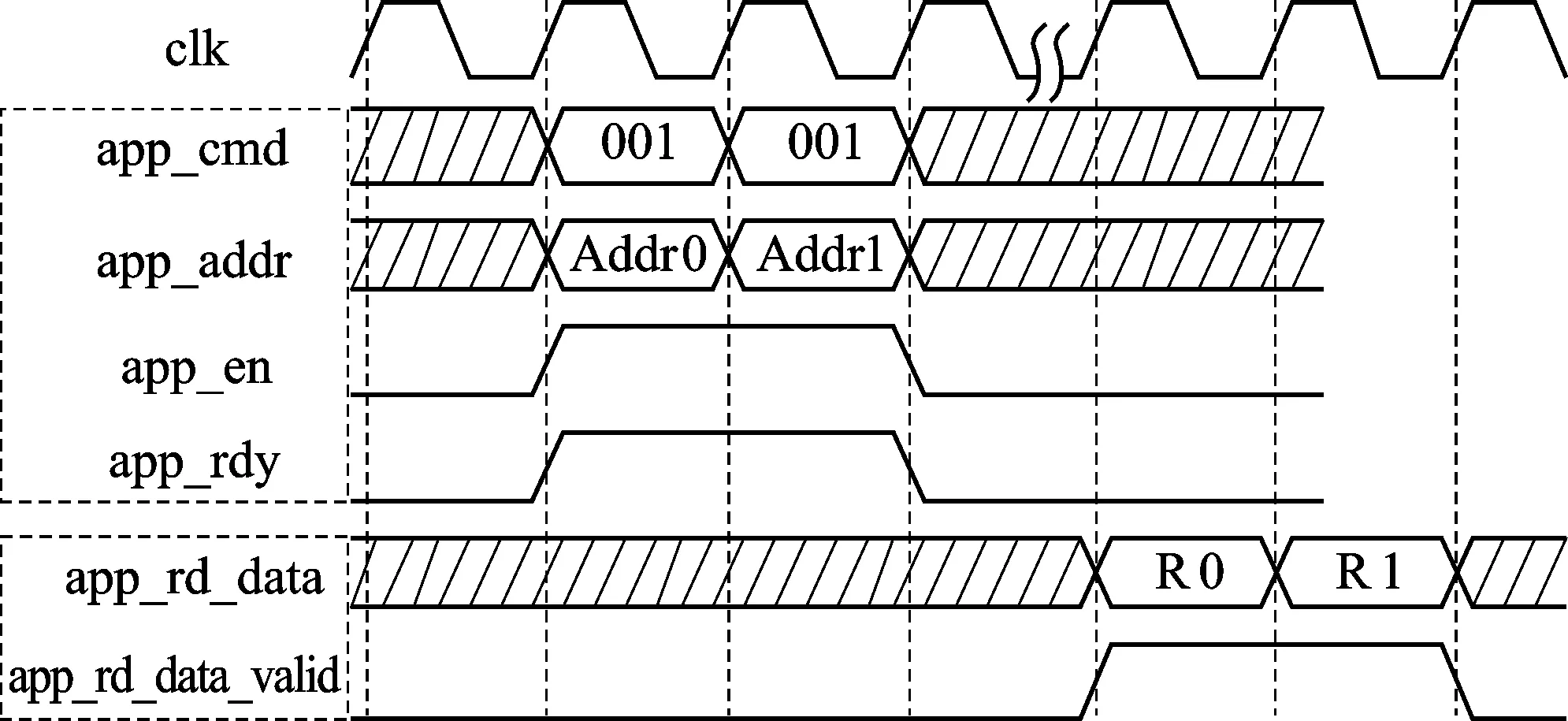

3 DDR3用戶接口仲裁控制模塊設計

每片DDR3只有一組控制、地址和數據總線,因此同一時刻只能有一個設備在訪問。常見的總線切換方式有兩種:一種是輪詢機制[6],軟件實現簡單,但實時性不高;另一種是仲裁機制[7],設備發送中斷請求,從而進行總線切換。由于視頻圖形顯示系統對實時性要求高,因此選擇仲裁機制。

DDR3用戶接口仲裁控制框圖如圖5所示。為了提高并行速度,將圖形和視頻分別進行中斷處理。將設備中斷請求解析成多個子請求,進行優先級判斷,每個子請求對應一個中斷處理邏輯。

圖5 DDR3用戶接口仲裁控制設計框圖

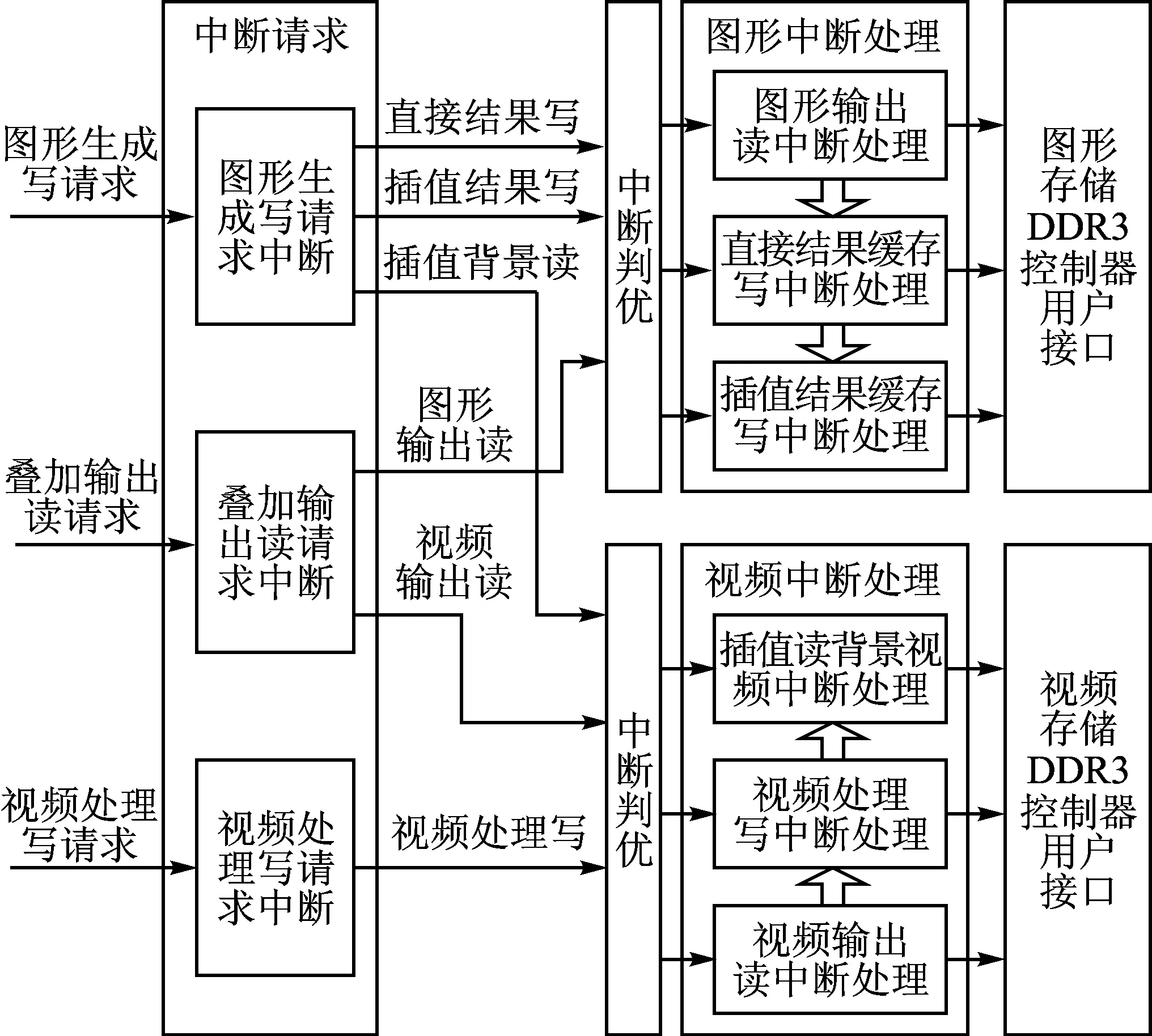

3.1 視頻處理寫請求中斷處理器設計

由于視頻處理寫請求不涉及到圖形中斷處理,所以對應一個子請求——視頻處理寫子請求。

視頻處理模塊將采集到的視頻經過縮放、旋轉等操作后存儲在緩存區中,當緩存區滿時發送視頻處理模塊寫請求。視頻處理寫中斷處理主要是從視頻處理模塊的緩存區中將地址和數據取出,寫入到視頻存儲DDR3中。

視頻處理寫請求中斷處理流程圖如圖6所示。當視頻處理模塊寫請求信號有效時,生成子中斷請求信號,若總線空閑則響應該中斷。當命令接收就緒(app_rdy=1)且數據接收就緒(app_wdf_rdy=1)時,從視頻處理緩存區中讀取地址和數據,同時發送寫命令、寫地址和寫數據。若緩存區為空,說明全部寫完,視頻處理寫中斷結束。

圖6 視頻處理寫請求中斷處理流程圖

3.2 疊加輸出讀請求中斷處理器設計

疊加輸出模塊需要從DDR3中將待輸出的圖形數據和視頻數據存儲到行緩存中,因此分為兩個子請求:視頻輸出讀請求和圖形輸出讀請求。由于兩者分別在圖形中斷處理和視頻中斷處理中完成,因此可以同時進行。

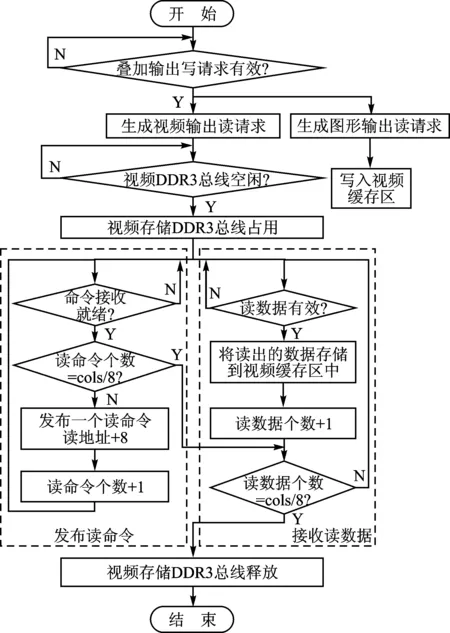

視頻輸出讀中斷處理主要從視頻存儲DDR3中讀取1行視頻數據,寫入到疊加輸出模塊的視頻緩存區中,視頻輸出讀中斷處理流程圖如圖7所示。本系統中突發長度BL=8,即每個用戶時鐘周期對應接收同一行地址中相鄰的8個存儲單元的連續數據。輸出視頻分辨率為cols×rows,則地址系統需要發送cols/8個突發讀命令。數據系統接收讀數據時,若讀數據有效(app_rd_data_valid=1),則將讀到的數據存儲到疊加輸出模塊的視頻緩存區中,同時讀數據個數加1。當讀數據個數為cols/8時,所有讀命令對應的讀數據全部接收,視頻輸出讀中斷處理結束。

圖7 視頻輸出讀中斷處理流程圖

圖形輸出讀中斷處理包含兩個步驟:從圖形存儲DDR3中讀取1行圖形數據,寫到疊加輸出模塊的圖形緩存區中;將剛剛搬移數據到圖形緩存區的DDR3存儲空間清零。前者與視頻輸出讀中斷的處理過程類似。

圖形數據寫入DDR3時只寫入有圖形的位置,而不是全屏掃描,如果不進行清屏操作會導致下一幀圖形畫面上殘留上一幀的圖形數據。清屏操作指圖形輸出后將DDR3中對應地址的存儲空間全部寫入數值0,從而將當前圖形數據清除。

3.3 圖形生成寫請求中斷處理器設計

為了提高讀寫速度,圖形中斷處理器中先進行直接結果寫中斷處理,同時視頻中斷處理器中進行插值背景視頻讀中斷處理,完成后再進行插值結果寫中斷處理。

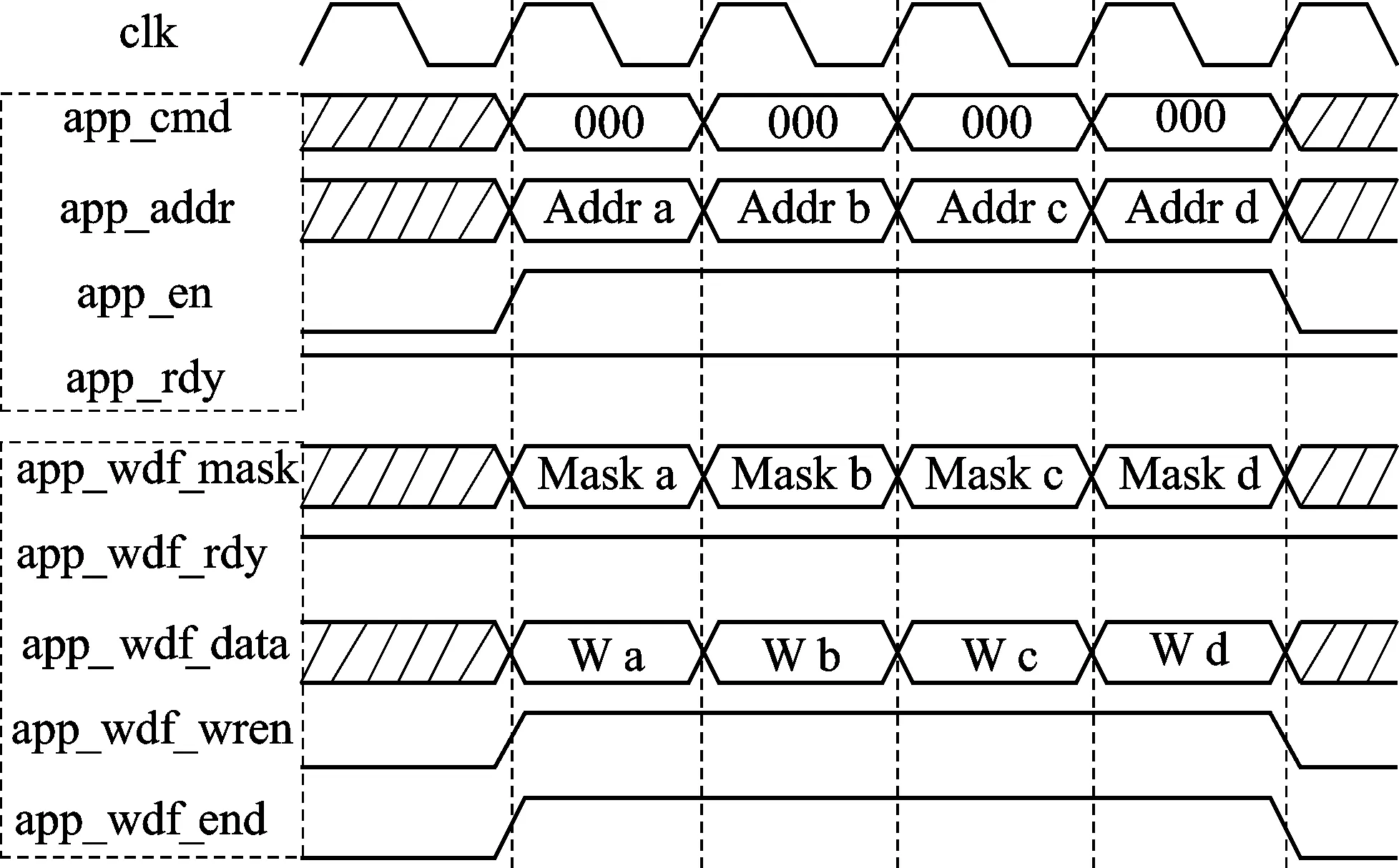

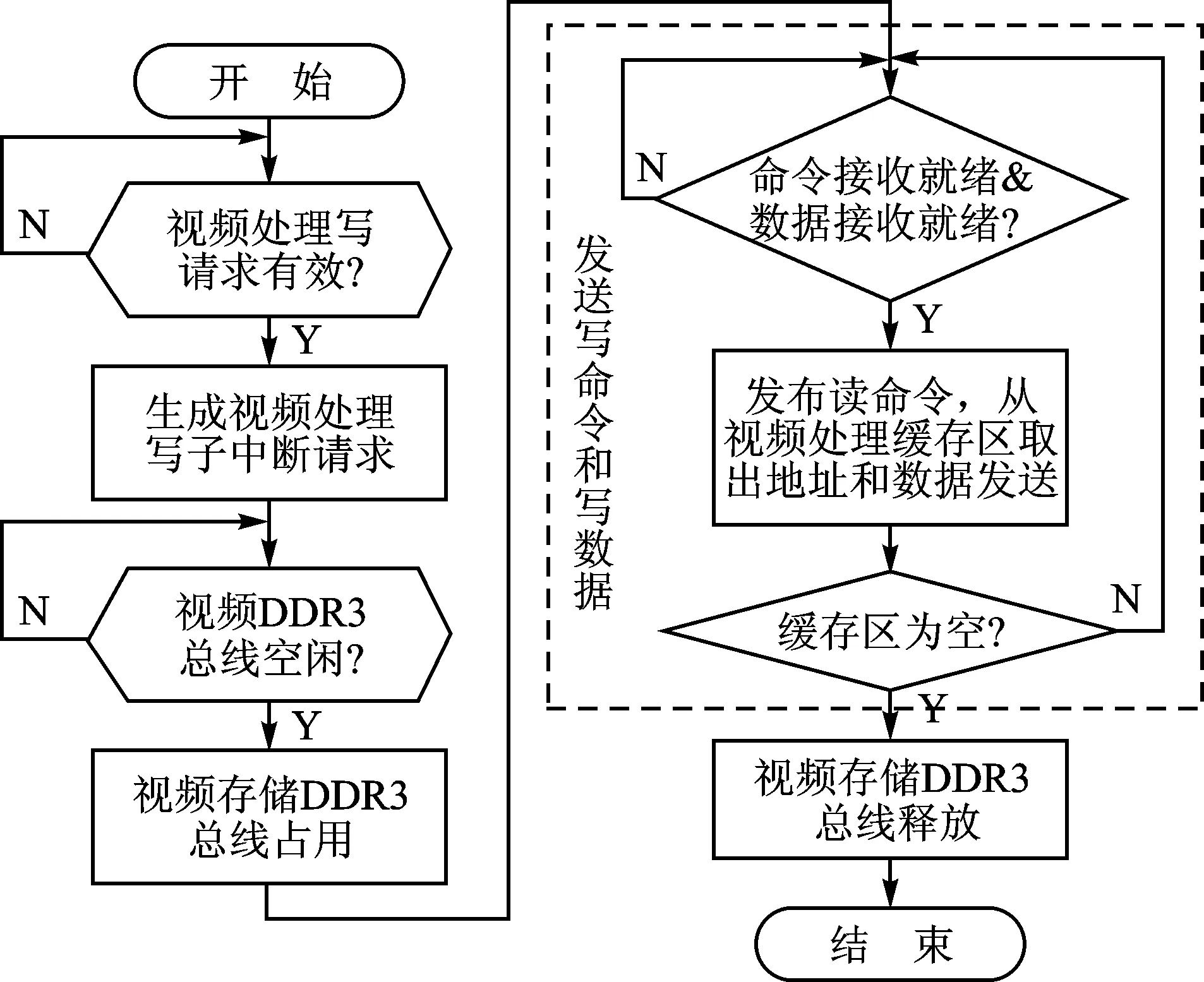

4 幀地址控制模塊設計

幀地址控制模塊主要是將DDR3空間進行劃分,同時控制幀地址的切換。為了簡化設計,將存儲器劃分為若干塊,每塊存儲一幀數據,在用戶仲裁控制模塊讀寫緩存區時只生成幀內地址,幀地址的切換由幀讀寫控制模塊實現,幀內地址結合幀地址組合成對應DDR3的內部地址值。DDR3的幀地址劃分如圖8所示。

圖8 DDR3幀地址劃分

設置三個幀存儲空間,其中一幀用于讀出,一幀用于寫入,還有一幀空閑,分別稱作輸入幀、輸出幀和空閑幀。用三者的切換來實現幀速率的轉換,確保輸出幀相對于當前輸入幀的延遲最小,即當前輸出幀輸出的是最新寫滿的幀。當寫入的幀存儲空間已經寫滿,而讀存儲空間還沒讀完,將下一幀的圖像數據寫入當前空閑的幀存儲空間。

圖9為PAL輸入幀和輸出幀讀寫控制流程圖。以A空間為輸出幀,B空間為輸入幀,C空間為空閑幀為例。若A空間讀完,B空間寫滿,則將B空間變成輸出幀并輸出,將C空間變成輸入幀并繼續輸入;若A空間還沒有讀完,B空間已經寫滿,則將下一幀數據寫入到C空間,并繼續從A空間輸出。

圖9 PAL輸入幀和輸出幀讀寫控制流程圖

5 驗證結果與分析

圖形生成寫中斷處理仿真圖略——編者注。

本文算法中,插值背景讀操作與直接結果寫操作同時在視頻中斷處理和圖形中斷處理中進行,利用并行操作減少時間,并大大降低了復雜度。

結 語

本文設計并實現了基于FPGA的DDR3多端口存儲管理,主要包括DDR3存儲器控制模塊、DDR3用戶接口仲裁控制模塊和幀地址控制模塊。DDR3存儲器控制模塊采用Xilinx公司的MIG方案,簡化DDR3的邏輯控制;DDR3用戶接口仲裁控制模塊將圖形和視頻分別進行中斷處理,提高了并行速度,同時簡化了仲裁控制;幀地址控制模塊將DDR3空間進行劃分,同時控制幀地址的切換。

經過分析,本文將圖形和視頻中斷分開處理,降低多端口讀寫DDR3的復雜度,提高并行處理速度。

[1] 謝軍,杜黎明,史小白.用SoC實現視頻圖形引擎功能的研究[J]. 單片機與嵌入式系統應用, 2002(10):6.

[2] Ladbury R L, Berg M D, Wilcox E P, et al. Use of Commercial FPGA-Based Evaluation Boards for Single-Event Testing of DDR2 and DDR3 SDRAMs. 2013.

[3] 劉德保, 汪安民. 多核DSP芯片TMS320C6678的DDR3接口設計[J]. 單片機與嵌入式系統應用, 2013,13(9):53-55.

[4] Xilinx Inc.Zynq-7000 SoC and 7 Series Devices Memory Interface Solutions v2.0, 2013.

[5] 劉立. 基于 MPSoC 的 DDR3 存儲器接口設計[D]. 南京:南京大學, 2013.

[6] 樊博, 王延杰, 孫宏海, 等. FPGA 實現高速實時多端口圖像處理系統的研究[J]. 液晶與顯示, 2013, 28(4): 620-625.

[7] 蘇丹, 任開春, 何春晗. ARM 嵌入式系統中觸摸屏的中斷控制方法[J]. 單片機與嵌入式系統應用, 2010(5): 71-72.

[8] 任政. 幀速率上變換算法研究[D]. 上海:上海交通大學, 2013.

[9] 張曉燕. 基于FPGA的機載視頻處理與圖形生成系統設計與實現[D]. 南京:南京航空航天大學, 2012.

吳連慧(碩士研究生),主要研究方向為機載信號處理及其FPGA技術;周建江(教授),研究方向為機載電子信息系統;夏偉杰(副教授),主要研究方向為信號處理。

Wu Lianhui,Zhou Jianjiang,Xia Weijie

(College of Electronic and Information Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,China)

In order to solve the problem of data storage conflicts of multi-port accessing DDR3 in the video and graphics display system, DDR3 storage management system based on FPGA is designed and implemented.MIG(Memory Interface Generator) is used to generate DDR3 controller in the DDR3 memory control module, so that the read and write operations can be done only through the user interface.The arbitration control module of DDR3 user interface turns interrupt request into multiple sub-requests,then it can complete video and graphics interrupt parallel processing.Frame address control module makes sure that the output frame is the latest filled frame.The results show that the design of storage management system simplifies the complexity of multi-port to read and write DDR3,and the speed of parallel processing is improved.

memory control;multi-port;frame address;DDR3;FPGA

TP333

A

迪娜

2014-07-03)