基于FPGA的可反饋式同步串行通信技術(shù)

蔣欣等

摘 要: 為了實(shí)現(xiàn)可反饋式高速同步串行總線設(shè)計,提出基于FPGA使用硬件描述語言(HDL)和利用串行通信的本身電氣特性設(shè)計出可反饋式電路,實(shí)現(xiàn)高可靠、高速率的同步串行總線通信方法。在工程應(yīng)用中驗(yàn)證了其高速率和高可靠性的總線傳輸特性,為提高LRM(現(xiàn)場可更換單元)級之間總線速率提供參考。

關(guān)鍵詞: 數(shù)據(jù)傳輸; FPGA; 串行總線; LVDS; 高級數(shù)據(jù)鏈路控制規(guī)程

中圖分類號: TN915?34 文獻(xiàn)標(biāo)識碼: A 文章編號: 1004?373X(2015)12?0139?04

0 引 言

同步串行高速總線在通信領(lǐng)域、自動控制領(lǐng)域發(fā)展迅猛,同時具有高可靠性、高傳輸速率的串行通信總線也在機(jī)載航電系統(tǒng)中得到廣泛應(yīng)用。同步串行高速總線不僅在成本、抗干擾能力和抗電磁干擾(EMI)的能力等方面能夠大大滿足現(xiàn)在高度綜合化、高度小型化的現(xiàn)場可更換模塊(LRU模塊)級機(jī)箱內(nèi)模塊與模塊之間的通信要求,也能夠利用同步串行總線靈活簡單的物理特性設(shè)計出可反饋式電路,增加通信的可靠性。

本文提出了一種基于FPGA的可反饋式硬件電路設(shè)計,采用硬件描述語言(HDL)實(shí)現(xiàn)了最高可達(dá)12.5 Mb/s的同步串行總線。

1 方案設(shè)計

隨著高集成度、高綜合化的機(jī)載航電設(shè)備的研制要求,在硬件設(shè)計中采用超大規(guī)模的FPGA和可反饋式電路設(shè)計,滿足體積小、重量輕、功耗低的高可靠性的航電設(shè)備設(shè)計需求。

1.1 原理設(shè)計

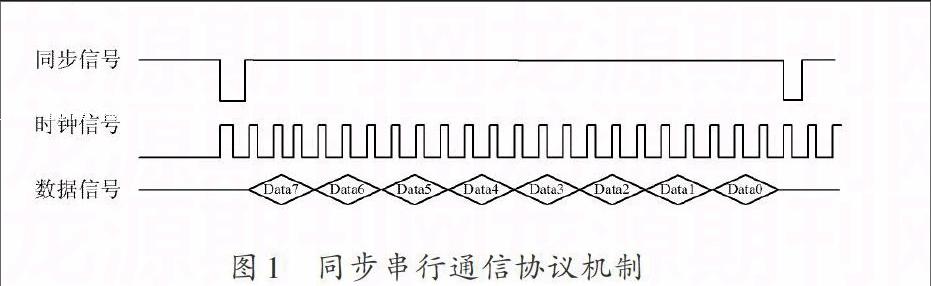

高速同步串行通信機(jī)制采用三線制同步串行通信,其中包括:幀同步信號、時鐘信號和串行數(shù)據(jù)。同步信號是發(fā)送端在同步時鐘的上升沿發(fā)出一個“低脈沖”給接收端,進(jìn)行串行數(shù)據(jù)通信握手。在低脈沖上升沿完結(jié)后的第一個同步時鐘周期的上升沿,連續(xù)發(fā)送8 B的串行通信數(shù)據(jù),發(fā)送端數(shù)據(jù)發(fā)送完畢后的第一個時鐘周期的上升沿,發(fā)送端發(fā)送一個“低脈沖”給接收端,進(jìn)行釋放數(shù)據(jù)通信握手。同步串行通信的時序圖,如圖1所示。

圖1 同步串行通信協(xié)議機(jī)制

串行同步傳輸過程中,發(fā)送端和接收端必須使用共同的時鐘源,才能保證它們之間的通信同步。同步數(shù)據(jù)傳輸時,在幀同步脈沖信號觸發(fā)下,串行數(shù)據(jù)信息以連續(xù)的數(shù)據(jù)幀形式發(fā)送,每個時鐘周期發(fā)送l B的數(shù)據(jù)。

采用LVDS標(biāo)準(zhǔn)的同步串行通信模式,利用LVDS標(biāo)準(zhǔn)的差分?jǐn)?shù)據(jù)傳輸?shù)碾姎馓匦裕岣叽型ㄐ啪€路的抗干擾能力和長距離數(shù)據(jù)傳輸?shù)臏?zhǔn)確性。在控制模式上,在發(fā)送端利用編碼器把待發(fā)送數(shù)據(jù)和同步時鐘組合在一起,通過物理差分?jǐn)?shù)據(jù)線發(fā)送到接收端;接收端的解碼器按照特定的數(shù)據(jù)格式(數(shù)據(jù)幀)從數(shù)據(jù)流中解析出同步時鐘頻率和數(shù)據(jù),共計4對LVDS差分線,實(shí)現(xiàn)發(fā)送端和接收端的全雙工同步串行通信。

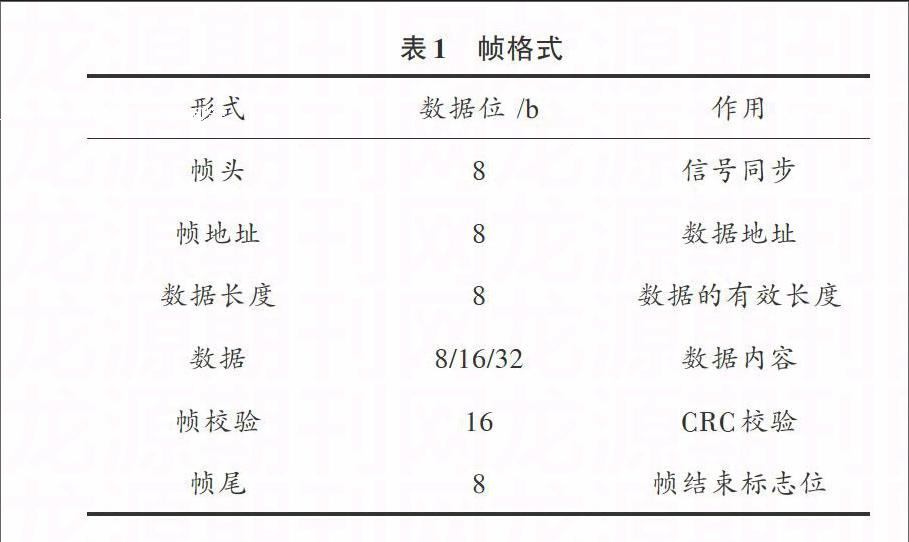

在LVDS標(biāo)準(zhǔn)的電氣特性上,數(shù)據(jù)通信格式采用了HDLC(高級數(shù)據(jù)鏈路控制規(guī)程)以“幀”為數(shù)據(jù)傳輸?shù)幕締挝唬ㄈ绫?所示),在所發(fā)送數(shù)據(jù)幀的幀頭增加數(shù)據(jù)標(biāo)志序列,接收端檢測出該標(biāo)志序列來實(shí)現(xiàn)同步。幀格式如表1所示。

表1 幀格式

1.2 硬件設(shè)計

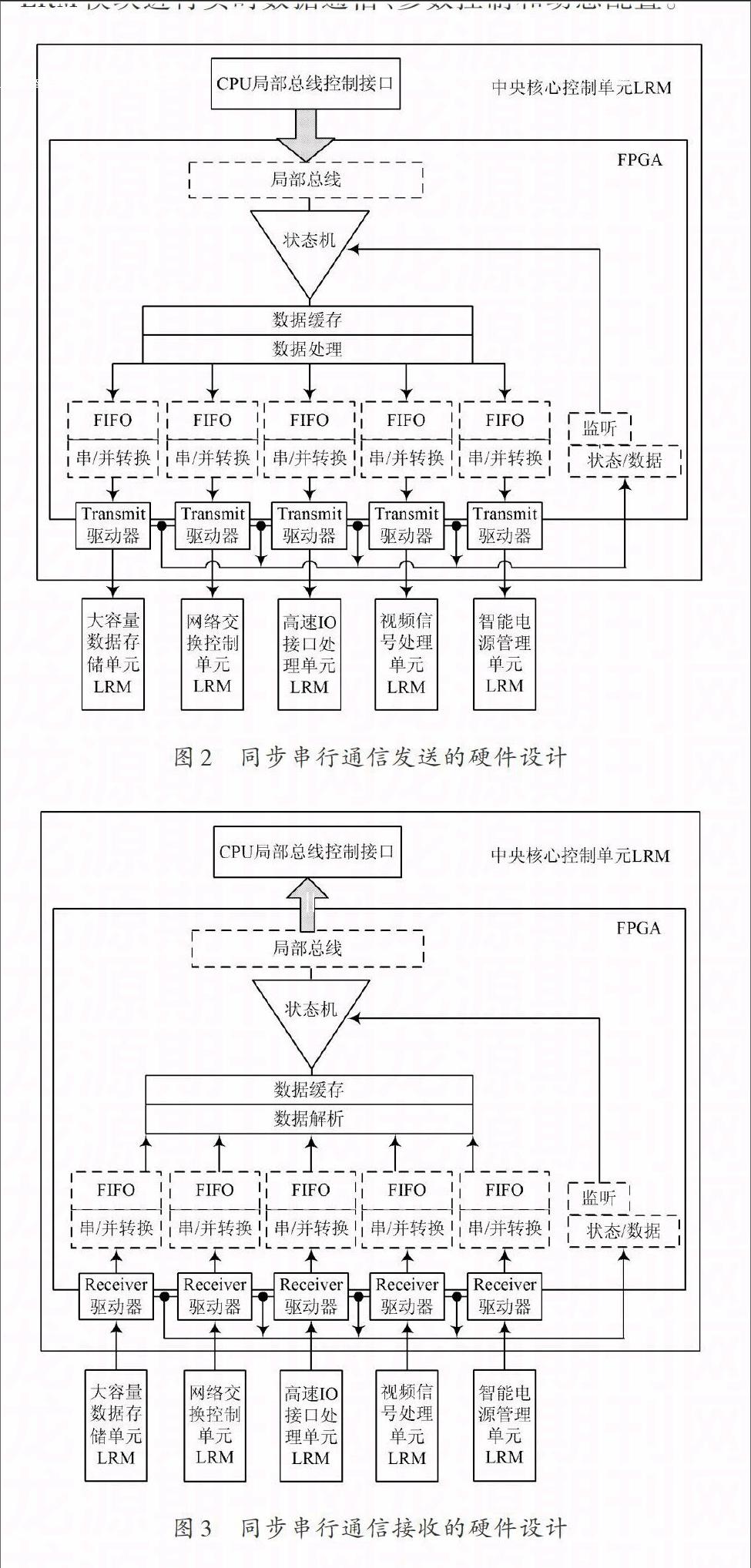

將具有同步機(jī)制的串行通信應(yīng)用在一個高度綜合化的航電設(shè)備中,不僅需要通信原理的高可靠性,也需要在物理電氣連接上的高可靠性。在實(shí)現(xiàn)高速、穩(wěn)定的同步串行通信時,也需要進(jìn)行發(fā)送響應(yīng)觸發(fā)機(jī)制和接收備份機(jī)制,保證發(fā)送數(shù)據(jù)的一致性和可偵測性,以及接收數(shù)據(jù)的有效性,因此,本文的同步串行通信硬件電路設(shè)計增加了發(fā)送端和接收端的可反饋式硬件電路設(shè)計。

FPGA的串行通信接口與LVDS驅(qū)動器連接,發(fā)送端設(shè)計了硬件的發(fā)送反饋,在接收端設(shè)計了硬件的接收備份,同時在FPGA的內(nèi)部采用發(fā)送比較器和接收緩沖器的冗余處理,以保證發(fā)送端的數(shù)據(jù)監(jiān)聽正常,接收端的數(shù)據(jù)雙重備份,防止數(shù)據(jù)在發(fā)送或接收的過程中,產(chǎn)生丟數(shù)或者誤碼。高可靠性的同步串行通信電路硬件設(shè)計如圖2和圖3所示。

將可反饋式同步串行通信在速率快和通道多的綜合化航電設(shè)備中使用,則具有高可靠的通信機(jī)理是保證綜合化航電設(shè)備運(yùn)行正常的基礎(chǔ)。可反饋式同步串行通信的工程化應(yīng)用設(shè)計如圖4所示,其中,綜合化航電設(shè)備都是采用現(xiàn)場可更換模塊(以下簡稱“LRM”),中央核心控制單元LRM與其他5個LRM模塊之間需要實(shí)時響應(yīng)。

中央核心控制單元LRM通過同步串行通信采用點(diǎn)對點(diǎn)全雙工模式,分別與智能電源管理單元LRM,高速I/O接口處理單元LRM,視頻信號處理單元LRM,大容量數(shù)據(jù)存儲單元LRM,網(wǎng)絡(luò)交換控制單元LRM這5個LRM模塊進(jìn)行實(shí)時數(shù)據(jù)通信、參數(shù)控制和動態(tài)配置。

如果中央核心控制單元同時接收、解析這5個LRM模塊的串口通信數(shù)據(jù),面臨的困境有:

(1) 依照目前CPU集成的串口控制器的處理速度將不能滿足綜合化航電設(shè)備通信的實(shí)時性要求;

(2) 采用傳統(tǒng)的點(diǎn)對點(diǎn)的通信方式,CPU不能有效監(jiān)控數(shù)據(jù)是否發(fā)送成功,只能等待握手時間超時,嚴(yán)重影響系統(tǒng)正常運(yùn)行。

要實(shí)現(xiàn)如此高速可靠的串行通信,采用基于硬件的反饋機(jī)制處理同步串行通信保證了綜合航電設(shè)備內(nèi)部各個LRM模塊之間通信的可靠性,并且在FPGA內(nèi)部實(shí)現(xiàn)上百兆時鐘的邏輯處理和并行多通道控實(shí)現(xiàn)高速多通道同步串行通信,保證了綜合航電設(shè)備內(nèi)部各個LRM模塊之間通信的實(shí)時性。

在中央核心控制LRM模塊中,通用FPGA內(nèi)部設(shè)計了串行通信管理狀態(tài)機(jī)(分為接收狀態(tài)機(jī)和發(fā)送狀態(tài)機(jī)),并行地解析和處理串行通信線路上的數(shù)據(jù),進(jìn)行緩存后再通知CPU來接收數(shù)據(jù),或者CPU接收到發(fā)送狀態(tài)機(jī)的指令,集中處理要發(fā)送的數(shù)據(jù)放入到FPGA的發(fā)送緩存中,由發(fā)送狀態(tài)機(jī)自行按照各個通道的串口通信狀態(tài)獨(dú)立控制發(fā)送。如圖2和圖3所示,F(xiàn)PGA完成同步串行通信通道的管理。這樣由FPGA完成各個通道同步串行通信的任務(wù),同時根據(jù)反饋式原理,保證串行通信線路上數(shù)據(jù)的有效性。這樣就將中央核心控制LRM的CPU解放,不需要CPU參與串口通信寄存器的保護(hù)和恢復(fù)現(xiàn)場,以及與外部存儲器通信所帶來的龐大時間開銷,由此來滿足中央核心控制單元與能電源管理單元、高速I/O接口處理單元、視頻信號處理單元、大容量數(shù)據(jù)存儲單元和網(wǎng)絡(luò)交換控制單元的高速同步串行總線的通信時序要求。

綜合航電設(shè)備上電后,中央核心控制LRM模塊同時給各個LRM模塊發(fā)出“握手信號”,中央核心控制LRM給各個LRM模塊發(fā)出同步串行通信數(shù)據(jù)幀。中央核心控制LRM模塊的FPGA集成一個微控制器(硬核),僅需要通知中央核心控制LRM的CPU,通過CPU的局部總線接口(LocalBus)將所有的發(fā)送各個LRM模塊的數(shù)據(jù)放到一個數(shù)據(jù)緩存中,再發(fā)送一個啟動發(fā)送指令,F(xiàn)PGA內(nèi)部的狀態(tài)機(jī)自行將數(shù)據(jù)緩存中的數(shù)據(jù)進(jìn)行發(fā)送數(shù)據(jù)處理,再向各個通道的FIFO中放入待發(fā)送數(shù)據(jù),啟動串并轉(zhuǎn)換協(xié)議向同步串行通道發(fā)送數(shù)據(jù),同時反饋電路接收到各個通道的LVDS驅(qū)動器發(fā)送數(shù)據(jù)后,F(xiàn)PGA將反饋數(shù)據(jù)與FIFO數(shù)據(jù)進(jìn)行比對,分為以下兩種情況:

(1) 如果正確,記錄發(fā)送狀態(tài),清除FIFO中待發(fā)送數(shù)據(jù),等待下一幀待發(fā)送數(shù)據(jù);

(2) 如果不正確,啟動應(yīng)急處理,給接收端發(fā)送“數(shù)據(jù)丟棄”幀,同時再從FIFO中發(fā)送數(shù)據(jù),再通過反饋電路進(jìn)行比對,如再錯,記錄發(fā)送狀態(tài),發(fā)出告警同步給CPU,放棄該通道的同步串行數(shù)據(jù)發(fā)送。

中央核心控制LRM模塊的同步串行通信接收端也是FPGA+LVDS驅(qū)動器實(shí)現(xiàn)的。FPGA中的狀態(tài)機(jī)自行解析各個通道同步串行數(shù)據(jù),同時啟動反饋電路采集各個通道的數(shù)據(jù),F(xiàn)PGA狀態(tài)機(jī)進(jìn)行比對,分為以下兩種情況:

(1) 如果正確,將有效的幀數(shù)據(jù)存放到FPGA內(nèi)部的數(shù)據(jù)緩存中,并通知FPGA中集成的微控制器讀取數(shù)據(jù)放入CPU的數(shù)據(jù)緩存中,記錄接收狀態(tài);

(2) 如果不正確,該通道的發(fā)送端發(fā)送“接收錯誤”幀,記錄接收狀態(tài),要求發(fā)送端再次發(fā)送,同時清除該通道反饋電路中的數(shù)據(jù),等待再次發(fā)送的數(shù)據(jù),如果再次接收比對正確,修改接收狀態(tài),再不正確,記錄接收狀態(tài),發(fā)出告警同步給CPU,放棄該通道的同步串行數(shù)據(jù)接收。

根據(jù)以上的工作原理,設(shè)計了發(fā)送和接收的FPGA邏輯控制流程,流程圖如圖5所示。

2 設(shè)計驗(yàn)證

在綜合化航電設(shè)備中,啟動中央核心控制LRM模塊分別與其他5個LRM模塊同時進(jìn)行數(shù)據(jù)發(fā)送和數(shù)據(jù)接收,要求每50 ms周期內(nèi),需完成中央核心控制模塊分別向各5個LRM模塊連續(xù)發(fā)送320 B數(shù)據(jù),并完成數(shù)據(jù)組包和數(shù)據(jù)發(fā)送。同時,要求每30 ms周期內(nèi)需完成中央核心控制LRM分別接收5個LRM模塊的數(shù)據(jù)發(fā)送來的128 B數(shù)據(jù),并完成數(shù)據(jù)解析和數(shù)據(jù)處理。通過連續(xù)發(fā)送和接收測試,監(jiān)測是否會存在丟包現(xiàn)象。

通過20 000幀數(shù)據(jù)為周期,持續(xù)近2 h的測試工作,未發(fā)現(xiàn)丟包及異常現(xiàn)象。在監(jiān)測過程中,實(shí)測的傳輸速率達(dá)到12.25 Mb/s。通過人為在傳輸線路上注入故障,中央核心控制模塊和各個LRM模塊能夠準(zhǔn)確檢測到傳輸通道故障。

3 結(jié) 語

該方案設(shè)計的實(shí)現(xiàn)大大減輕了CPU的處理負(fù)荷,有效利用超大規(guī)模的FPGA內(nèi)部資源實(shí)現(xiàn)高速可靠的同步串口通信技術(shù),不易受外界干擾,推廣到目前綜合化航電設(shè)備的高速數(shù)據(jù)傳送系統(tǒng)中。

參考文獻(xiàn)

[1] 張磊,張小林,楊百平.無人機(jī)機(jī)載設(shè)備串行通信測試系統(tǒng)的設(shè)計[J].計算機(jī)測量與控制,2010,18(1):26?28.

[2] 郭先樹.利用TL16C550B實(shí)現(xiàn)DSP與PC機(jī)的異步串行通信[J].華東交通大學(xué)學(xué)報,2003,20(2):63?66.

[3] 任曉東.CPLD/FPGA高級應(yīng)用開發(fā)指南[M].北京:電子工業(yè)出版社,2003.

[4] 楊小強(qiáng),黃智剛,張軍,等.基于空地數(shù)據(jù)鏈的飛機(jī)狀態(tài)監(jiān)控系統(tǒng)的實(shí)現(xiàn)[J].電訊技術(shù),2003,43(1):68?72.

[5] 馮春陽,張遂南.三線制同步串行通信控制器接口設(shè)計[J].現(xiàn)代電子技術(shù),2009,32(19):80?82.

[6] 杜曉斌,陳興文.FPGA和單片機(jī)串行通信接口的實(shí)現(xiàn)[J].微計算機(jī)信息,2004(9):71?72.

[7] 魏祎,許永輝.基于PXI總線的航空串行總線專用通訊模塊研制[J].現(xiàn)代電子技術(shù),2014,37(17):86?89.

[8] 邱偉.機(jī)載電子設(shè)備間高速數(shù)據(jù)傳輸研究[J].現(xiàn)代電子技術(shù),2014,37(12):30?31.