基于FPGA的高速圖像數據存儲系統

李超,呂曉龍

哈爾濱工程大學自動化學院,黑龍江哈爾濱 150001

基于FPGA的高速圖像數據存儲系統

李超,呂曉龍

哈爾濱工程大學自動化學院,黑龍江哈爾濱 150001

為滿足高速全景圖像的實時無損存儲的需求,設計了基于現場可編程門陣列(field-programmable gate array,FP-GA)的SATA陣列和TF卡陣列嵌入式存儲系統。用2片FPGA作為控制器,分別負責全景圖像的采集處理任務與存儲傳輸任務,設計了8層PCB板級硬件系統并對高速數字信號線進行了細致的阻抗匹配,并設計了支持SD3.0協議的RTL級控制器。實際測試TF卡陣列存儲平均速度為227.36 MB/s,峰值速度達293 MB/s,實現了數據的高速存儲功能。

全景視覺;現場可編程門陣列;TF陣列;SD3.0;高速存儲;阻抗匹配

隨著圖像傳感器制造技術的高速發展,數碼相機的分辨率和速度都有大幅提升,因此對圖像的處理能力和存儲能力都提出了越來越高的要求。與PC系統相比,嵌入式的圖像采集、處理和存儲系統具有高速的處理和存儲數據的能力,實時性強并具有大數據量、小型化的特點。

全景視覺視野范圍可以達到180°~360°,廣泛應用于監控、視覺導航、太空探測、機器人等領域。由于全景圖像數據量大且速度快,很難實現圖像采集之后的實時無損存儲,本文針對高速全景圖像采集系統,構建基于現場可編程門陣列(Field-Pro-grammable Gate Array,FPGA)的專用嵌入式高性能圖像實時存儲系統,滿足數據的高速、大容量、實時性的要求。

西安電子科技大學的NAND Flash存儲陣列容量為800 GB,存儲速度達到300 MB/s[1]。中科院空間中心以NAND Flash作為存儲介質,以四級流水線的方式,最高存儲速率達500 Mbit/s,存儲容量達128 Gbit,并可以擴展[2]。信億科技的ANS-9012固態硬盤,采用SDHC卡陣列作為存儲介質,平均讀取速度為121.4 MB/s。臺灣友晶公司的DE4開發平臺,以Altera Stratix IV GX系列的FPGA為主控芯片并配有4路SATA硬盤接口。國內自由電子科技代工設計的“高速高清DVR板”采用Xlinx的Virtex5系列的FPGA,設計了2路高速CameraLink接口,支持DDR2緩存和12路SATA硬盤[3]。

這些開發平臺覆蓋了圖像采集、傳輸和存儲功能,但造價非常高昂,適用于通用驗證平臺,不適合針對性很強的應用。對于高速全景圖像而言,采集、處理、存儲的數據量大,實現實時無損非易失性存儲的難度很大。

1 總體方案設計

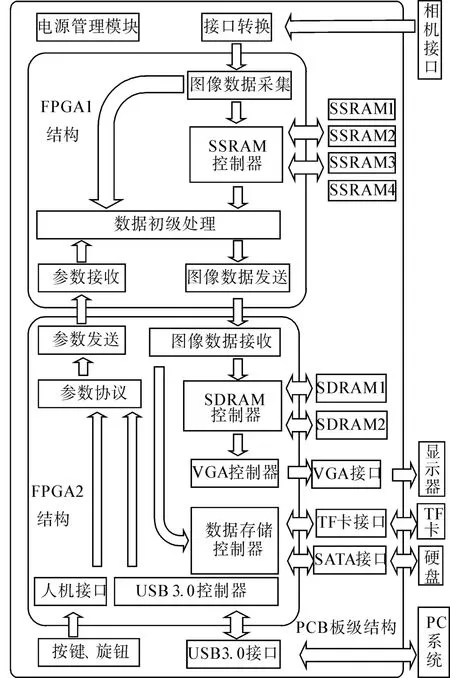

在高速系統設計中,一般都遵循面積和速度的平衡互換原則,本文將數據流串并轉換,把高速的串行數據流分流為多路并行處理單元進行數據存儲。本系統采用2片FPGA分別進行圖像的采集處理與存儲傳輸。如圖1所示為系統結構圖,FPGA1選用EP3C80F780,與4片SSRAM和2路CameraLink接口構成高速圖像采集處理子系統;FPGA2選用帶有高速串行解串器的EP4CGX110DF31[4-5],設計了4 路SATA接口和8路高速TF卡接口,分別實現硬盤陣列和TF卡陣列,實現圖像的存儲功能,USB3.0接口與VGA接口分別實現傳輸與顯示功能。

圖1 系統結構圖

2 板級系統設計

2.1 硬件電路設計

2.1.1 高速接口的布線及阻抗匹配

本文設計了8層PCB板級硬件系統,多層PCB不僅擴大了布線空間,而且合理的分層設計能夠提高電源的純凈度和信號的質量,不僅能減少外界環境的干擾,也能減少PCB對外界的電磁輻射[6]。

SATA和USB3.0差分信號對與TF卡數據線都是高速數字信號,對阻抗匹配和信號走線都有很高的要求,否則會產生振鈴、反射等不良現象。SATA差分信號對必須滿足單端阻抗60Ω(±15%),差分阻抗100Ω (±15%)的要求,USB3.0信號線的阻抗要求為單端阻抗60Ω(±15%),差分阻抗90Ω(±15%)。

借助PCB阻抗設計軟件Polar SI9000計算信號線的參數,當線寬為5 mil,線間距為7 mil,層高為6 mil,信號線厚度為1.4 mil(1 oz)時,單端阻抗為66.4Ω,差分阻抗為107.9Ω,滿足系統要求,其他高速差分信號線的匹配阻抗值如表1所示。

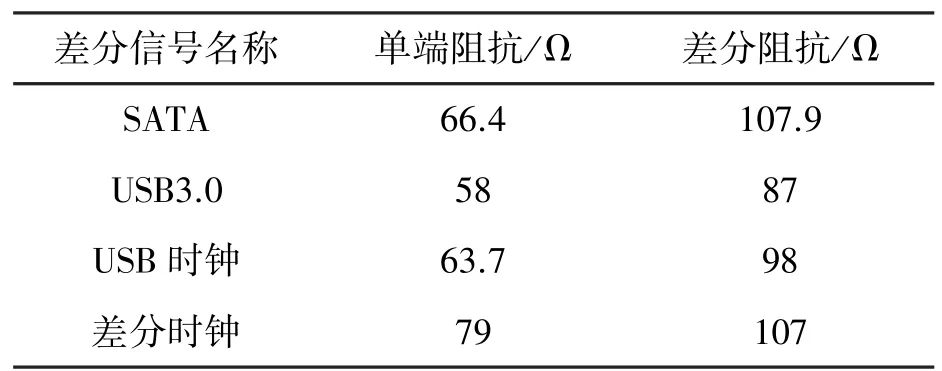

表1 高速差分信號線的匹配阻抗值

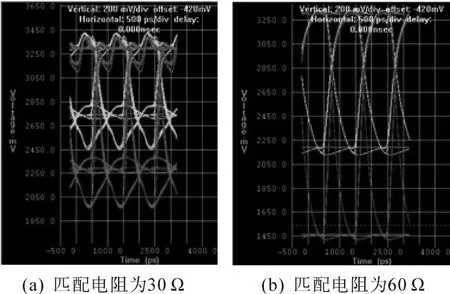

2.1.2 PCB板級硬件電路信號完整性分析

利用HyperLynx軟件對關鍵的高速差分信號與TF卡數據信號線進行板級信號完整性分析,驗證布線合理性,及時修改不滿足要求的信號線,如圖2所示為TF卡數據線在不同匹配電阻時的信號圖,圖2(a)的匹配電阻為30Ω,信號有較大的超調和抖動,把匹配電阻調為60Ω后,如圖2(b)所示,信號質量有了明顯提升。如圖3所示為存儲系統的硬件板級系統。

圖2 TF卡數據信號線在不同匹配電阻時的信號

圖3 高速圖像數據存儲裝置的硬件板級系統

2.2 SD3.0協議的RTL級設計

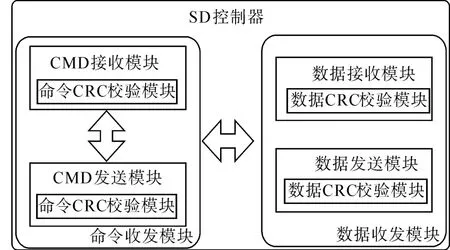

支持SD3.0總線協議[7]的TF卡速度等級為UHS-I,最高讀寫速度達104 MB/s,TF卡有3種工作模式:非激活模式、卡識別模式和數據傳輸模式。圖4為SD控制器的結構,控制器由命令傳輸模塊和數據傳輸模塊構成,命令和數據管理分開控制,便于數據控制和調試。數據模塊受命令模塊控制,2個模塊之間進行通訊協作,數據模塊根據命令模塊發出的命令進行數據的發送或接收,這樣結構緊湊,控制方便,而且可以減少FPGA的資源消耗。

圖4 SD控制器結構

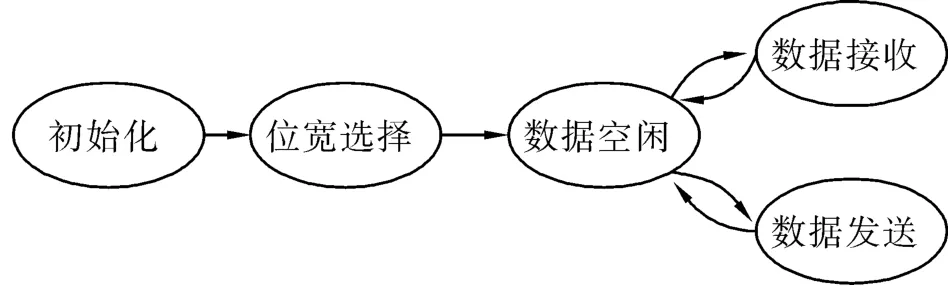

卡識別模式下的工作狀態轉換為:空閑狀態—準備狀態—認證狀態[8-10]。數據傳輸模式的工作狀態為:就緒狀態—傳輸狀態—發送/接收數據狀態。卡先進入就緒狀態,主機獲取CSD寄存器信息后,發送CMD7使要操作的卡進入傳輸狀態,然后主機發送ACMD6設置傳輸數據線的寬度,主機發送CMD18,從TF卡讀數據,發送CMD25,對TF卡寫數據。寫入數據時,采用多塊預擦除和多塊讀寫操作,在多塊寫操作時,先發送CMD23設定要進行寫操作的數據塊數,然后發送ACMD23進行多塊預擦除,最后發送CMD25進行多數據塊寫操作。用Verilog HDL語言描述SD主機控制器,并通過有限狀態機(FSM)實現狀態跳轉[11],如圖5所示為SD主機的有限狀態機。

圖5 SD主機的有限狀態機

3 系統測試分析

本系統使用SanDisk公司的Extreme Pro移動存儲卡進行測試,單卡容量為16 GB,速度等級為UHS-I。采用SignalTap II工具對FPGA信號進行采樣分析,圖6為采集到的TF卡正確初始化過程。

圖6 SignalTap II采集到的TF卡初始化過程

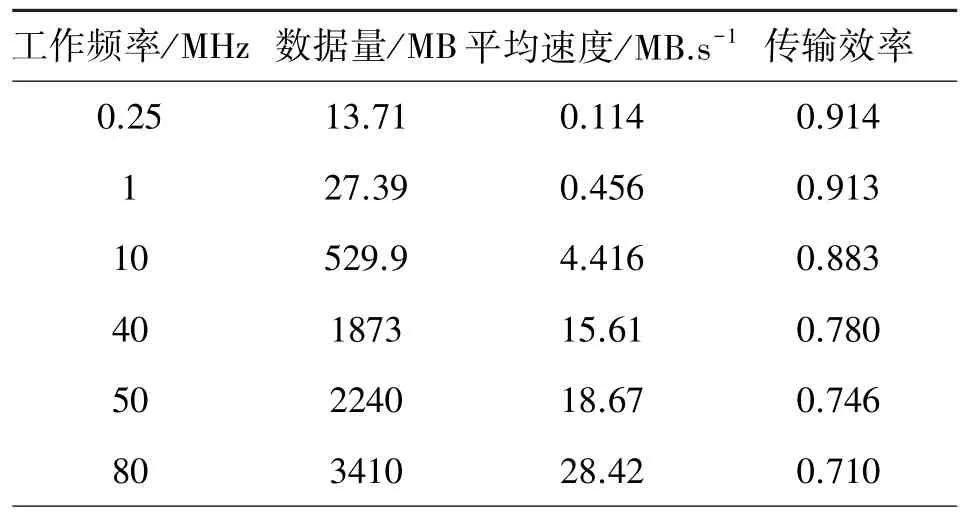

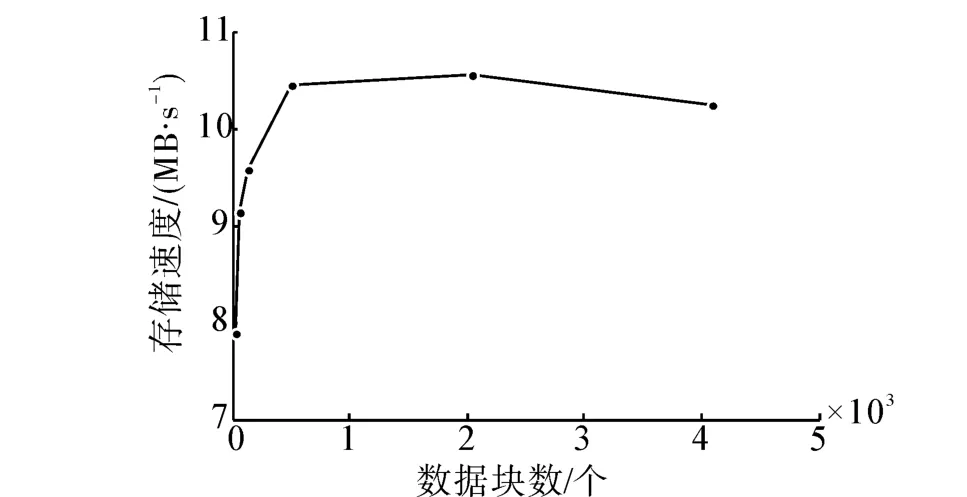

對系統分別進行固定存儲時間和固定存儲數據量的存儲測試。固定存儲時間存儲,是向TF卡寫入120 s時長的數據,每次讀寫2 048塊數據,在不同的工作頻率下,測試TF卡的實際存儲速度,測量參數如表2所示,存儲速度與工作頻率之間的關系如圖7所示。固定存儲數據量存儲,是向TF卡寫入1 GB的數據,工作頻率為25 MHz時,單次寫入不同的數據塊數,測試TF卡的存儲速度,測量參數如表3所示,存儲速度與讀寫塊數之間的關系如圖8。

表2 固定存儲時間存儲測試參數(每次讀寫2 048塊數據)

圖7 存儲速度與工作頻率之間的關系

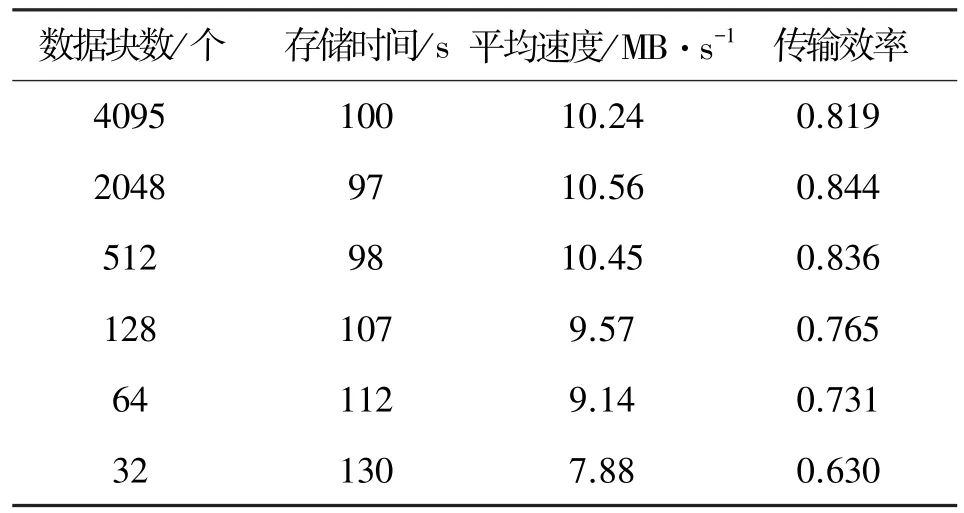

表3 固定存儲數據量存儲測試參數(工作頻率為25 MHz)

圖8 存儲速度與讀寫數據塊數之間的關系

由實驗數據得,每次讀寫數據塊數固定時,隨著工作頻率增加,實際傳輸速度逐漸增大,最大平均速度為28.42 MB/s,但傳輸效率卻逐漸降低,最大傳輸效率為91.43%。工作頻率固定時,每次讀寫數據在512塊以上時,傳輸效率穩定在84%左右,在512塊以下時,隨著數據塊的減少,傳輸效率逐漸降低。工作頻率為80 MHz,單次寫入數據塊數為2 048時,平均存儲速度最大為28.42 MB/s,此時小塊數據的周期為1 066,峰值速度為36.64 MB/s,傳輸效率為91.6%。在實驗中,只用8路TF卡陣列的2路接口進行TF卡陣列并行存儲的驗證。在SD3.0協議中,SDR50、SDR104等高速模式需要1.8 V的信號電壓,而此系統只能提供3.3 V的信號電壓。在3.3 V的信號電壓下,協議中高速模式的最高工作頻率為50 MHz,理論最高存儲速度為25 MB/s。而本系統的工作時鐘最高為80 MHz,超出額定工作頻率60%,實際測試本系統的工作時鐘最高為80 MHz,單卡平均速度為28.42 MB/s,峰值速度為36.64 MB/s,雙TF卡陣列的平均速度為56.84 MB/s,峰值速度為73.28 MB/s。若把8片TF卡全部加入到系統中,則平均速度為227.36 MB/s,峰值速度為293 MB/s,滿足高速存儲的要求。

4 結論

針對高速全景圖像的實時無損存儲,本文設計了基于FPGA的SATA陣列和TF卡陣列嵌入式存儲系統。通過設計、仿真與實際測試結果表明:

1)此雙FPGA系統方案,實現了數據采集處理與存儲傳輸任務的分離,效率更高。

2)設計的8層PCB板級硬件系統,能夠滿足SATA、USB3.0等高速數字信號的傳輸要求。

3)設計的RTL級TF卡控制器支持SD3.0協議,在3.3 V信號電壓時,單卡存儲的平均速度為28.42 MB/s,峰值速度達36.64 MB/s。

4)設計的TF卡陣列,實際測試平均速度為227.36 MB/s,峰值速度為293 MB/s。

本系統實現了嵌入式TF卡陣列的高速圖像實時無損存儲功能,可廣泛應用于全景視覺、機器人視覺導航、監控等領域,具有很好的實際應用價值。

[1]方火能.高速大容量存儲陣列控制器的設計與實現[D].西安:西安電子科技大學,2012:41-59.

[2]陳斌,沈衛華.嫦娥二號衛星大容量存儲器設計[J].航天器工程,2011(5):99-104.

[3]孫長勝.高速攝影系統中海量數據存儲器研究[D].成都:電子科技大學,2011:1-6.

[4]吳繼華,蔡海寧.Altera FPGA/CPLD設計:2版[M].北京:人民郵電出版社,2011:46-100.

[5]Altera Corporation.Cyclone IV Device Handbook[EB/OL].[2012-12-01].www.altera.com.cn.

[6]王劍宇,蘇穎.高速電路設計實踐[M].北京:電子工業出版社,2010:1-280.

[7]SD Group.SD Specifications Part 1 Physical Layer Simpli-fied Specification Version 3.01[S].2010.

[8]李顯龍.基于SD總線的FPGA加解密算法實現[D].廣州:華南理工大學,2012:6-14.

[9]王清,劉新寧.SD卡硬件啟動和數據存儲的控制邏輯的設計實現[J].電腦知識與技術,2008(31):990-991.

[10]唐磊,洪傳榮.基于FPGA的SD卡控制器設計[J].電聲技術,2011(3):29-31.

[11]夏宇聞.Verilog數字系統設計教程:2版[M].北京:北京航空航天大學出版社,2010:20-300.

High-speed image data storage system based on FPGA

LIChao,LYU Xiaolong

College of Automation,Harbin Engineering University,Harbin 150001,China

In order to satisfy the need for the real-time and loss-less storage of a high-speed panoramic image,an embedded image data storage system based on FPGA with SATA array as well as TF card array is designed.The controller consists of two pieces of FPGAs,which and they are in charge of collecting/processing and storing/trans-fermissions of the panoramic image respectively.Further,a hardware system with a PCB board of eight layers is devised,and an impedancematch is performed for the high-speed digital signal lines.Then,an RTL-level control-ler that supportes SD3.0 protocol is projected.Finally,the actual test shows that the average speed of TF cards ar-ray is 227.36 MB/s and the peak speed is up to 293 MB/s,thus a high-speed storage capacity of the data is a-chieved by the developed system.

panoramic vision;field-programmable gate array(FPGA);TF array;SD3.0;high-speed storage;im-pedancematching

TN911

A

1009-671X(2015)02-44-04

10.3969/j.issn.1009-671X.201503016

2015-03-19.

日期:2015-04-08.

國家自然科學基金資助項目(61175089,61203255).

.李超(1991-),男,碩士研究生;

呂曉龍(1977-),男,講師.

呂曉龍,E-mail:35122911@qq.com.

http://www.cnki.net/kcms/detail/23.1191.U.20150408.1448.001.html