考慮場板邊緣效應的SOI-pLDMOS表面電場模型及器件優化設計

葉 然 張春偉 劉斯揚 孫偉鋒

(東南大學國家專用集成電路系統工程技術研究中心, 南京 210096)

考慮場板邊緣效應的SOI-pLDMOS表面電場模型及器件優化設計

葉 然 張春偉 劉斯揚 孫偉鋒

(東南大學國家專用集成電路系統工程技術研究中心, 南京 210096)

針對帶有柵極場板的絕緣體上硅p型橫向雙擴散場效應晶體管(SOI-pLDMOS),提出了一種新型表面電場解析模型.相比于傳統模型,該模型充分考慮了場板邊緣效應對電場分布的影響,驗證結果顯示新模型能更好地符合Medici數值仿真結果.此外,基于所建立的器件表面電場模型,研究了柵極場板長度(包括多晶硅場板和金屬場板)及漂移區摻雜濃度對器件表面電場分布和擊穿特性的影響,進而對SOI-pLDMOS進行了優化設計.流片測試表明,所建立的新型表面電場解析模型能夠很好地指導器件參數設計,實現了器件耐壓和導通電阻的最佳折中.

解析模型;表面電場;SOI-pLDMOS;邊緣效應

p型橫向雙擴散場效應晶體管(p-type lateral double diffusion MOS transistor, pLDMOS)具有高擊穿電壓、高輸入阻抗、高開關速度以及便于集成等優點.絕緣體上硅(silicon on insulator, SOI)技術則具有全介質隔離和低寄生等優勢,可以在功率集成電路(power integrated circuit, PIC)中實現功率器件和邏輯電路之間的有效電學隔離.因此,高壓SOI-pLDMOS已廣泛應用于新一代平板顯示驅動芯片、浮柵驅動芯片、電源管理芯片及音頻功放芯片中[1].

如何在滿足耐壓的基礎上降低器件的導通電阻,實現耐壓和導通電阻的最佳折中是高壓器件設計領域的研究熱點[2-4].通過求解二維泊松方程,獲得器件表面電場分布與器件設計參數的關系,能很好地幫助設計者根據應用背景設計出最合適的器件.雖然對帶有場板的高壓器件解析模型已有一定的研究[5-7],但目前報道的建模方法中都還沒有考慮到場板的邊緣效應對器件表面電場的影響.場板的邊緣效應不僅會影響其正下方區域的電場,還會對相鄰區域的電場有調節作用.因此沒有考慮場板邊緣效應的模型所得出的表面電場與實際表面電場會產生較大的誤差,影響模型的精確性.

本文在充分考慮場板邊緣效應的基礎上,建立了精確的SOI-pLDMOS器件表面電場的解析模型.通過Tsuprem-4和Medici數值仿真發現,考慮場板邊緣效應后的模型更符合器件的實際情況.此外,本文還基于該模型分析了漂移區摻雜濃度和柵極場板長度對器件表面電場的影響,進而設計了一個擊穿電壓高于200 V的SOI-pLDMOS器件.流片測試結果顯示該建模方法準確有效,能有效指導器件的優化設計.

1 二維解析模型

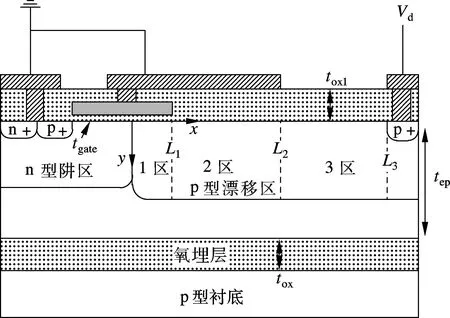

本文所要研究的SOI-pLDMOS器件結構如圖1所示.傳統二維解析模型求解方法中對器件的分區方法如圖1所示[8],各區域滿足的泊松方程及邊界條件為

(1)

(2)

(3)

(4)

i=2,3

(6)

φi-1(Li-1,0)=φi(Li-1,0)i=2,3

(7)

圖1 SOI-pLDMOS剖面結構圖

(8)

式中,Pdrf為器件p型漂移區的摻雜濃度;tox為氧埋層的厚度;tep為外延層厚度;tox1為器件上表面氧化層厚度;tgate為柵氧化層的厚度;εsi為硅的相對介電常數;εox為氧化層的相對介電常數;L1,L2分別為多晶硅場板和金屬場板長度;L3為漂移區長度.

關態條件下,器件的柵極和源極接地,漏極接負電壓Vd.將邊界條件式(2)~(8)代入式(1),可以求得關態條件下器件的表面電場[9-10],即

i=1,2,3

(9)

式中,Vi為器件在區域分界處的電勢,i=1,2,3;V0=0,L0=0,V3=Vd.

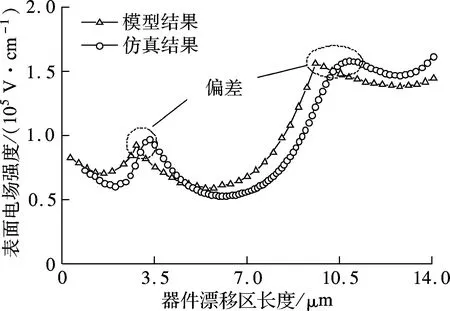

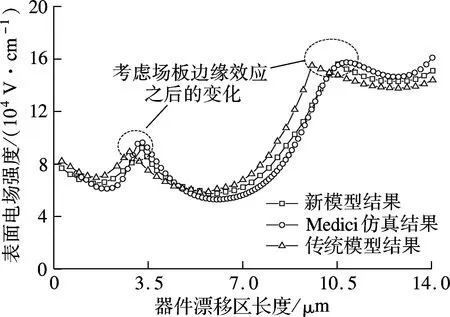

本文所研究的SOI-pLDMOS器件的結構參數為:Pdrf=2×1015cm-3,tep=7 μm,tgate=0.4 μm,tox1=1.4 μm,tox=1 μm,L1=3 μm,L2=9.5 μm,Vd=-170 V.在上述條件下,由式(9)得到的模型計算結果與Medici數值仿真結果見圖2.由圖可見,傳統解析模型得到的表面電場與仿真結果在多晶硅場板末端和金屬場板末端存在偏差.這是因為場板具有邊緣效應,場板不僅會影響圖1中區域1和2的場板正下方的電場,還會對區域2和區域3中靠近場板末端區域的電場有調節作用,而傳統的分區方法會忽略這一影響.

圖2 SOI-pLDMOS表面電場分布

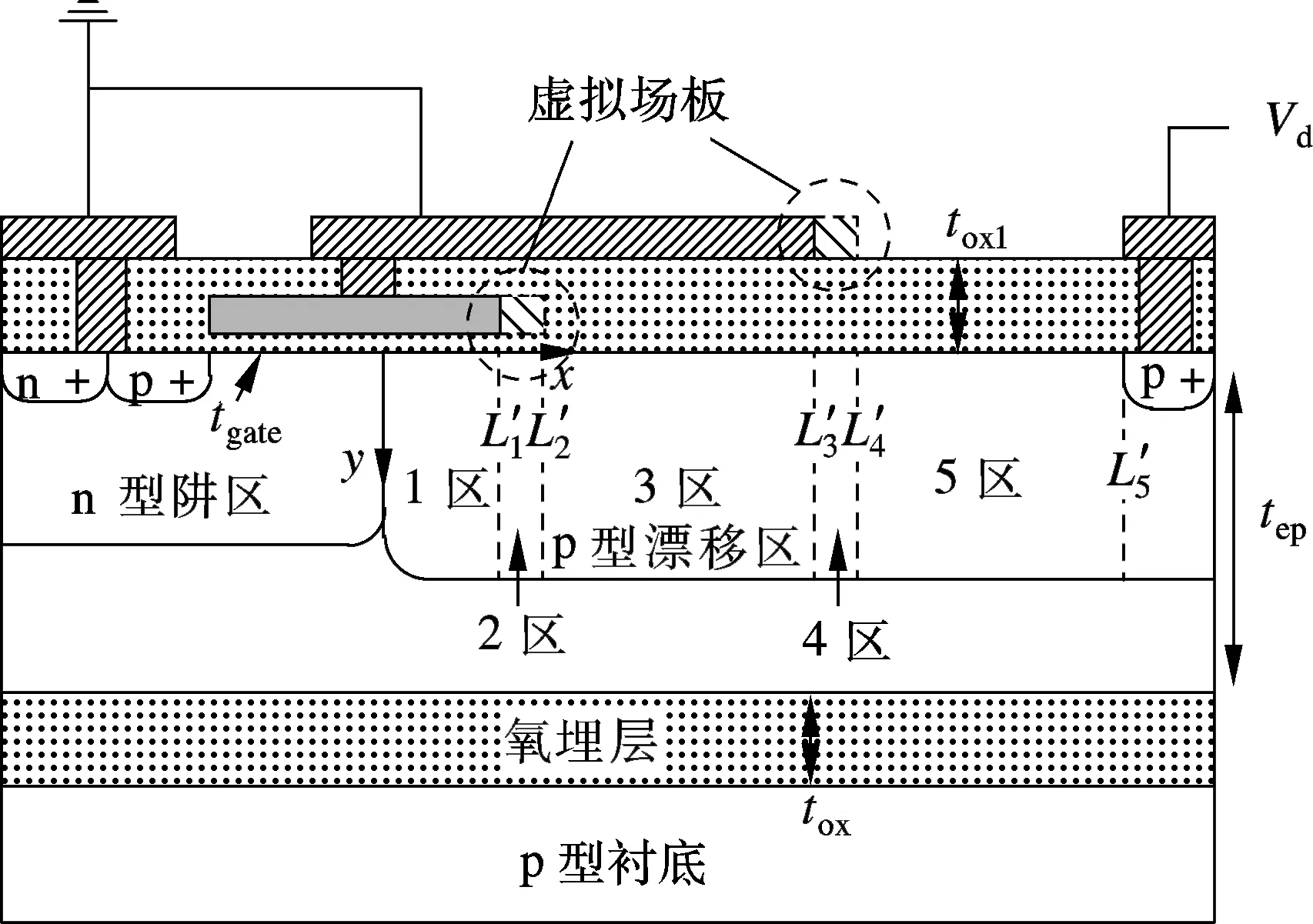

本文所建立的新模型如圖3所示,將SOI-pLDMOS分成5個部分,原有區域1,2,3變為區域1,3,5,相比于傳統模型,本文增加了區域2和區域4以考慮場板的邊緣效應.各區域的泊松方程及邊界條件為

(10)

(11)

(12)

(13)

(14)

(15)

(16)

(18)

圖3 SOI-pLDMOS剖面結構圖

在模型中,認為場板末端相鄰區域內電勢為線性遞增變化,所以在區域2和區域4中增加了虛擬場板以模擬場板邊緣效應對場板末端相鄰區域內電場所造成的影響.對此,采用下式來描述虛擬場板各處的電勢:

(19)

式中,Ldrf為器件漂移區的長度;hi為場板下方氧化層的厚度.

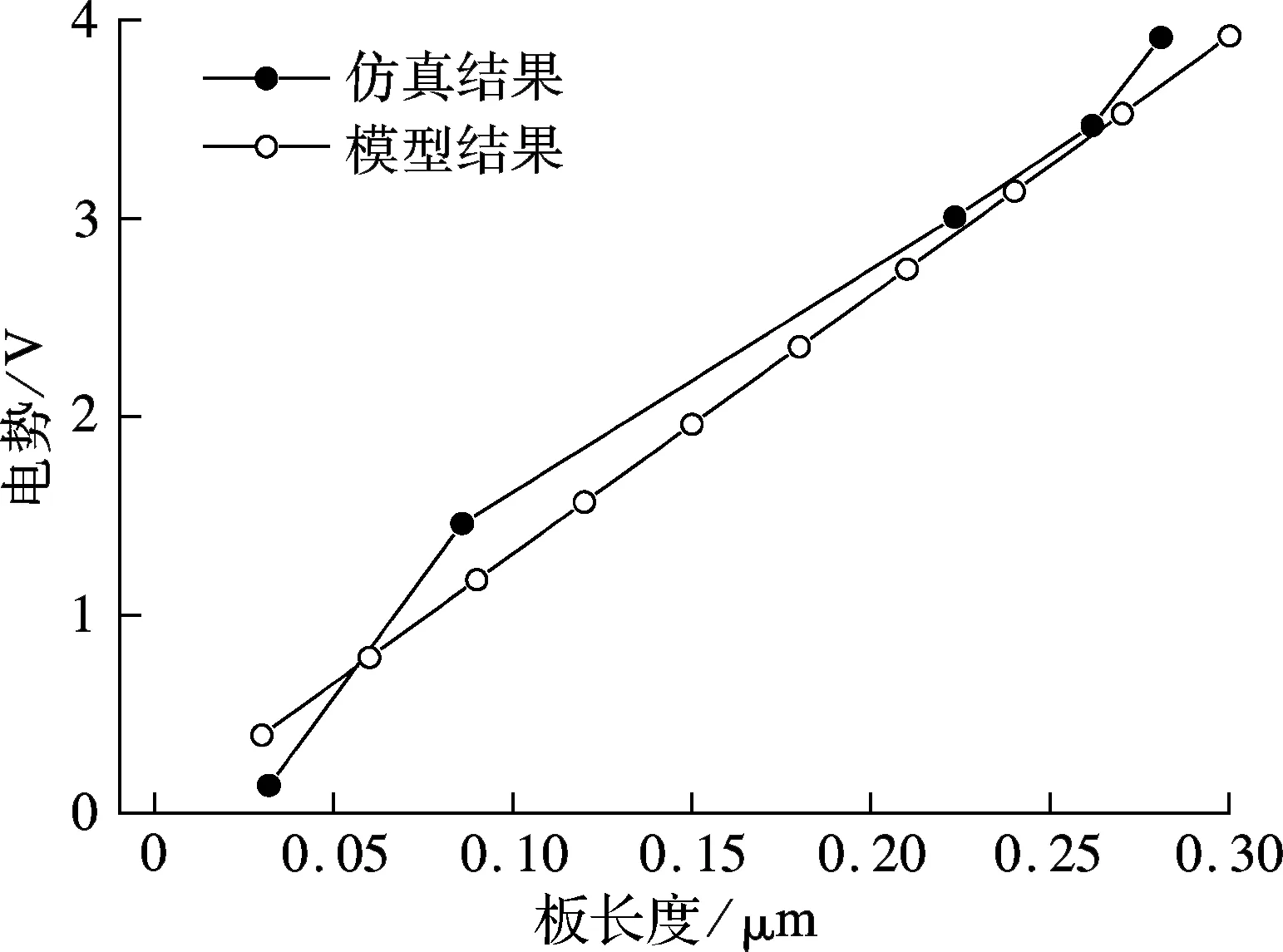

圖4顯示了區域2和區域4中虛擬場板下表面氧化層中電勢的模型計算結果和Medici數值仿真結果.由圖可見,仿真得到的虛擬場板下表面氧化層中的電勢呈線性分布,且和模型結果能夠較好地吻合.

(a) 多晶硅虛擬場板

(b) 金屬虛擬場板

將邊界條件式(11)~(18)代入式(10),求得新模型器件表面的電場解析式為

i=1,2,…,5

(20)

圖5給出了傳統模型、新模型和Medici數值仿真得到的SOI-pLDMOS器件表面電場的分布圖.由圖可見,考慮場板邊緣效應的新模型結果與仿真結果吻合較好,但仍存在較小的差異.導致這些差異的原因是解析模型采用的是平均值代替漂移區摻雜濃度,而實際仿真中漂移區摻雜濃度的分布是非線性的.但這些差異的影響很小,不影響模型的使用.

圖5 新模型SOI-pLDMOS表面電場分布

2 優化與討論

從圖5中也可看出,原目標器件表面電場的分布并不均勻,容易在柵極金屬末端發生提前擊穿.因此,可以利用解析模型研究柵極場板長度和漂移區摻雜濃度等參數對擊穿電壓的影響,從而對器件進行進一步的優化.

2.1 柵極場板的優化

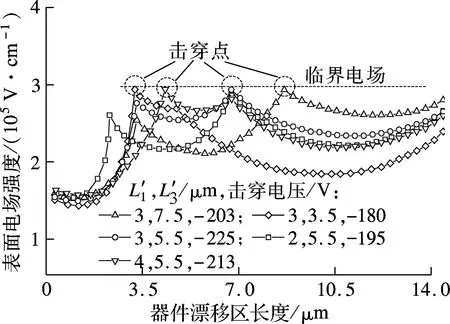

在柵極場板模型中,固定柵極場板的長度,調節Vd使峰值電場達到材料的臨界電場(3×105V/cm),此時的Vd即為器件的擊穿電壓.圖6為不

圖6 不同場板長度下器件表面電場分布

同柵極場板長度下的表面電場分布及其擊穿電壓變化.由圖可見,隨著金屬場板長度的減小,多晶硅場板產生的峰值隨之增加.這是因為金屬場板長度過短,末端靠近多晶硅場板,多晶硅場板與金屬場板末端產生的電勢線集中在較小的范圍內,使多晶硅場板末端的電場峰值增加.此外,如果多晶硅場板長度增加且末端離金屬場板越近,也會導致電勢線集中在較小的范圍內,使多晶硅場板末端電場峰值增加,影響器件擊穿電壓.

綜合考慮多晶硅場板和金屬場板,當多晶硅場板長度為3 μm,金屬場板長度為5.5 μm時,器件表面電場分布最為均勻,其擊穿電壓也最大,為-225 V.

2.2 漂移區摻雜濃度的優化

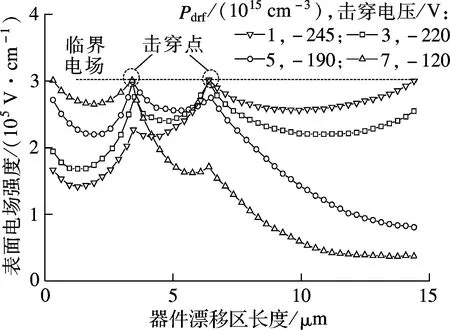

漂移區摻雜濃度是高壓器件設計的另一重要參數.利用本文建立的模型,在最優多晶硅場板和金屬場板的長度下,研究不同漂移區摻雜濃度對器件擊穿電壓的影響.

圖7顯示了在不同漂移區摻雜濃度下器件的表面電場分布.從圖中可以看到,隨著漂移區摻雜濃度的增加,在多晶硅場板末端產生的電場峰值也隨之增加.這是因為多晶硅場板末端離p型漂移區和n阱形成的pn結很近.根據pn結電場公式[11],當摻雜濃度增加時pn結中的電場也增加,這就導致了多晶硅場板末端的電場增加.所以,器件的擊穿電壓下降.為了避免在多晶硅場板末端形成過高的電場峰值,故漂移區的摻雜濃度不能過高.

圖7 不同漂移區摻雜濃度下的表面電場分布

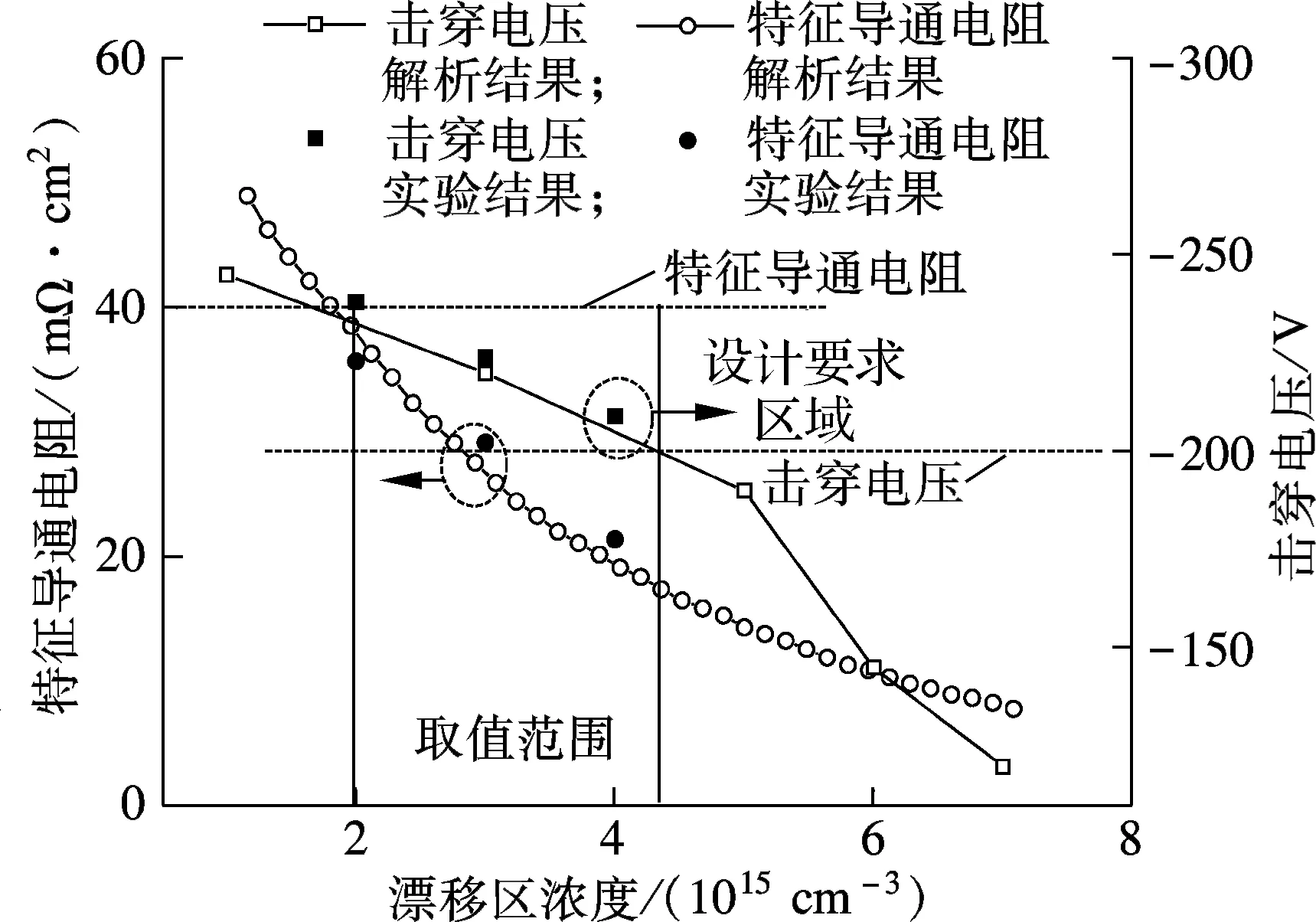

然而,漂移區摻雜濃度不僅影響器件的擊穿電壓,也會影響器件的導通電阻.所以,漂移區摻雜濃度的選取要考慮器件耐壓和導通電阻之間的折中關系.根據本文所建立的模型,并結合已有的導通電阻模型[12]得出了圖8所示的器件擊穿電壓和特征導通電阻隨漂移區摻雜濃度的變化關系.由圖可見,特征導通電阻與摻雜濃度成反比,器件的擊穿電壓隨漂移區濃度的增加而下降,這是因為漂移區摻雜濃度的增加使p型漂移區和n阱形成的pn結中的電場變大,從而使器件的擊穿電壓下降.

圖8 特征導通電阻和擊穿電壓隨漂移區摻雜濃度的變化

考慮到目標電路的應用需求,設計要求器件的特征導通電阻小于40 mΩ·cm2,且擊穿電壓要超過-200 V.在圖8中標出了設計要求所規定的區域,此時漂移區摻雜濃度允許范圍為2×1015~4.2×1015cm-3.圖8中也顯示了實際測試結果,可以看到擊穿電壓的實驗結果與模型預測結果相近,誤差在2.5%以內.考慮到器件耐壓特性和導通電阻的折中關系以及存在的工藝波動,確定最優參數為:漂移區摻雜濃度3×1015cm-3、多晶硅場板長度3 μm、金屬場板長度5.5 μm.

3 結語

本文建立了一個考慮場板邊緣效應的SOI-pLDMOS器件表面電場模型,驗證結果顯示所建立的模型更符合Medici數值仿真結果.此外,應用該模型對200 V SOI pLDMOS的結構參數進行了優化,確定最優參數為:漂移區摻雜濃度3×1015cm-3、多晶硅場板長度3 μm、金屬場板長度5.5 μm,改善了器件的擊穿特性.本文所建立的考慮場板邊緣效應的表面電場模型對高壓器件的設計優化具有一定的指導意義.

References)

[1]萬維俊,劉斯揚,孫虎,等.高柵壓低漏壓條件下FG-pLEDMOS的熱載流子退化機理[J].東南大學學報:自然科學版,2012,42(1):25-28. Wan Weijun, Liu Siyang, Sun Hu, et al. Mechanism of hot-carrier induced degradation in FG-pLEDMOS under high gate voltage low drain voltage stress [J].JournalofSoutheastUniversity:NaturalScienceEdition, 2012, 42(1): 25-28. (in Chinese)

[2]Zhou Kun, Luo Xiaorong, Xu Qing, et al. A RESURF enhanced p-channel trench SOI LDMOS with ultral low specific on-resistance [J].IEEETransactionsonElectronDevices, 2014, 61(7): 2466-2472.

[3]Miyoshi T, Tominari T, Fujiwara H, et al. Design of a reliable p-channel LDMOSFET with RESURF technology [J].IEEETransactionsonElectronDevices, 2014, 61(5): 1451-1456.

[4]鄭維山,孫虎,劉斯揚,等.pLEDMOS導通電阻及閾值電壓的熱載流子退化[J].東南大學學報:自然科學版,2011,41(3):522-525. Zheng Weishan, Sun Hu, Liu Siyang, et al. On-resistance and threshold voltage hot-carrier degradation of pLEDMOS [J].JournalofSoutheastUniversity:NaturalScienceEdition, 2011, 41(3): 522-525. (in Chinese)

[5]Nandi A, Saxena A K, Dasgupta S. Analytical modeling of a double gate MOSFET considering source/drain lateral Gaussian doping profile [J].IEEETransactionsonElectronDevices, 2013, 60(11): 3705-3709.

[6]Coffie R. Analytical field plate model for field effect transistors [J].IEEETransactionsonElectronDevices, 2014, 61(3): 878-883.

[7]Sun Weifeng, Shi Longxing. Analytical models for the surface potential and electrical field distribution of bulk-silicon RESURF devices [J].Solid-StateElectronics, 2004, 48(5): 799-805.

[8]Chung S K, Han S Y. Analytical model for the surface field distribution of SOI RESURF devices [J].IEEETransactionsonElectronDevices, 1998, 45(6): 1374-1376.

[9]Huang Haimeng, Wang Yongwei, Chen Xingbi. An analytical model for SOI triple RESURF devices [C]//IEEE9thInternationalConferenceonASIC. Xiamen, China, 2011: 547-550.

[10]李琦,張波,李肇基.帶p埋層表面注入硅基LDMOS模型與優化[J].半導體學報,2007,28(8):1267-1271. Li Qi, Zhang Bo, Li Zhaoji. Analytical model and optimization of bulk-silicon surface implanted LDMOS with p buried layer [J].JournalofSemiconductors, 2007, 28(8): 1267-1271. (in Chinese)

[11]Kozlov A V, Cheremisinov A A, Polomoshnov S A, et al. Model of effect of pn-junction magnetic field modulation [C]//InternationalConferenceandSeminarofYoungSpecialistsonMicro/NanotechnologiesandElectronDevices. Erlagol, Russia, 2011: 137-139.

[12]孟堅,高珊,陳軍寧,等.用阱作高阻漂移區的LDMOS導通電阻的解析模型[J].半導體學報,2005,26(10):1983-1988. Meng Jian, Gao Shan, Chen Junning, et al. An analytical model of a LDMOS on-resistance using a well as a high resistance drift region [J].JournalofSemiconductors, 2005, 26(10): 1983-1988. (in Chinese)

Surface electrical field model of SOI-pLDMOS considering edge effect of field plate and optimization design

Ye Ran Zhang Chunwei Liu Siyang Sun Weifeng

(National ASIC System Engineering Technology Research Center, Southeast University, Nanjing 210096, China)

A new surface electrical field analytical model is presented for the p-type lateral double diffusion MOS (metal-oxide-semiconductor) transistor based on silicon on insulator (SOI-pLDMOS) with gate field plate. Compared with the traditional analytical model, the proposed model fully considers the influence of the edge effect of field plate upon the electrical field distribution. The results show that the presented model accords with the Medici simulations better. In addition, based on the new analytical model, the effects of the length of the gate field plate (including the polysilicon field plate and metal field plate) and the concentration of p-drift on electrical field distributions and breakdown characteristics are researched. Also, a SOI-pLDMOS is optimally designed. The test results demonstrate that the new surface electrical field analytical model can guide the design of device parameters and realize the best compromise between the breakdown voltage and on-resistance.

analytical model; surface field; SOI-pLDMOS; edge effect

10.3969/j.issn.1001-0505.2015.02.003

2014-09-16. 作者簡介: 葉然(1991—),男,碩士生;孫偉鋒(聯系人),男,博士,教授,博士生導師,swffrog@seu.edu.cn.

港澳臺科技合作專項資助項目(2014DFH10190)、江蘇省青藍工程資助項目、東南大學研究生科研基金資助項目(YBPY1403).

葉然,張春偉,劉斯揚,等.考慮場板邊緣效應的SOI-pLDMOS表面電場模型及器件優化設計[J].東南大學學報:自然科學版,2015,45(2):214-218.

10.3969/j.issn.1001-0505.2015.02.003

TN432

A

1001-0505(2015)02-0214-05