一種實現合并單元同步采樣的方案

Strategy of Implementing Synchronous Sampling for Merging Unit

范訓沖1 萬方華2 張 洪1

(江南大學機械工程學院1,江蘇 無錫 214122;國網電力科學研究院無錫恒馳電器制造有限公司2,江蘇 無錫 214000)

一種實現合并單元同步采樣的方案

Strategy of Implementing Synchronous Sampling for Merging Unit

范訓沖1萬方華2張洪1

(江南大學機械工程學院1,江蘇 無錫214122;國網電力科學研究院無錫恒馳電器制造有限公司2,江蘇 無錫214000)

摘要:合并單元(MU)是實現對電子互感器信息采集的一個重要部件。為了實現合并單元的同步采樣功能,保護現場設備的安全,根據IEC 61850協議,提出了一種采用FPGA實現同步采樣功能的方案。利用全球定位系統(GPS)和高精度晶振,實現同步信號的產生。由于晶振本身存在誤差,在同步脈沖丟失以后,提出一種誤差消除策略。經過軟件分析和試驗論證,該方案大大提高了合并單元的同步精度。

關鍵詞:合并單元同步采樣誤差消除互感器IEC 61850

Abstract:Merging unit (MU) is an important part for achieving information collection for electronic current transformer (ECT). In order to implement synchronous sampling function of MU, and protect field devices, in accordance with IEC 61850 protocol, the scheme of implementing synchronous sampling function by using FPGA is proposed, and the synchronous signals are generated by adopting global position system (GPS) and high precision crystal oscillation. Due to error exists in crystal oscillator itself, the error elimination strategy is proposed for situation of losing synchronous pulse. The software analysis and test verification show that this scheme largely enhances the synchronization accuracy of MU.

Keywords:Merging unitSynchronous samplingElimination of errorCurrent transformerIEC 61850

0引言

隨著智能化變電站技術的逐步革新,電子式互感器也有了很大的發展。如今,國內外電子式互感器主要是Rogowski空心線圈和精密電容分壓器技術[1]。與傳統的電磁式互感器相比,電子式互感器具有體積小、質量輕、絕緣優良、無飽和、頻帶響應寬、數字化方便等優點[2]。

電子式互感器主要給繼電保護和測控裝置提供電壓和電流信號,其精度影響著系統的運行狀況。根據IEC 60044-8,合并單元的主要功能就是接收電子式互感器的12路電流電壓信號[3]。如果這些信息量不同步采集,會造成測控裝置和電表錯誤,導致繼電保護產生錯誤的動作,所以在設計合并單元時,必須保證信息采集的同步性。

1合并單元的同步

1.1 合并單元同步的精度要求

根據電力系統時鐘同步規范2008,同步精度要求如表1所示,信息采集同步的精度必須低于1 μs。

表1 同步精度要求

1.2 合并單元同步實現方法

實現合并單元同步的方法有很多,現階段主要的幾種同步方法說明如下[4]。

① 插值再采樣同步

根據收到采樣值報文的時刻,間隔層設備推算實際采樣時間,然后采用插值算法計算出同步采樣值。這種方法的優點是實現方式簡單,不需要同步時鐘源和光纖[5]; 缺點是不能實現以太網采樣值傳輸,并且會引入較大的誤差。

② 秒脈沖同步

通過光纖同步網輸出秒脈沖,每秒鐘對設備進行一次同步,消除內部時鐘的走時誤差。這種方法的優點是采樣頻率是不固定的,可以自己確定自己的采樣頻率;其次數據可以通過規定的幀格式進行以太網傳輸,而且沒有插值法帶來的誤差。缺點是會用較多的光纖,當秒脈沖丟失后,會由于晶振的誤差,對系統造成誤差。

③ B碼對時

該方式每秒以 BCD 碼形式輸出一幀含日期段、小時段、分段、秒段的信息。B 碼信號一般有4種形式:RS-232 電平方式、RS- 422 電平方式、TTL 電平方式和調制信號。這種方法的優點是精度高,缺點是實現困難。根據各個方法的優缺點以及現場的情況,本次設計采用秒脈沖同步方法。

1.3 合并單元的同步實現

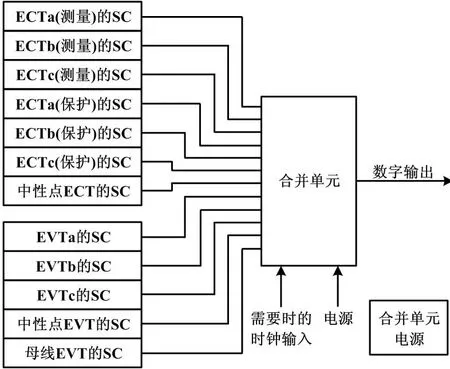

如圖1 所示,合并單元的主要功能是接收7路電流信號和5路電壓信號,將信號進行處理并傳送給保護裝置和測控裝置[6]。

圖1 合并單元定義

合并單元的同步主要實現3個功能:①秒脈沖識別;②產生采樣脈沖;③秒脈沖丟失后的異常處理。

2秒脈沖的識別

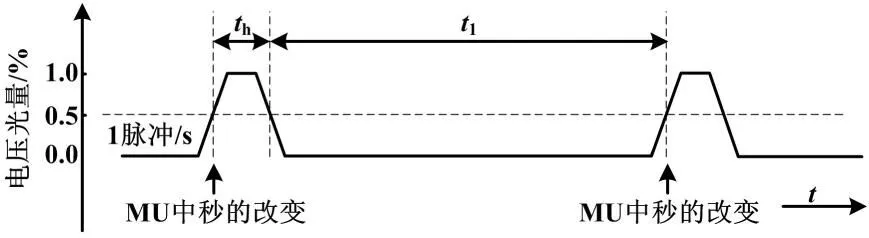

根據IEC 60044-8標準,對秒脈沖要求如下:脈沖高電平持續時間th要達到10 μs 以上,兩個脈沖的間隔t1要大于500 ms,脈沖頻率為1 Hz[7]。輸入波形如圖2所示。

圖2 合并單元同步時鐘輸入波形

現以50 MHz的晶振來說明秒脈沖的識別過程。

① 狀態0:判斷秒脈沖的到來。如果到來,則跳到狀態1,否則跳到狀態0。

② 狀態1:計數器cnt進行計數,在cnt計數到500之前,不斷檢查脈沖是否出現兩個低電平的周期。如果出現,則計數器清零,這個脈沖視為無效脈沖,跳轉到狀態0。如果計數器cnt超過500,則跳到狀態2。

③ 狀態2:判斷脈沖持續時間,cnt繼續計數,當計到 50 000 000±200(200是考慮晶振誤差的存在),再次判斷秒脈沖是否到來。如果到來,則脈沖計數器cnt-pps加1,計數器cnt清0,跳到狀態3;若沒有,則計數器cnt清0,跳到狀態0。

④ 狀態3:判斷cnt-pps的個數。若cnt-pps小于2,則跳到狀態2;如果cnt-pps的個數等于2,則表示出現3個有效脈沖,跳到狀態4。

⑤ 狀態4:計數器cnt繼續計數。當計到50 000 000±200時,判斷下一個秒脈沖是否到來,若在這期間測得到高電平,則pps-right置1,pps-wrong置0,跳到狀態4;若沒有檢測到高電平,則pps-right置0,pps-wrong置1,跳到狀態5。

⑥ 狀態5:等待秒脈沖回復信號pps-s的到來。如果到來,則跳轉狀態4;如果不來,則繼續在狀態5等待。

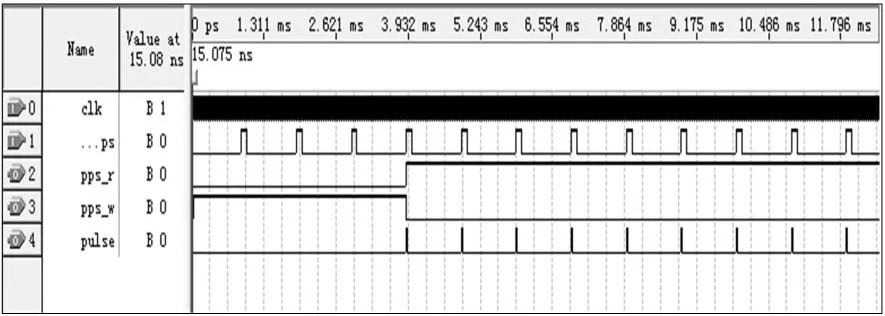

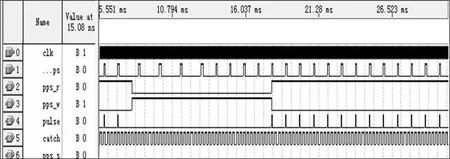

通過QuartusⅡ進行仿真,結果如圖3所示。本次仿真程序設置的秒脈沖信號是1 ms。通過圖3可以看出,在接收到3個正確的秒脈沖信號之后,便可以正確地識別秒脈沖信號。

圖3 正確的秒脈沖信號輸入

3采樣脈沖的產生

在正常情況下,當pps-right為1、pps-wrong為0時,通過采樣模塊來產生同步采樣脈沖。

根據IEC 60044-8[8],系統支持80個點采樣,在這我們選取80個點采樣,采樣頻率為50 Hz,頻率為4 kHz,這樣采樣一次的時間是250 μs,晶振的頻率是50 MHz,我們使用cntct進行計數。當cntct等于12 500(12 500/50 MHz=250 μs)時進行采樣。用另外一個計數器cnt2對采樣的次數進行計數,當采樣次數達到3 999時,判斷pulse的上升沿是否到來,如果到來,則繼續下一次采樣,并且將cntct和cnt2清0;如果沒有到來,則進入異常處理模塊。

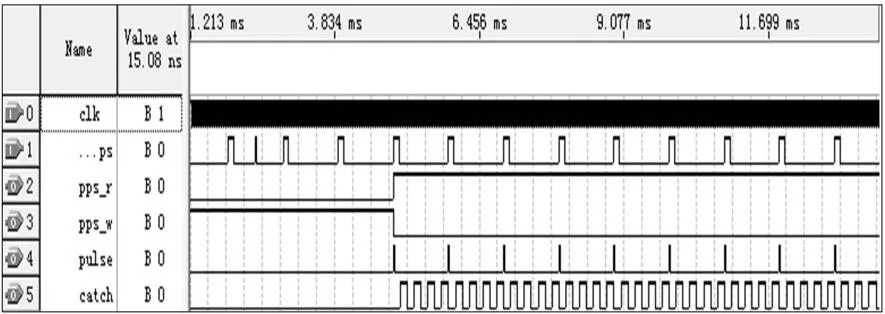

圖4是采樣信號的產生情況。當檢測到正確的秒脈沖之后,系統產生采樣信號catch。從圖4可以看出,系統每毫秒產生4個脈沖。

圖4 采樣脈沖信號的產生

4異常處理模塊

在秒脈沖丟失的情況下,pps-right為0、pps-wrong為1,這時進入異常處理模塊來處理當下的情況。

隨著運行時間的增長,溫度、濕度的變化等因素,晶振的精度會出現一定程度的降低,而晶振的精度是影響同步精度的最關鍵因素[9]。

在正常運行時,由于秒脈沖的存在,1 s強制執行校正;當秒脈沖丟失時,需要通過一定的算法來實現系統的穩定運行。

由于晶振頻率出現誤差,在秒脈沖丟失的情況下,晶振的頻率為50 MHz+ΔC,對于ΔC,傳統的方法是將ΔC集中到最后一次采樣時間。具體實施方法如下:在秒脈沖到來之前,記錄晶振的頻率Cn,C=(C1+C2+……+Cn)/n;當秒脈沖丟失時,ΔC=C-50 MHz,最后第一次采樣為12 500+ΔC。這種方法存在一個誤差的累積,時間一久,將無法實現同步。本文提出一種誤差均衡策略,將ΔC平均分配到ΔC個采樣周期上,所以ΔC個采樣周期的時鐘個數為12 501,而4 000-ΔC個采樣周期為12 500。

ΔC個脈沖的理論時間值為:

(1)

ΔC個脈沖的實際時間值為:

(2)

誤差為:

δ=T-t

(3)

假設ΔC為100,則誤差為1.9 μs。這樣仍不符合要求,需要再次分組。我們繼續進行8組分樣,將ΔC分到8個時間段,則8個時間段的理論時間值為:

(4)

實際時間值:

(5)

當ΔC為100時,δi=Ti-ti,可算出δi=0.24μs,符合要求。

異常秒脈沖處理如圖5所示。

圖5 異常秒脈沖處理

通過圖5可以看出,當秒脈沖丟失以后,系統立即作出反應,能夠很好地產生采樣脈沖,保證系統的正常運行。

5結束語

合并單元是接收互感器信號的重要元件, 實現合并單元同步采樣可以很好地保證系統的正常運行。本文從PPS信號接收,到采樣信號的產生,再到異常情況的處理,提出了基于FPGA的解決策略方案。經試驗論證,該方案能很好地實現合并單元的同步采樣。

參考文獻

[1] 黃益莊.智能變電站自動化系統原理與應用設計[M].北京:中國電力出版社,2011.

[2] 陽靖,周有慶,劉琨.電子式互感器相位補償方法研究 [J].電力自動化設備,2007,27(3):45-48.

[3] 丁書文.綜合自動化原理及應用[M].北京:中國電力出版社,2010.

[4] 趙應兵,周水兵,馬朝陽.基于IEC61850-9-2的電子式互感器合并單元的研制 [J].電力系統保護與控制,2010,38(6):104-106.

[5] 晏玲,李偉,曹津平.采用 FPGA 實現合并單元同步采樣的方案[J]. 電力自動化設備,2010,30(10):126-128.

[6] 賀敬凱 Verilog HDL數字設計實訓教程[M].西安:西安電子科技大學出版社,2012.

[7] 吳仕平,丁網林,闕連元.基于 IEC61850 標準的電子式互感器接口同步的解決方案[C]∥電力系統及其自動化專業第二十三屆學術年會,2007.

[8] 夏梁,梅軍,鄭建勇.基于IEC61850-9-2的電子式互感器合并單元設計[J] .電力自動化設備,2011,31(11):135-138.

[9] 竇曉波.基于IEC61850的新型數字化變電站通信網絡的研究與實踐 [D].南京:東南大學電氣工程學院,2006.

中圖分類號:TP29;TM76

文獻標志碼:A

DOI:10.16086/j.cnki.issn1000-0380.201507027

修改稿收到日期:2014-12-30.

第一作者范訓沖(1989-),男,現為江南大學機械工程專業在讀碩士研究生;主要從事氣體絕緣組合電器的研究。