CAN總線檢測系統的多接口設計研究*

李 平,魏長寶(黃淮學院信息工程學院,河南駐馬店463000)

?

CAN總線檢測系統的多接口設計研究*

李平*,魏長寶

(黃淮學院信息工程學院,河南駐馬店463000)

摘要:為使CAN總線網絡通信更加便捷,提高CAN總線設備檢測效率,基于ARM和FPGA設計了一種CAN總線檢測系統。設計硬件電路時采用了功能模塊化方法,對ARM模塊、FPGA模塊和CAN總線接口電路分別進行設計。在FPGA內部采用了自頂向下的方法進行邏輯設計。在設計中針對多接口集成問題,采用ARM微控制器設計了USB和以太網兩種接口,兩個接口可獨立工作并完成數據交互。完成設計后,進行了仿真驗證和硬件調試,結果表明該系統可有效實現CAN總線數據的檢測及測試。關鍵詞:CAN總線;檢測系統;多接口;模塊化方法

CAN總線即控制器局域網,是德國Bosch公司開發的一種串行數據通信總線,目前已逐步發展成為國際上應用最常用的現場總線之一[1]。CAN總線具有實時性好、可靠性好、成本低以及易開發等優點,現在已廣泛應用到各個領域,如:工廠自動化、汽車電子、電力通訊、鐵路交通等[2-3]。由于CAN總線系統在開發以及使用過程中難免出現異常干擾或設計不周,很可能使總線系統不能正常工作。為了加速總線通信故障的定位和排除,本文致力于設計一種CAN總線檢測系統。

目前,USB已成為計算機上的標準接口,具有連接靈活、傳輸速度快、提供電源和低成本等特點[3],受到設計者的廣泛關注。同時,以太網具有應用成熟、價格低廉等特點。如果能將嵌入式系統與多接口技術相結合,則不僅可以降低設備研制成本、提高設備的通用性,而且可以簡化總線設備研制和生產中的配套檢測設備。

根據CAN總線通信的要求,本文選用了集成USB、以太網和CAN控制器的的ARM微控制器LPC1768。并利用FPGA較強的復雜時序信號邏輯處理功能[4],實現ARM與CAN控制器的接口時序譯碼部分。通過該實現方法解決了CAN總線通信過程中多路復用總線和非多路復用總線之間的轉換與匹配問題,設計了多接口CAN總線檢測系統。

1 CAN總線概述

CAN總線是目前唯一有國際標準(ISO11898)的現場總線,與傳統的現場工業總線RS-485相比,在總線利用率、通信速率和網絡特性等方面具有明顯優勢[5]。

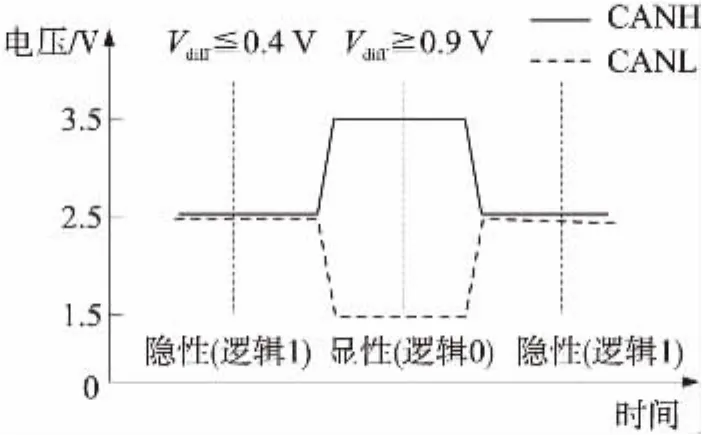

CAN總線收發器和總線之間有兩個接口引腳:CANH、CANL,信號是以兩線之間的“差分”電壓形式出現[6]。圖1為雙絞線傳輸介質下的CAN總線電平標稱值。差分信號對外部電磁干擾(EMI)具有高度免疫,同時無需依賴地的穩定性。

圖1 雙絞線傳輸下的CAN總線電平標稱值

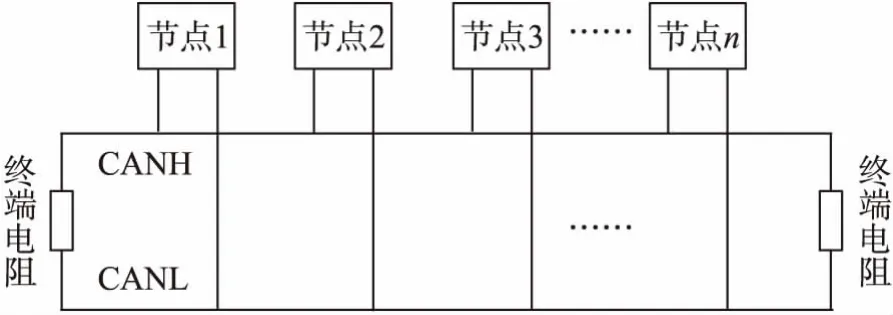

CAN總線為多主方式工作,網絡上任一節點均可在任意時刻主動地向網絡上的其他節點發送信息。多主方式網絡結構可靠性高,節點控制靈活,容易實現多播和廣播功能。網絡節點數主要取決于總線驅動電路,目前可達110個,總線結構如圖2所示。

圖2 CAN總線的多主網絡結構

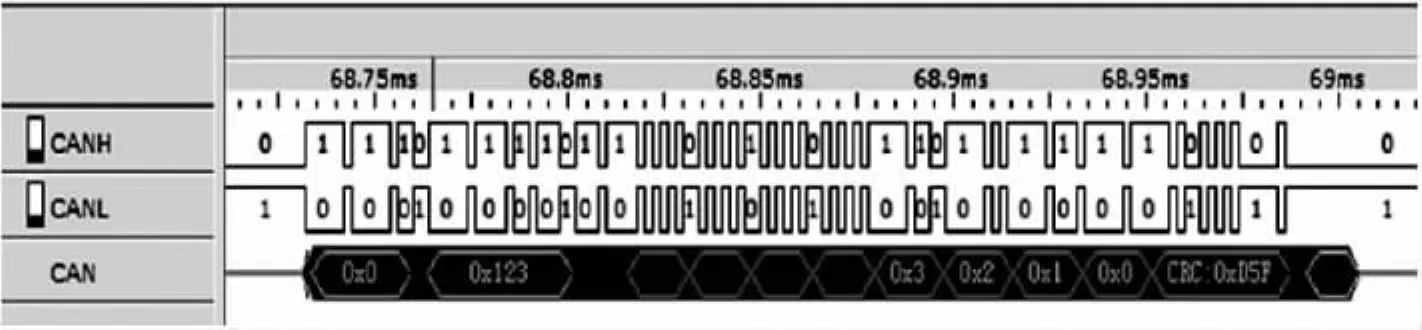

CAN總線上信息以幾個不同的固定格式的報文發送。幀格式的4種類型分別為數據幀、遠程幀、錯誤幀、過載幀。邏輯分析儀截取的CAN總線波形如圖3所示。

圖3 CAN總線波形

2 硬件設計

2.1總體設計

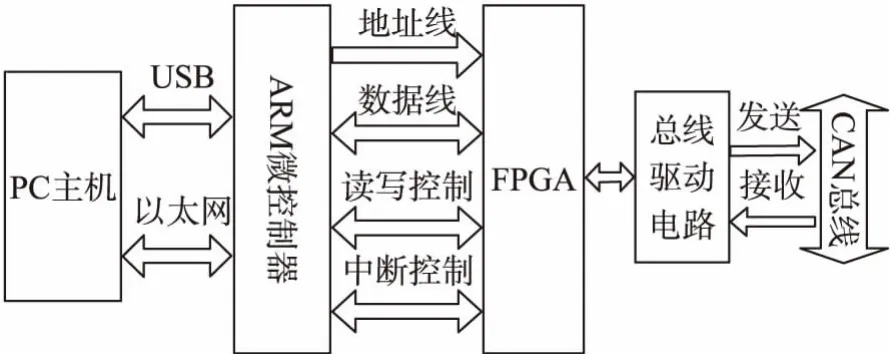

本文研究目標為設計一種針對CAN總線設備的實時檢測系統,可檢測使用CAN總線進行通信的各種設備,方便實際應用中總線設備的檢測和維護。采用ARM微控制器、可編程邏輯器件FPGA以及相應的接口驅動電路。具體實現框圖如圖4所示。

圖4 多接口總線設備檢測系統設計圖

由于ARM微控制器集成了以太網MAC、USB接口,所以在接口設計方面采用了雙接口模式,且兩個接口均可獨立工作并完成與主機的數據交互。因此,不再使用單獨的USB協議芯片與以太網控制芯片。ARM微控制器通過兩種接口與計算機直接通信,并控制著接口的配置和操作。可編程邏輯器件FPGA實現了CAN總線協議處理模塊所要實現的邏輯功能,即CAN總線協議,完成了對CAN總線數據的轉換和處理。可編程邏輯器件只需通過總線驅動電路便可與總線設備進行數據通信。該設計方案簡化了設計程序,充分利用了芯片資源,很大程度上節省了成本。

本文所選用的LPC1768是基于ARM Cortex-M3內核的32 bit微控制器,最高工作頻率為100 MHz,每個器件最高集成了512 kbyte閃存和64 kbyte SRAM[6]。作為主控芯片,LPC1768對整個系統的所有模塊進行有效控制,不僅完成信息的處理、傳輸和存儲,還要根據需要完成對兩個接口控制功能。

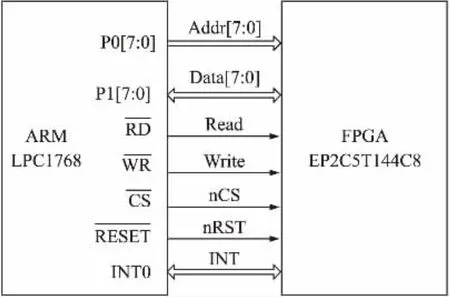

ARM處理模塊主要負責整個系統的控制和管理以及總線設備與上位機的通信。本設計將ARM 與FPGA相結合,充分利用ARM微控制器強大的芯片資源實現系統數據交互。FPGA與ARM連接模塊實現內部控制和數據交換,需要連接地址線、數據線和控制線。

圖5 ARM與FPGA處理模塊連接圖

2.2USB總線接口電路

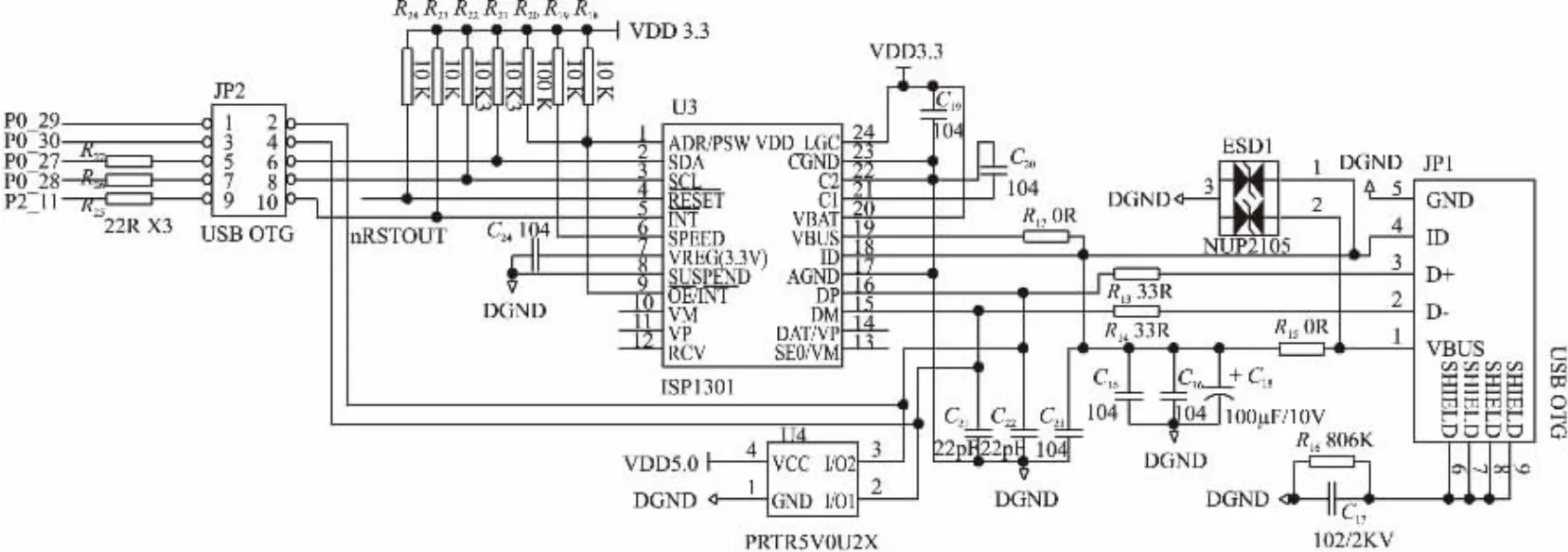

LPC1768具有3級流水線和哈佛結構,采用矩陣式AHB總線,可同時管理以太網、USB等高寬帶外設而不影響性能[7]。本文充分利用LPC1768芯片資源,考慮到內置有USB2.0全速/主機/OTG控制器,另外還配有片上物理層接口,所以不再使用USB專用協議芯片。芯片的以太網模塊(EMAC)包含一個功能齊全的10 Mbit/s和100 Mbit/s的MAC,所以也不必使用專用網絡控制芯片,只需配置一片PHY芯片即可。LPC1768內部集成了嵌入式USB OTG控制器,利用該OTG控制器可以和具有USB控制器的嵌入式設備進行點對點通信。USB總線接口電路如圖6所示。

圖6 USB總線接口電路圖

只需配置一片收發器即可實現數據收發。USB OTG收發器采用ISP1301芯片,它完全遵循USB2.0的補充規范:USB OTG V1.0a,可在全速(12 Mbit/s)和低速(1.5 Mbit/s)速率下收發串行數據。

2.3以太網接口電路

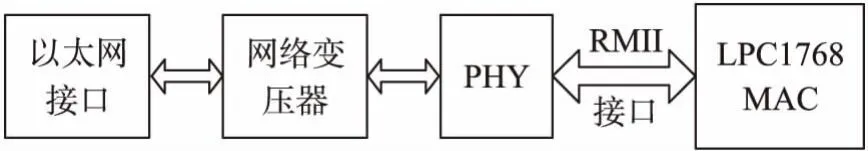

以太網控制器由以太網媒體接入控制器(MAC)和物理接口收發器(PHY)組成。網絡接口電路設計框圖如圖7所示。

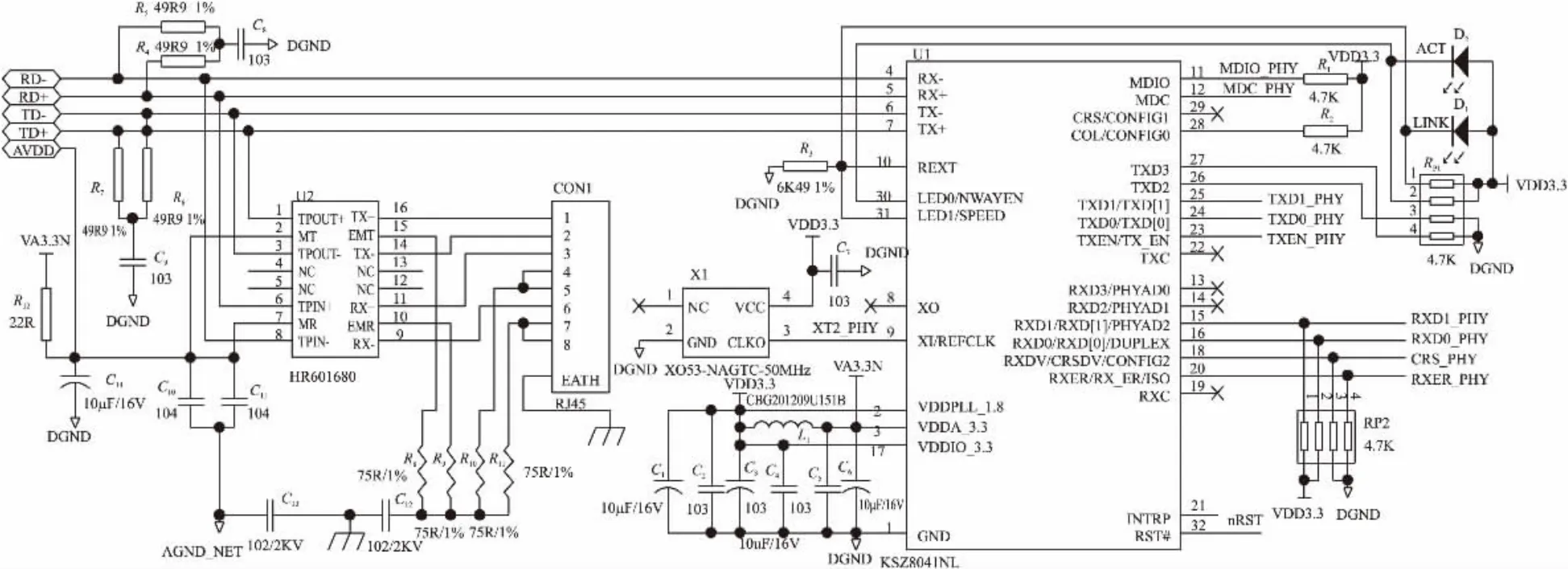

MAC與PHY通訊采用媒體獨立接口(MII)或者RMII接口(簡化的MII)。LPC1768微控制器可以通過RMII與PHY組成一個完整的以太網控制器,再經過網絡變壓器與以太網接口連接。以太網接口電路原理圖如圖8所示。

圖7 網絡接口電路框圖

圖8 以太網接口電路原理圖

PHY芯片選用的是KSZ8041NL芯片,其內核可在1.8 V下進行操作以符合低壓和低功率的要求,可用單電源3.3V供電。它使用MII接口或者RMII接口與10BASE-T/100BASE-TX物理層收發器進行數據交換,其獨有的混合信號設計不但可以擴大發送信號的距離,而且還可以降低功耗。網絡變壓器選擇了單口以太網網絡變壓器HR601680。

3 CAN總線檢測系統功能

CAN總線檢測系統支持兩個不同的自測試模式:全局自測試(在正常操作模式下設置自接收請求位)和局部自測試(在自測試模式下設置自接收請求位)[8]。

兩種自測試都在使用CAN控制器的“自接收”特性。使用自接收請求時,發送的報文也會被接收并存放到接收緩沖器中。因此,驗收濾波器必須進行相應的配置。CAN報文一旦發送出去,就會產生發送中斷和接收中斷(如果中斷被使能的話)。

(1)全局自測試

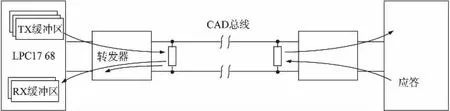

全局自測試可以用來檢驗在一個給定的CAN系統中所選的CAN控制器配置。如圖9所示,至少還要有另一個正在應答每個CAN報文的CAN節點連接到CAN總線上。

圖9 CAN總線全局自測試

啟動一次全局自測試與啟動一次正常CAN發送類似。在啟動全局自測試的情況下,CAN報文的發送是通過置位自接收請求位(SRR)和CAN控制器命令寄存器(CANCMR)中的報文緩沖位(STB3、STB2和STB1)來啟動的。

(2)局部自測試

局部自測試非常適用于單個節點測試。在這種自測試下,不需要其他節點的答應。如圖10所示,帶有適合CAN總線終端的CAN轉發器必須連接到LPC1768微控制器。CAN控制器必須通過置位元CAN控制器模式寄存器(CANMOD)中的STM位來進入“自測試模式”。

報文發送是通過置位自接收位(SRR)和選中的報文緩沖器(STB3、STB2和STB1)來啟動。

4 實驗結果

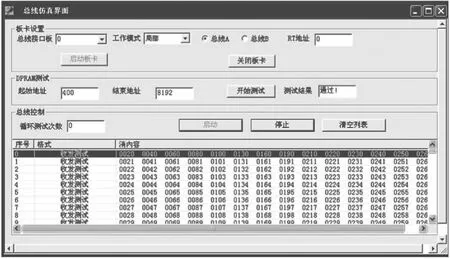

在設計完成后,需對檢測系統的功能進行測試,主要是測試CAN節點功能。同時利用CAN總線仿真界面控制和管理總線上的數據傳輸,CAN總線發送和接收仿真界面如圖11所示。

圖11 發送通道仿真界面

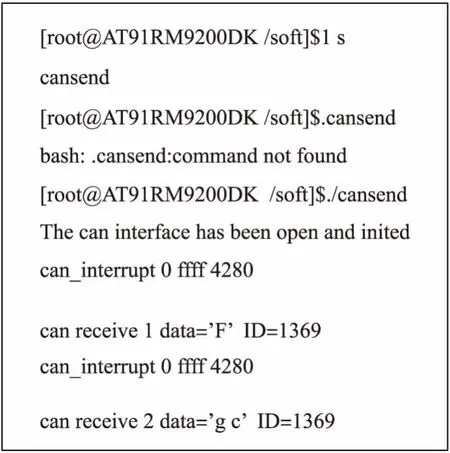

圖12 轉換卡CAN節點接收圖

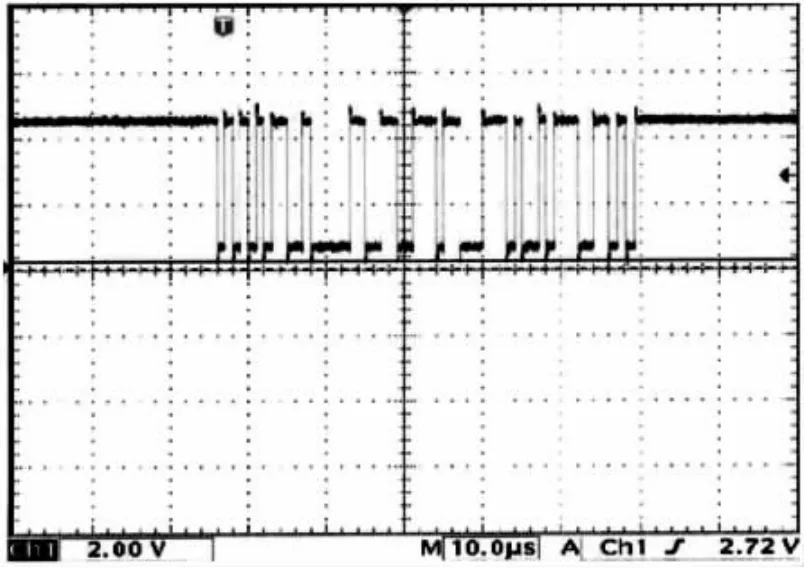

檢測系統CAN節點接入到CAN總線設備中,設定其ID為0x355,通過一個節點ID為1369的節點給它發送信息幀,通過在LPC1768中運行的接收程序可以看到其接收情況如圖12所示,可以看出通過兩次中斷后接收到了兩個不同的數據段,且測試結果和所發送數據一致,看見檢測系統的CAN節點具有接收數據的功能。接著觀察其發送數據的功能,把示波器的探頭接在發送引腳上,然后通過發送程序發送數據,可以在示波器上看到在發送端口上的波形圖如圖13所示,CAN總線上的節點也收到了相關的數據,由此可見檢測系統的CAN節點可實現數據功能,滿足設計要求。

圖13 CAN節點發送示波器截圖

5 結束語

本文采用ARM+FPGA的方案來設計,這種方案能夠體現出檢測系統的集成化和低成本特性。針對多接口集成問題,采用ARM微控制器集成的雙接口模式來實現,且兩個接口均可獨立工作并完成數據交互。通過軟件仿真和硬件性能測試,結果表明該系統可實現CAN總線數據的有效發送與接收功能,能夠實現CAN總線設備間的多接口數據交互。本系統提高了檢測效率,從成本上和通用性上都有了很大改善。

參考文獻:

[1]楊春杰,王曙光,亢紅波.CAN總線技術[M].北京:北京航空航天大學出版社,2010:5-18.

[2]Road Vehicles.Controller area Network(CAN)-Part2:High-Speed Medium Access Unit,ISO11898[S].International Standardization Organization,2003,20-21.

[3]唐明南,董云峰,牛躍聽.CAN總線在衛星半物理實時仿真中的設計與應用[J].計算機測量與控制,2008,16(1):124-127.

[4]NXP Semiconductors.LPC176x Product Data Sheet[EB/OL].2011.http://www.nxp.com.

[5]王巖,張福恩.基于CAN總線的智能測控節點的設計[J].電子器件,2000,23(4):267-270.

[6]林超凡,黃繼業,方舟.基于CAN總線的高分辨率工業顯示屏控制器[J].電子器件,2012,35(3):361-365.

[7]NXP Semiconductors.LPC178x/7x User Manual[EB/OL].2012.http://www.nxp.com.

[8]CiA Draft Standard 102 Version 2.0 CAN Physical Layer for Industrial Applications[S].CAN in automation Gmhb,1994,4:3-4.

李 平(1976-),女,漢族,河南駐馬店人,碩士,講師,主要研究方向為信息處理現代電子系統等,393423675 @qq.com;

Research of Design Technologies for 8-bit 80 Msample/s Low Power Pipelined ADC*

JU Shuirong1*,LIU Minjie2,ZHU Zhangming3

(1.Jiangsu College of Information Technology,Wuxi Jiangsu 214153,China; 2.Xidian University,Xi’an 710071,China)

Abstract:8-bit,80 Msample/s low power ADC is presented by using seven stage pipelined architecture.To reduce the chip size and power of total ADC,and improve the harmonic distortion and noise property,MDAC in first sub-ADC is considered in focus,thus sampling and holding circuit of total ADC is integrated in MDAC of first sub-ADC,step by step shrinking technology is used,symmetry of capacitors and amplifier in every stage ADC is considered in layout design.The whole ADC was designed in 0.18 μm CMOS process,the SNR of the ADC is 49.5 dB,ENOB is 7.98 bit.The total chip size is only 0.56 mm2,as well as the typical power current is only 22 mA.The performance requirement of the ADC is achieved.

Key words:ADC integrated circuit; design technology; chip size; low power; SNR(Signal-to-Noise Ratio)

doi:EEACC:257010.3969/j.issn.1005-9490.2015.04.041

收稿日期:2014-11-20修改日期:2014-12-19

中圖分類號:TP274

文獻標識碼:A

文章編號:1005-9490(2015)04-0917-05

項目來源:河南省科技廳發展計劃項目(142102110088)