面向三維集成電路版圖設(shè)計(jì)的EDA插件研究*

陳 娟,竺興妹,段倩妮(.南京工程高等職業(yè)學(xué)校電子工程系,南京35; .南京航空航天大學(xué)電子信息工程學(xué)院,南京006)

?

面向三維集成電路版圖設(shè)計(jì)的EDA插件研究*

陳娟1*,竺興妹1,段倩妮2

(1.南京工程高等職業(yè)學(xué)校電子工程系,南京211135; 2.南京航空航天大學(xué)電子信息工程學(xué)院,南京210016)

摘要:為了更好的滿足工程師在三維集成電路設(shè)計(jì)中的需要,基于SKILL語(yǔ)言,對(duì)業(yè)界主流版圖設(shè)計(jì)工具Cadence Virtuoso進(jìn)行二次開發(fā),開發(fā)出能輔助三維集成電路設(shè)計(jì)的EDA插件。該EDA插件主要包括3種功能:自動(dòng)對(duì)齊,自動(dòng)打孔和三維可視化技術(shù)。最終在三維集成電路的背景下設(shè)計(jì)兩個(gè)并聯(lián)的反相器以驗(yàn)證算法功能。實(shí)驗(yàn)表明,該EDA插件能夠滿足三維集成電路設(shè)計(jì)的需求,簡(jiǎn)化三維集成電路版圖設(shè)計(jì)的過程,具有很好的易用性。

關(guān)鍵詞:三維集成電路;插件; SKILL;硅穿孔;版圖設(shè)計(jì)

隨著晶體管加工工藝的不斷進(jìn)步,按比例縮小集成電路的發(fā)展思路已經(jīng)接近極限,面臨的問題有:(1)未來系統(tǒng)需要集成多種非電子元件,如射頻、光/光電、執(zhí)行器、MSMS等; (2)互聯(lián)線延遲對(duì)電路性能影響的比例不斷提升[1]。正是這一系列的嚴(yán)峻挑戰(zhàn)促使了“More Than Moore”定律的發(fā)展與應(yīng)用[2-3]。國(guó)際半導(dǎo)體技術(shù)藍(lán)圖宣稱三維集成電路是達(dá)到更高晶體管集成密度的關(guān)鍵技術(shù)之一[4]。該項(xiàng)技術(shù)可以在芯片面積不變的前提下進(jìn)一步提升芯片的集成度。此外,三維集成電路更注重系統(tǒng)集成和各種工藝的兼容性,這有利于提升微電子系統(tǒng)的性能[5-7]。但是,現(xiàn)階段的EDA軟件如Cadence等僅僅支持三維集成電路版圖的設(shè)計(jì)規(guī)則檢查(DRC)、版圖原理圖檢查(LVS)和版圖仿真,沒有覆蓋整個(gè)三維集成電路設(shè)計(jì)流程,造成了目前工程師設(shè)計(jì)三維集成電路時(shí)過程復(fù)雜,且容易出錯(cuò)[8]。

為了更好的滿足工程師在三維集成電路設(shè)計(jì)中的需要,本文在下面第1部分研究了三維集成電路的物理實(shí)現(xiàn)流程,并在第2部分內(nèi)容中基于現(xiàn)有三維集成電路版圖設(shè)計(jì)流程的問題,構(gòu)建三維集成電路的設(shè)計(jì)流程;第3部分基于SKILL語(yǔ)言[9-11],對(duì)Cadence Virtuoso進(jìn)行二次開發(fā),開發(fā)出能輔助三維集成電路設(shè)計(jì)的EDA插件。第4部分設(shè)計(jì)了一個(gè)設(shè)計(jì)實(shí)例對(duì)算法功能進(jìn)行了驗(yàn)證。

1 三維集成電路的物理實(shí)現(xiàn)流程

三維集成電路被定義為一種系統(tǒng)級(jí)集成結(jié)構(gòu),在這一結(jié)構(gòu)中,多層平面器件被堆疊起來,并經(jīng)由硅穿孔TSV(Through Si Via)在Z方向連接起來[12]。為制造這樣的疊層結(jié)構(gòu),TSV制作、層減薄技術(shù)、對(duì)準(zhǔn)和鍵合技術(shù)是三維集成電路制造的3大關(guān)鍵技術(shù)。

TSV制作:Z軸互連是穿透襯底(硅或者其他半導(dǎo)體材料)的連接,TSV的尺寸取決于TSV的高度,TSV的高度越高,TSV的尺寸越大; TSV可堆棧多片芯片,其設(shè)計(jì)概念來自于印刷電路板,在芯片鉆出小洞(制程又可分為先鉆孔以及后鉆孔兩種),從底部填充入金屬,硅晶圓上以刻蝕或鐳射方式鉆孔,再以導(dǎo)電材料如銅、多晶硅、鎢等物質(zhì)填滿。

層減薄技術(shù):初步應(yīng)用需減薄到大約75 μm~50 μm,而在將來需減薄到約25 μm~1 μm。

對(duì)準(zhǔn)和鍵合技術(shù):芯片與晶圓(D2W)之間,或者晶圓與晶圓(W2W)之間,將TSV對(duì)準(zhǔn)并鍵合。

基于上述關(guān)鍵技術(shù),三維集成電路的物理實(shí)現(xiàn)流程根據(jù)鉆孔的次序,分為先鉆孔流程和后鉆孔流程。

先鉆孔流程包括如下步驟:

(1)基于光刻,摻雜和刻蝕工藝實(shí)現(xiàn)第1層集成電路的晶體管及其相應(yīng)金屬層。

(2)生長(zhǎng)第2層集成電路的襯底。

(3)通過TSV制作工藝,生成第1層和第2層集成電路之間的TSV。

(4)再基于光刻,摻雜和刻蝕工藝生長(zhǎng)第2層集成電路的晶體管及其相應(yīng)金屬層。

由于工藝水平的限制,上述流程中的第2步驟并不成熟,因此先鉆孔流程的三維集成電路良片率較低。目前三維集成電路的物理實(shí)現(xiàn)主要依賴第2種后鉆孔流程,其流程包括如下步驟:

(1)基于光刻,摻雜和刻蝕工藝分別實(shí)現(xiàn)第1層和第2層集成電路的晶體管及其相應(yīng)金屬層。

(2)基于層減薄技術(shù)減薄第2層集成電路的襯底。

(3)通過TSV制作工藝,生成第1層和第2層集成電路之間的TSV。

(4)對(duì)第2層集成電路中的TSV上方進(jìn)行淀積絕緣層。

2 三維集成電路(IC)版圖設(shè)計(jì)流程

2.1三維IC版圖特點(diǎn)

由第2章介紹可知,三維集成電路可以視作由若干層二維集成電路組成,這些二維集成電路在Z軸方向上通過TSV工藝進(jìn)行連接。因此三維集成電路的版圖可以視為若干個(gè)二維集成電路版圖的集合。值得指出的是,三維集成電路中的多層二維集成電路彼此之間存在電氣連接關(guān)系;即使沒有電氣連接,也會(huì)因?yàn)楸舜伺R近,會(huì)對(duì)相鄰的電路性能產(chǎn)生影響。因此,三維集成電路的版圖設(shè)計(jì)過程相對(duì)于二維集成電路版圖設(shè)計(jì)過程,會(huì)更加復(fù)雜。

2.2現(xiàn)有三維IC版圖設(shè)計(jì)流程的問題

由于三維集成電路中的多層二維集成電路彼此之間存在電氣連接關(guān)系,因此在二維集成電路設(shè)計(jì)EDA工具Cadence Virtuoso中實(shí)現(xiàn)上述步驟,主要存在的問題有:

(1)三維集成電路版圖中,各層之間的相對(duì)位置必須非常精確,絲毫不差。

(2)各層集成電路對(duì)相鄰層的電路會(huì)有性能影響,因此在布局時(shí)需要考慮彼此的位置和方向。

(3)三維集成電路設(shè)計(jì)中,各層之間需要增加TSV過孔。而各層電路存放于不同的CellView中,對(duì)于一個(gè)TSV,需要手動(dòng)分別在兩個(gè)不同CellView中增加TSV,且要保證TSV的位置嚴(yán)格對(duì)應(yīng)。

2.3本文提出的三維IC版圖設(shè)計(jì)流程

為了解決上述問題,本文結(jié)合二維集成電路設(shè)計(jì)流程,提出一種適合三維集成電路的版圖設(shè)計(jì)過程。其設(shè)計(jì)過程包括如下步驟:

(1)實(shí)現(xiàn)基本單元版圖。新建不同的CellView文件,實(shí)現(xiàn)版圖所需的基本單元版圖。

(2)布局。通過調(diào)用單元電路,根據(jù)設(shè)計(jì)需求,使這些單元分布在三維集成電路版圖中。在布局過程中,往往需要綜合考慮上下層電路彼此之間的關(guān)系。

(3)布線。通過對(duì)這些單元進(jìn)行連線,對(duì)于不同層的金屬連線還需要增加TSV,使其成為一個(gè)完整的三維集成電路的版圖。在布線過程中,需要在相連的兩層版圖中都要打上TSV,并且兩者位置需要完全吻合對(duì)應(yīng)。

3 本文提出的三維IC版圖插件設(shè)計(jì)

在2.3節(jié)所述的三維集成電路設(shè)計(jì)流程中,步驟(1)內(nèi)容是和二維集成電路版圖設(shè)計(jì)內(nèi)容完全一致。但是步驟2和步驟3的內(nèi)容是三維集成電路版圖設(shè)計(jì)中特有的。為了方便設(shè)計(jì)者在步驟2和步驟3中的版圖設(shè)計(jì),本文提出一種EDA插件。該插件包括3種功能:自動(dòng)對(duì)齊,自動(dòng)打孔和三維可視化。

以在三維集成電路工藝環(huán)境下設(shè)計(jì)兩個(gè)并聯(lián)的反相器為例,其步驟主要有如下3步。

(1)在兩個(gè)版圖文件上分別畫上兩個(gè)反相器的版圖。

(2)擺放反相器的位置。這期間,可以通過三維可視化觀察各層電路版圖的相對(duì)位置。

(3)在相鄰層之間繪制TSV時(shí),只要在一層中繪制TSV,運(yùn)行自動(dòng)打孔功能后,插件會(huì)在相鄰層對(duì)應(yīng)的位置繪制TSV。

(4)在繪制版圖過程中,若移動(dòng)了其中一層版圖。為使另一層版圖與之依舊對(duì)齊,可以運(yùn)行自動(dòng)對(duì)齊功能的腳本完成移動(dòng)另一層版圖的功能。當(dāng)完成自動(dòng)對(duì)齊功能后,還可以運(yùn)行可視化功能,觀察腳本是否運(yùn)行正確。

3.1自動(dòng)對(duì)齊

自動(dòng)對(duì)齊是當(dāng)三維集成電路版圖中的任意層版圖被移動(dòng)后,運(yùn)行該腳本,相鄰版圖會(huì)對(duì)應(yīng)移動(dòng),使得相鄰版圖的相對(duì)距離不變,以保證相鄰版圖之間的TSV連接正確。

為實(shí)現(xiàn)上述功能,本文提出的自動(dòng)對(duì)齊算法首先在相鄰版圖之間尋找對(duì)應(yīng)點(diǎn),一般取有電氣連接關(guān)系的TSV作為對(duì)應(yīng)點(diǎn);然后通過對(duì)應(yīng)點(diǎn),分別讀取相鄰版圖的位置,計(jì)算相鄰版圖的坐標(biāo)偏移量;最后根據(jù)計(jì)算的坐標(biāo)偏移量,移動(dòng)相鄰版圖實(shí)現(xiàn)對(duì)齊。

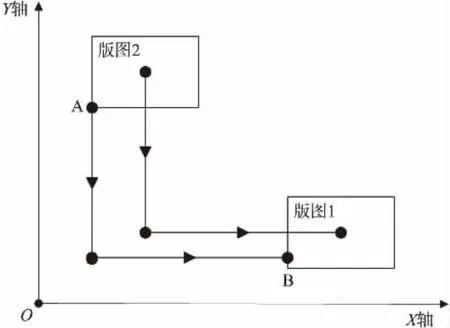

圖1中用兩個(gè)長(zhǎng)方形標(biāo)識(shí)相鄰的版圖1和版圖2。如圖所示,版圖2中內(nèi)部任意點(diǎn)移動(dòng)到版圖1中相應(yīng)點(diǎn)位置,其在X軸方向上的移動(dòng)距離、Y軸上的移動(dòng)距離,與版圖邊框上點(diǎn)移到對(duì)應(yīng)點(diǎn)的移動(dòng)距離是完全一致的。因此,若將版圖2移動(dòng)到版圖1的位置,只需要計(jì)算出相鄰版圖對(duì)應(yīng)點(diǎn)在X軸和Y軸的偏移量。

圖1 自動(dòng)對(duì)齊核心算法說明圖

因此,通過對(duì)對(duì)應(yīng)點(diǎn)的提取可以得到點(diǎn)A的坐標(biāo)(a,b),同樣的可以得到點(diǎn)B的坐標(biāo)(c,d)。

基于式(1)和式(2),可得到移動(dòng)版圖2到版圖1所需的偏移量,然后調(diào)用系統(tǒng)自帶函數(shù)即可移動(dòng)版圖2中的所有圖形。

3.2自動(dòng)打孔

TSV是相鄰層電氣連接的橋梁,若相鄰層的TSV位置錯(cuò)位,則會(huì)對(duì)電路性能帶來致命影響。例如,若相鄰版圖的TSV只有部分對(duì)齊,會(huì)導(dǎo)致TSV的電阻增大。如果兩層版圖的TSV完全分離,這會(huì)導(dǎo)致相鄰版圖沒有電氣連接關(guān)系,是完全錯(cuò)誤的打孔。

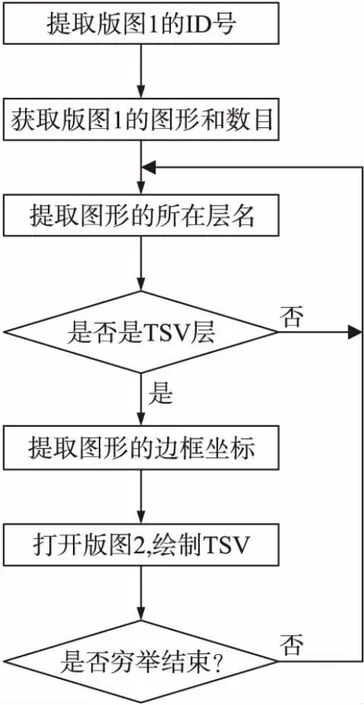

為避免繪錯(cuò)TSV的位置,本文提出自動(dòng)打孔功能。當(dāng)在一層版圖上繪制TSV后,運(yùn)行自動(dòng)打孔功能后,會(huì)在相鄰版圖上繪制對(duì)應(yīng)的TSV版圖,其算法流程如圖2所示。

圖2 自動(dòng)打孔算法流程圖

3.3三維可視化

為了方便對(duì)比相鄰版圖之間的關(guān)系,同時(shí)省去電路設(shè)計(jì)時(shí)的麻煩,本文設(shè)計(jì)了三維可視化功能。設(shè)計(jì)者可以通過該功能在任意層版圖中觀察相鄰版圖的情況。

可延續(xù)的抽象規(guī)則與制度理念組成高校制度文化的第三層面——價(jià)值觀念層,它是在高校的長(zhǎng)期發(fā)展過程中,因?yàn)楦咝H珕T的習(xí)慣、經(jīng)驗(yàn)、知識(shí)積累等自然形成的,是高校精神文化的核心,反映并決定著高校的集體意志與價(jià)值取向。由于這種價(jià)值觀念已形成了相對(duì)穩(wěn)定的影響力且這種影響力具有延伸性和擴(kuò)展性,其便具有了作為“制度”的“強(qiáng)制性”,在一定程度上引導(dǎo)、校正高校物質(zhì)文化和精神文化的價(jià)值變遷。

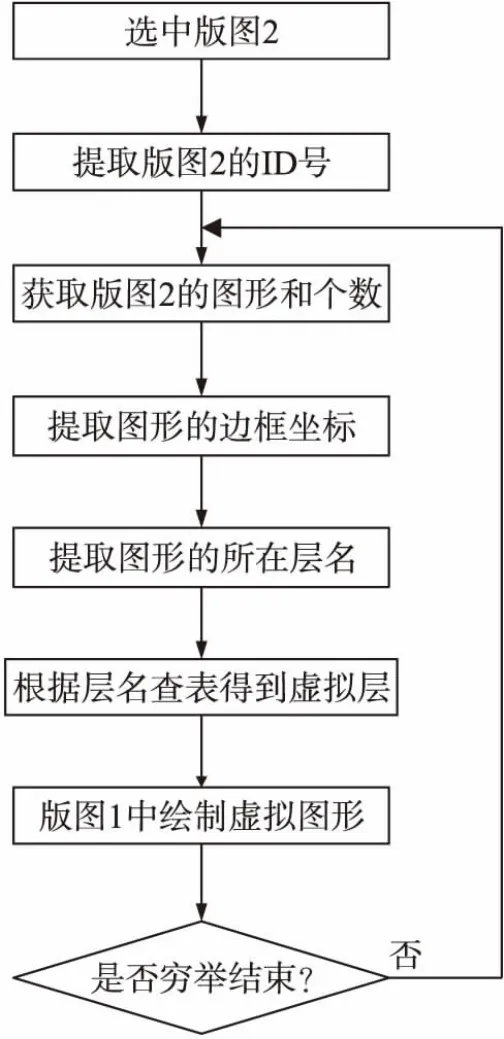

三維可視化由兩個(gè)模塊組成:可視化模塊和刪除虛擬版圖模塊。例如,當(dāng)需要在版圖1中觀察版圖2的相對(duì)位置時(shí),可以運(yùn)行可視化模塊;對(duì)比完后,再運(yùn)行刪除虛擬版圖模塊,刪除可視化模塊產(chǎn)生的供觀察用的虛擬版圖,具體的算法和調(diào)用流程如圖3所示。

圖3 三維可視化技術(shù)部分流程圖

4 設(shè)計(jì)實(shí)例

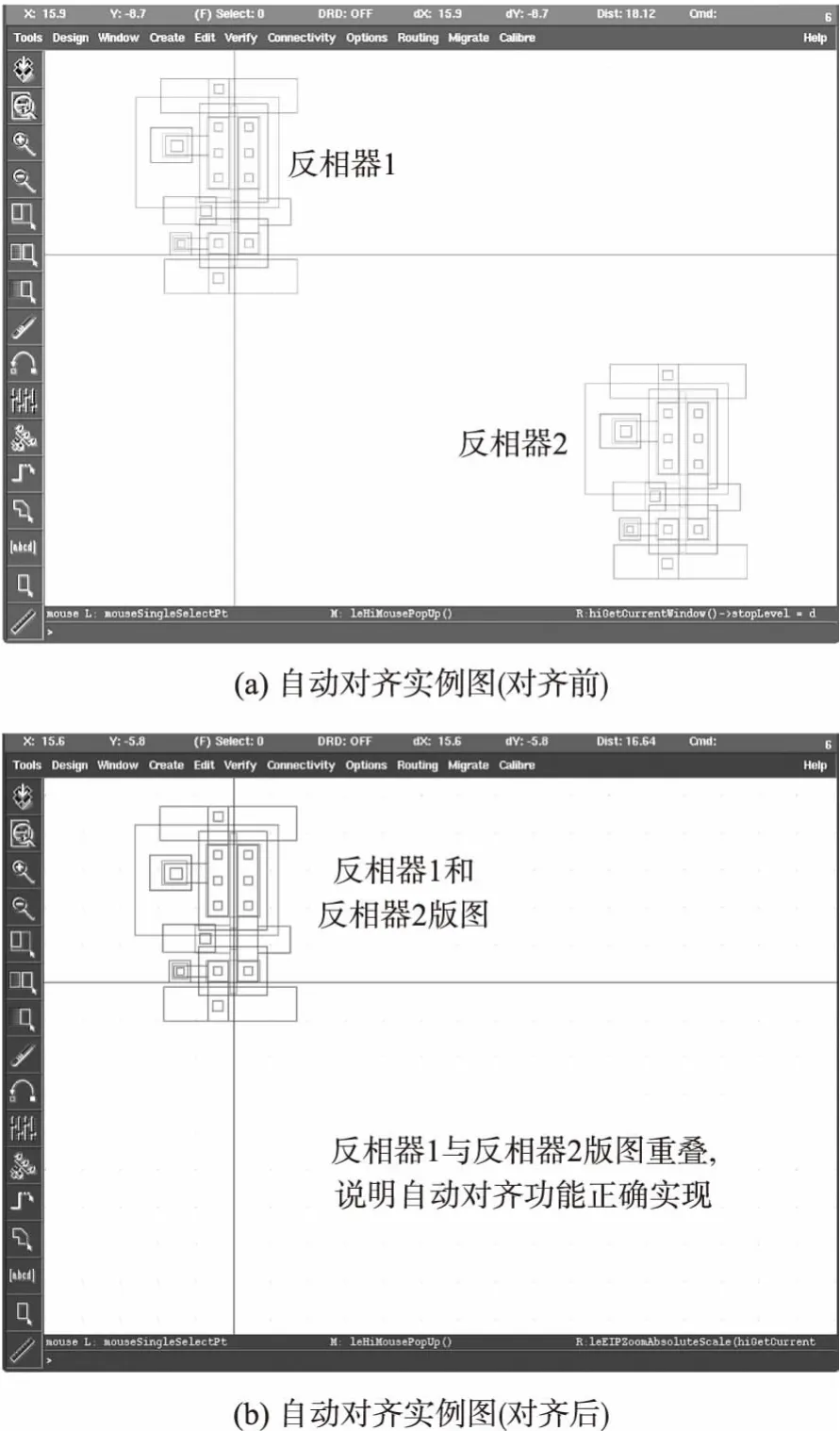

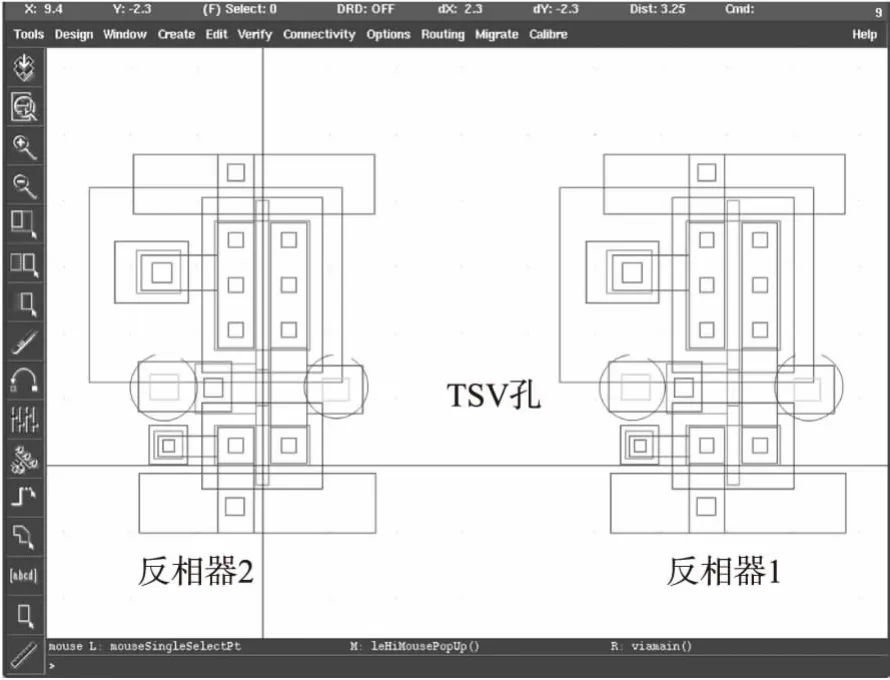

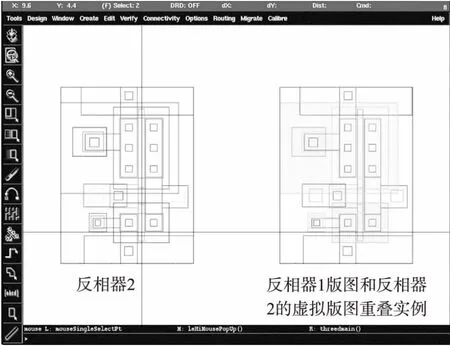

為驗(yàn)證所提插件的正確性和實(shí)用性,本文在三維集成電路工藝背景下設(shè)計(jì)了兩個(gè)并聯(lián)的反相器。在設(shè)計(jì)實(shí)例中,這兩個(gè)反相器分別被命名為反相器1和反相器2,并且在三維集成電路中分別處于兩個(gè)相鄰版圖中。本文針對(duì)反相器1和反相器2版圖,依次運(yùn)行自動(dòng)對(duì)齊、自動(dòng)打孔和三維可視化腳本,并通過觀察運(yùn)行結(jié)果判斷腳本的準(zhǔn)確性。

4.1自動(dòng)對(duì)齊

圖4所示的是自動(dòng)對(duì)齊實(shí)例圖。如圖4(a)所示,分別繪制了反相器1和反相器2版圖。當(dāng)運(yùn)行腳本后,反相器2版圖被整體移動(dòng)和反相器1版圖重合,對(duì)齊后的版圖效果如圖4(b)所示。

圖4 反相器實(shí)例圖

4.2自動(dòng)打孔

圖5所示是自動(dòng)打孔功能運(yùn)行后的示意圖。為了方便觀察自動(dòng)打孔的效果,反相器1和反相器2版圖被手動(dòng)分開。如圖5所示,反相器1和反相器2的TSV位置分別和版圖其他圖形的相對(duì)關(guān)系是完全一致的,說明自動(dòng)打孔的功能是正確的。

圖5 自動(dòng)打孔實(shí)例圖

4.3三維可視化

圖6 三維可視化實(shí)例圖

5 總結(jié)

為了更好的滿足工程師在三維集成電路版圖設(shè)計(jì)中的需要,本文基于業(yè)界主流二維集成電路版圖設(shè)計(jì)工具Cadence Virtuoso,構(gòu)建三維集成電路的版圖設(shè)計(jì)流程;并基于SKILL語(yǔ)言,對(duì)Cadence Virtuoso進(jìn)行二次開發(fā),開發(fā)出能輔助三維集成電路版圖設(shè)計(jì)的EDA插件。該EDA插件主要包括3種功能:自動(dòng)對(duì)齊,自動(dòng)打孔和三維可視化技術(shù)。為了驗(yàn)證該EDA插件在三維集成電路設(shè)計(jì)中的易用性和實(shí)用性,本文在三維集成電路工藝背景下設(shè)計(jì)兩個(gè)并聯(lián)的反相器。實(shí)驗(yàn)表明,該EDA插件簡(jiǎn)化了三維集成電路版圖設(shè)計(jì)過程,具有很好的易用性。

參考文獻(xiàn):

[1]鄭偉,李文鈞,劉軍,孫玲玲.基于90 nm低功耗NMOS工藝射頻器件的版圖優(yōu)化[J].電子器件,2011,34(6),645-648.

[2]Wristers D.Complex Trade-Offs-Enablement of Moore and More Than Moore[C]//2013 International Conference on IC Design and Technology,2013:1-2.

[3]Heinig A,Dietrich M,Herkersdorf A,et al.System Integration—The Bridge between More Than Moore and More Moore,Design [C]//2014 Automation and Test in Europe Conference and Exhibition(DATE),2014:1-9.

[4]Hui Min Lee,En-Xiao Liu,Er-Ping Li,et al.Impact of Technology Scaling on Electrical Characteristics of Through-Silicon Via Correlated with Equivalent Circuits[C]//EMC Europe 2011 York,2011,339-344.

[5]Qian Libo,Zhu Zhangming,Yang Yintang.System Level Performance Evaluation of Three-Dimensional Integrated Circuit[C]//2011 IEEE 9th International Conference on ASIC (ASICON),2011:694-697.

[6]Chen K N,Tan C S.Integration Schemes and Enabling Technologies for Three-Dimensional Integrated Circuits[J].IET Computers and Digital Techniques,2011,5(3),160-168.

[7]夏艷.3D集成的發(fā)展現(xiàn)狀與趨勢(shì)[J].中國(guó)集成電路,2011,146(7):23-28.

[8]Chang-Hsin Cheng,Chung-Kai Liu,Hsing-Chuang Liu,et al.On-Line Error Detection and Correction Techniques for TSV in Three-Dimensional Integrated Circuit[C]//2011 International Symposium on Intelligent Signal Processing and Communications Systems(ISPACS),2011,1-5.

[9]畢宗軍,羅嵐,楊軍.基于SKILL語(yǔ)言的按比例自動(dòng)縮放版圖方法[J].電子器件,2006,29(4):1187-1191.

[10]馬亮.基于VC的Cadence二次開發(fā)[J].電子科技,2011,24(2):98-101.

[11]趙兵,黃凱,楊軍.基于SKILL語(yǔ)言的自動(dòng)天線效應(yīng)修復(fù)器設(shè)計(jì)[J].微電子學(xué),2008,38(2):182-186.

[12]Civale Y,Redolfi A,Jaenen P,et al.Through-Silicon Via Technology for Three-Dimensional Integrated Circuit Manufacturing[C]//2012 35th IEEE/CPMT International Electronic Manufacturing Technology Symposium(IEMT),2012:1-5.

陳 娟(1983-),女,漢,江蘇丹陽(yáng),南京工程高等職業(yè)學(xué)校電子工程系講師,電路與系統(tǒng),cherry_c_j@163.com;

段倩妮(1990-),女,漢,江蘇常州,南京航空航天大學(xué)研究生,集成電路設(shè)計(jì),qianniduan@163.com。

竺興妹(1975-),女,漢,江蘇南京,南京高等職業(yè)學(xué)校電子工程系副教授,電氣自動(dòng)化及其自動(dòng)化技術(shù),472036640 @qq.com;

A System-Level Post-Simulation Verification Platform for Mixed-Signal SoC*

HU Xiaogang1,ZHAO Linna1,YU Zhiguo1*,WEI Jinghe2,GU Xiaofeng1

(1.Key Laboratory of Advanced Process Control for Light Industry(Ministry of Education),Department of Electronic Engineering,Jiangnan University,Wuxi Jiangsu 214122,China;

2.The 58th Research Institute of China Electronics Technology Group Corp,Wuxi Jiangsu 214035,China)

Abstract:Regarding the problem of slow post-simulation speed of the large-scale mixed-signal System-on-Chip (SoC),a system-level post-simulation verification platform for mixed-signal SoC is proposed.Based on the traditional Verilog-cdl post-simulation verification platform and popular EDA tools,the proposed platform utilizes a Verilog-cdl-Verilog simulation method in which the modules with long simulation time are replaced by the Verilog ones.As a result,the verification process is obviously fastened.The design flow of the simulation platform is described in details,including the verification environment setup,the system script design and the mixed-signal simulation interface design.The instruction set simulation based on the verification platform is tested and verified.The results indicate that the verification platform is feasible and reliable,which can shorten the developing period of large-scale mixed-signal SoC.

Key words:mixed signal SoC; post-simulation; Verilog-cdl-Verilog; verification platform

doi:EEACC:257010.3969/j.issn.1005-9490.2015.04.008

收稿日期:2014-10-17修改日期:2014-11-11

中圖分類號(hào):TN402

文獻(xiàn)標(biāo)識(shí)碼:A

文章編號(hào):1005-9490(2015)04-0749-05

項(xiàng)目來源:國(guó)家自然科學(xué)基金項(xiàng)目(61106029)