基于可控采樣率及斷點保護的數據采編存儲器設計

季 偉 ,蘇淑靖 ,喬文生 ,張 斌

(1.中北大學 儀器科學與動態測試教育部重點實驗室 電子測試技術國家重點實驗室,太原 030051;2.中國航天科工集團第六研究所601所,呼和浩特 010076;3.中北大學 經濟與管理學院,太原 030051)

隨著信息技術的發展,采編存儲器的采樣速度、通道數、精度也隨之提高[1-2],但是對其通用性也提出了要求。本設計采用FPGA(現場可編程門陣列)作為控制芯片,設計了16通道可以設置為不同采樣率的同步采編存儲器,該存儲器還具有掉電監測功能和FLASH斷點保護功能。本設計利用VHDL的并行特性,充分發揮了FPGA改動靈活方便和并行控制的特點[3],克服了多通道同步采集、不同采樣率ADC數據混合編幀和斷點保護等設計難點,提高了所設計的采編存儲器的通用性。

本文設計的數據采編存儲器可以同步采樣16路0 V~5 V的模擬電壓信號,可選擇1 kS/s,5 kS/s,10 kS/s,25 kS/s和50 kS/s 5種采樣率,具有0.1%FS的精度。

1 總體方案設計

采編存儲器內的16路輸入采集卡功能框圖如圖1所示。采集卡由阻抗匹配、減法電路、四階抗混疊濾波器、放大電路、8路同步采樣ADC、基準電壓源、掉電檢測電路、控制單元和背板總線組成。FPGA選用了XILINX公司的低成本Spartan-3E系列中的XC3S500E,可提供50萬個系統門數、4656個Slice、73 kb分布式RAM和360 kb塊RAM容量。其可靈活配置、低功耗的特性足以滿足設計要求。

圖1 采編存儲器總體設計圖Fig.1 Acquisition overall diagram

系統工作原理為16路模擬信號從輸入接口接入,經過16路模擬信號調理,由FPGA控制ADC實現模數轉換、編幀、存儲,數據通過背板總線上傳。為了滿足通道數和采樣精度的設計要求,實現同步采集,提高電路集成度,ADC采用ADI公司的AD7606,它可以8通道同步模擬采樣,處理±5 V真雙極性輸入信號,有高達1 MΩ的固定輸入阻抗,采樣率最大達200 kS/s。上位機可以實時分析采樣數據。采編存儲器受上位機命令控制。

2 掉電監測電路設計

采編存儲器工作時,需要寫入或讀取FLASH。如果此時基準電壓源故障導致意外掉電,可以引起系統程序跑飛而無法繼續工作,甚至造成大量數據的丟失,帶來不可彌補的損失,影響數據的完整性、正確性。而且下次上電時,難以恢復上次的存取狀態,導致數據因為掉電而損壞。為了避免出現這種情況,設計了掉電監測電路,采用MAX709監測電源電壓,同時產生系統的復位信號。

MAX709能夠在加電、掉電以及降壓情況下,使其RESET引腳變為低電平,提供復位信號。MAX709不受短持續期的Vcc瞬變的影響,能夠提供可靠的復位信號[4]。因此MAX709的RESET低電平信號可以用作掉電的監測信號。由于電容性器件的存在,當系統掉電時,工作電壓下降到系統無法工作的危險電壓之前有一定的時間延遲,這段時間可以執行數據保護操作。經過示波器測試,本采編存儲器從監測到掉電信號到工作電壓下降到危險電壓的時間約為 4 ms。MAX709的RESET連接到FPGA,作為復位和掉電信號。

3 邏輯設計

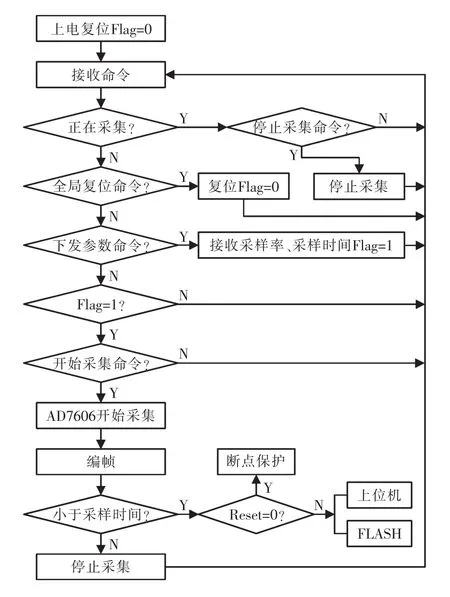

3.1 總體邏輯設計

總體邏輯包括時鐘產生模塊、命令模塊、全局復位模塊、全局時鐘模塊、A/D控制模塊、FIFO、編幀模塊。由全局時鐘模塊產生全局同步時鐘信號,同步所有模塊的操作。A/D控制模塊與編幀模塊之間采用乒乓操作設計。2個ADC的數據交替地寫入2個FIFO里,編幀模塊對數據進行混合編幀,之后數據同時存儲到上位機和FLASH中。模塊框圖如圖2所示,總邏輯流程如圖3所示。

圖2 程序模塊框圖Fig.2 Program module diagram

圖3 總邏輯流程圖Fig.3 Flow chart of general logic

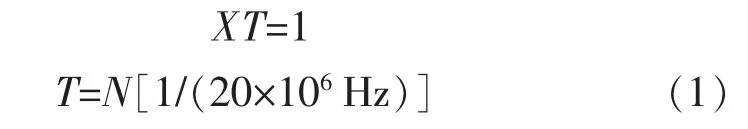

3.2 ADC采樣率可變設計

為了滿足通道數要求,采用2片AD7606在FPGA的控制下進行同步采集。AD7606設置為并行字節模式,8通道同步采樣,每個通道的數據以字節為單位,在并口DB[7:0]先輸出高字節后再輸出低字節。如果對2片ADC順序控制,非但體現不出FPGA的并行控制的優勢,而且無法實現16通道同步采集。設計中對2個ADC采用了雙進程分別進行控制。在VHDL中同一個結構體內的2個進程是并行執行的[5],這就使2個ADC可以同時采樣,而且2個ADC可以以不同的采樣率同時采樣。AD7606的采樣周期受輸入CONVST管腳的邏輯電平控制。為了使采樣率變化,必須控制CONVST管腳的電平周期。AD7606的工作時鐘為20 MHz,為了實現5種可選的采樣率,在AD控制程序中需要對狀態計數。在采樣率為X時,每次采樣對應的狀態數N可計算為

式中,T為CONVST電平變化的周期。在ADC采樣轉換后讀取數據會占用采樣時間使采樣率降低,所以設計為在采樣轉換期間讀取上一次采樣數據,保證采樣率按設計要求實現。并行字節模式在轉換期間讀取數據的時序如圖4所示。

圖4 并行字節模式讀取數據時序圖Fig.4 Parallel byte mode data read time sequence

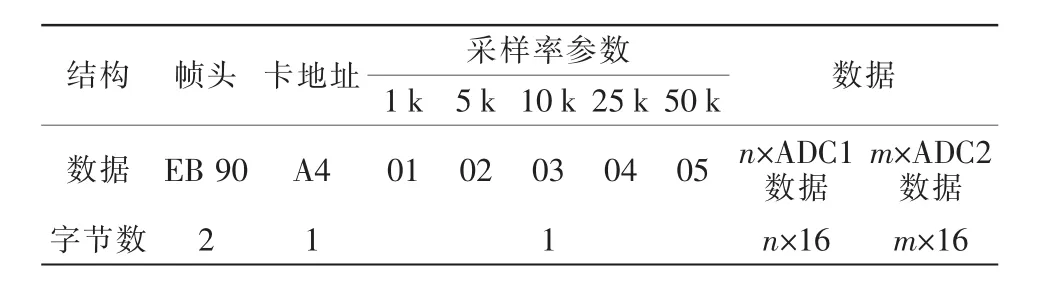

3.3 數據混合編幀設計

采樣率的可選設計給數據編幀帶來了困難,因為幀結構是隨著采樣率的不同而變化的。本設計中不同的ADC可以不同采樣率同時工作,編幀模塊必須根據每個ADC的采樣率設置其幀結構。設計如圖2所示,每個ADC分配了獨立的緩存FIFO,使不同幀結構的數據不會混淆以至無法區分。而幀結構設計為如表1所示的16通道混合可變結構,每幀數據為16個通道1 ms采到的數據。其中n為ADC1即前八通道的每毫秒采樣次數,m為ADC2即后八通道的每毫秒采樣次數。n和m的值可以由采樣率得出。編幀模塊根據采樣率參數設置n和m值,分別從2個FIFO中讀出16 n個字節和16 m個字節,再加上幀頭、卡地址和采樣率參數組成一幀。編好幀的數據就可以傳給上位機或者存儲到FLASH中。

表1 幀結構表Tab.1 Frame structure

3.4 數據緩存設計

A/D控制模塊控制著2片ADC,2片ADC可以設置為不同采樣率進行采樣。而這2片ADC的采樣數據要按設計的幀結構存儲在一起。編幀模塊與FLASH模塊的工作頻率與數據傳輸速度不同,而且FLASH頁編程的200 μs期間不能寫入數據,上位機讀數周期則為1 ms。這2段時間內數據不能存儲和上傳,需要數據緩存。按可設置的最快采樣率50 kS/s計算緩存數據,參照表1,那么每幀的數據量D可用下式計算:

D=2+1+1+50×16+50×16=1604 B

因此,對FLASH而言,需要緩存的數據量為

200 μs×1604 B/ms=320.8 B

而上位機需要緩存的數據量為

1 ms×1604 B/ms=1604 B

選用容量為2048 B的FIFO作為緩存,足以滿足緩存需要。

3.5 FLASH無效塊檢測及斷點保護

FLASH存儲芯片采用了三星公司的NAND芯片K9WBG08U1M。其塊擦除時間為1.5ms,頁編程時間為 200 μs,容量為 4 GB。

FLASH中不可避免地存在無效塊,無效塊不能被用來存儲數據,因此在寫入、讀取操作前都要識別無效塊。常規做法是對無效塊建立地址表,通過對地址表的查詢識別無效塊。這種方法需要占用FPGA中寶貴的存儲資源,而且每次操作之初都必需更新無效塊地址表,否則如果出現新的無效塊,存儲數據就會出錯。為此,本設計采用了在每次寫入、讀取、擦除之前對每一塊進行無效塊檢測的方法。無效塊檢測采用讀取每塊前2頁的第2048字節的內容來實現,如果讀到非FFh的數據則認為該塊為無效塊。因為擦除操作失敗會產生無效塊,在每次擦除操作后必須對操作成功與否進行檢測,即擦除操作完成后,查看I/O 0位的值,如果非0則擦除失敗。在擦除失敗的塊前2頁的第2048字節處寫入00h,將其標記為無效塊。

FPGA的FLASH模塊檢測到MAX709的RESET信號時,會進入斷點保護程序。斷點保護是在存儲數據的過程中,為避免因系統電源電壓欠壓甚至切斷而造成數據存儲紊亂而采取保護的一種措施[6]。斷點保護程序需要保存FLASH斷點地址,即當前的寫入地址和讀取地址。本設計將斷點地址保存在FLASH的第一塊中,所以保存新地址之前需要擦除舊地址。這些擦除、寫入操作需要在系統開始掉電的4 ms之內完成,而FLASH的頁編程典型時間為200 μs,塊擦除典型時間為1.5 ms,斷點程序共需要約1.7 ms來完成斷點保護,時間在4 ms之內,斷點保護程序可以實現。

4 測試結果

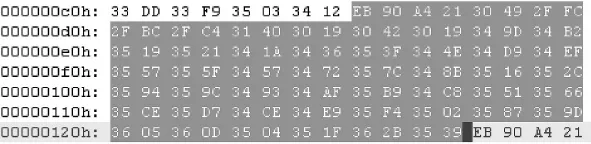

如圖5所示為采集卡采樣到的數據的幀結構,每幀共100 B,其中,EB 90為幀頭,A4為卡地址,21表示前八通道采樣率為5 kS/s,后八通道采樣率為1 kS/s,由表1計算可知與設計相符。

圖5 幀結構圖Fig.5 Frame structure

用GPS-4303C型穩壓電源為采編存儲器輸入4.8008 V(使用6位半精度的高精度萬用表測得)的直流電壓,計算通道10的精度為(4.8008-4.7995)/5=0.026%,小于滿量程的0.1%。

圖6為給采編存儲器輸入0~5 V正弦波后,上位機通道1和通道9的輸出波形。

圖6 上位機輸出波形Fig.6 Software output wave

5 結語

本設計使用FPGA做采編存儲器的控制芯片,實現了16路數據同步采樣、不同采樣率ADC的混合編幀和FLASH存儲器的斷點保護。設計的采編存儲器能夠在采樣率可選的情況下同步采樣多路數據,達到了較高精度,提高了設計通用性,滿足設計要求。

[1]李念強,魏長智,潘建軍,等.數據采集技術與系統設計[M].北京:機械工業出版社,2009:1.

[2]胡曉軍.數據采集與分析技術[M].2版.西安:西安電子科技大學出版社,2010:1-5.

[3]郭亮,衛一然,甄國涌.基于FPGA的高速數據采集系統設計實現[J].計算機測量與控制,2013,21(2):537-539.

[4]吳東,張岡,張志鵬,等.一種實用的掉電檢測和保護電路[J].電子技術應用,1999,25(6):69-70.

[5]侯伯亨,顧新.VHDL硬件描述語言與數字邏輯電路設計[M].西安:西安電子科技大學出版社,2000:10-60.

[6]冉自博.基于U盤高速串行數據記錄器設計[D].山西:中北大學,2014.