用于DVFS片上系統的全數字SARDLL設計

徐太龍,薛 峰,高先和,蔡志匡,韓少宇,胡學友,陳軍寧

(1.合肥學院電子信息與電氣工程系,合肥230601;2.安徽三聯學院電子電氣工程學院,合肥230601;3.南京郵電大學電子科學與工程學院,南京210046;4.安徽大學電子信息工程學院,合肥230601)

1 概述

互補金屬氧化物半導體(Complementary Metal Oxide Semiconductor,CMOS)工藝的發展,極大地提高了系統芯片(System-on-Chip,SoC)的復雜度和工作頻率[1-4]。功耗成為繼速度、面積后日益關注的問題,各種低功耗技術應運而生,其中,動態電壓/頻率調整(Dynamic Voltage/Frequency Scaling,DVFS)技術被認為是最有效的低功耗管理方法之一[5]。動態電壓/頻率調整技術的工作原理是根據器件的工作模式動態地調整處理器的工作電壓和頻率,從而有效地控制芯片的功耗[1,6-8]。由于工作頻率發生了變化,因此需要一個消除時鐘偏差的電路來快速同步系統芯片中每個子系統的時鐘相位[9-10]。鎖相環(Phase-Locked Loop,PLL)和延時鎖定環(Delay-Locked Loop,DLL)是2種常用的時鐘同步電路,在不需要對輸入時鐘信號倍頻時,延時鎖定環由于不累積時鐘抖動而被廣泛地用作系統芯片中的時鐘同步電路以消除時鐘偏差[11-13]。

當延時鎖定環用于采用了動態電壓/頻率調整技術的系統芯片時,必須具備2個條件:(1)寬的工作頻率范圍;(2)快速鎖定,即鎖定時間短[1,6-7]。從電路實現的方式上,可以把延時鎖定環分為全模擬、全數字和混合3類[14]。全數字延時鎖定環(All Digital Delay-Locked Loop,ADDLL)因具有易于集成、抗工藝、電壓、溫度(Process,Voltage,Temperature,PVT)變化能力強的特點,而更適合用于系統芯片中以消除偏差、同步時鐘信號。全數字延時鎖定環根據搜索算法可以分為3種:(1)采用線性搜索算法,如寄存器控制的延時鎖定環(Register-controlled Delay-Locked Loop,RDLL)和計數器控制的延時鎖定環(Countercontrolled Delay-Locked Loop,CDLL),鎖定時間隨著控制字位數的增加成指數增長;(2)采用閃存架構,即時間數字轉換(Time-to-Digital Conversion,TDC)方案,但會占用很大的面積和消耗很大的功耗;(3)采用二元搜索算法(Binary Search Algorithm,BSA),即逐次逼近寄存器控制方案(Successive Approximation Register-controlled,SAR)。其中,逐次逼近寄存器方案是在考慮復雜度和鎖定時間折中條件下的最佳方案[12,15]。

在寬工作頻率范圍應用時,傳統全數字逐次逼近寄存器延時鎖定環存在諧波鎖定,即假鎖和零延時陷阱的問題[1,12,15]。文獻[1,15]提出采用可復位數字控制延時線(Resettable Digitally Controlled Delay Line,RDCDL)方案來消除諧波鎖定和零延時陷阱。文獻[1]的延時單元中包含二選一數據選擇器,增加了延時線的復雜度和面積。文獻[15]中的方案需要前置延時單元才能正確地工作,增加了延時線的固有延時,限制了最高工作頻率。本文設計一種改進的可復位數控延時線,在降低面積的同時增大延時鎖定環的最高工作頻率。

2 系統描述

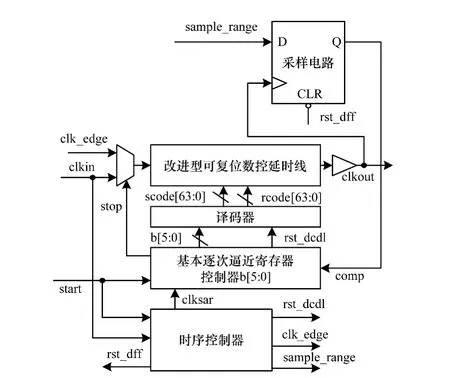

本文設計的全數字逐次逼近寄存器延時鎖定環的系統框圖如圖1所示。基本結構與文獻[1]提出的結構相同,由時序控制電路、基本逐次逼近寄存器控制器[2]、譯碼器、數據選擇器、采樣電路和本文提出的改進型可復位數控延時線(Digitally Controlled Delay Line,DCDL)組成。

圖1 延時鎖定環的系統框圖

整個延時鎖定環系統的工作時序如圖2所示[1]。在開始階段,信號start初始化整個系統。

圖2 延時鎖定環的工作時序圖

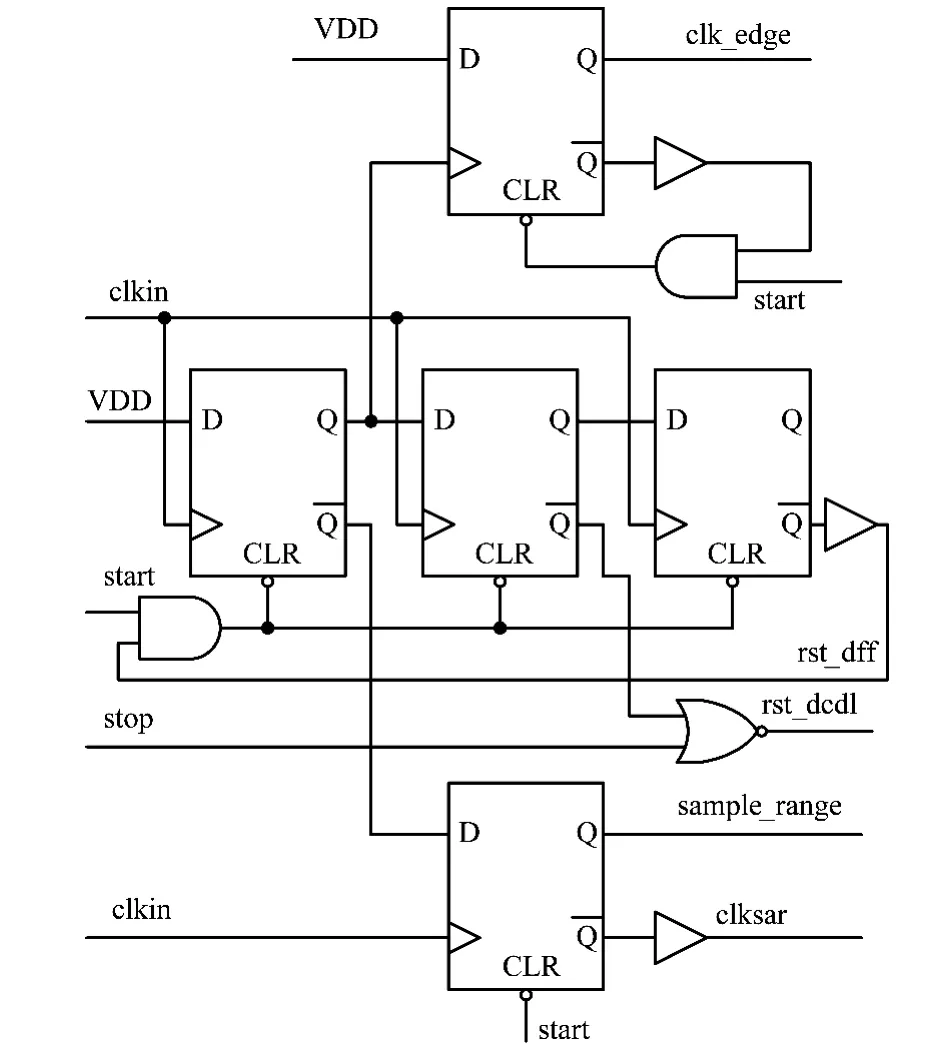

圖2中的所有控制信號由圖3所示的時序控制電路產生[1]。

輸入時鐘信號clkin的3個周期決定1位SAR控制字。在clkin的第1個周期,短脈沖信號clk_edge產生,信號sample_range設置為高電平“1”。并且,clk_edge進入DCDL中,如果在sample_range的高電平期間,clk_edge沒有到達clkout,說明對應的DCDL的延時量過大,需要修改SAR控制字以減少DCDL的延時量。相反,對應的SAR控制字將保持不變。在clkin的第2個周期,信號rst_dcdl被置為高電平,對DCDL進行復位以確保延時線中沒有殘留的clk_edge。若沒有對DCDL進行復位,殘留的clk_edge會在下一個sample_range的高電平期間出現在clkout,并用于決定下一位SAR控制字,而不能正確反映當前clk_edge在DCDL中的狀態,可能導致錯誤的SAR控制字,因此必須在clkin的第2個周期對DCDL復位,以清除殘留的clk_edge信號,同時調整SAR控制字。在第3個clkin周期,SAR控制字有足夠的時間來改變DCDL的延時量。同時在第3個clkin周期的開始處,產生一個短脈沖信號rst_dff用來對采樣電路和時序控制電路的觸發器進行復位。每3個clkin周期,重復一次以上所述過程。

圖3 時序控制電路原理

在clkin的第1個周期時,如果clk_edge出現在clkout,對應的SAR控制字保持不變。然后下1位SAR控制字置“1”以增加DCDL的延時量,阻止DLL向著clkin的第1個時鐘上升沿方向鎖定,從而有效地解決零延時陷阱問題。另一方面,在clkin的第1個周期,如果clk_edge沒有出現在clkout處,相應位的SAR控制字被復位,減小DCDL的延時量,因此,可以有效地消除諧波鎖定現象。

圖2中SAR控制字的變化和最基本的傳統SAR的工作原理一樣,只是SAR控制器的時鐘信號clksar的周期是輸入時鐘信號clkin周期的3倍[2]。

3 改進型可復位數控延時線

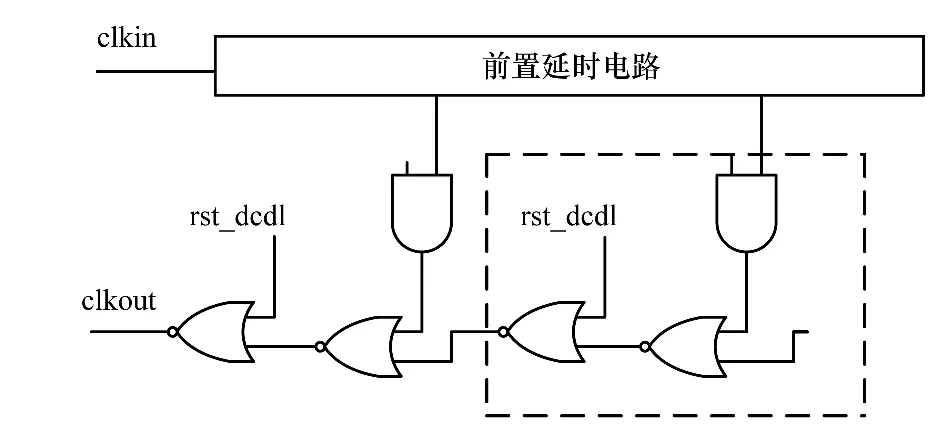

為了消除諧波鎖定和零延時陷阱現象,文獻[1,15]提出了可復位數控延時線方案。文獻[1]的可復位數控延時線方案如圖4所示,每個延時單元的結構如圖中虛線框內所示,由于需要2個二選一數據選擇器,增加了芯片面積。

圖4 文獻[1]中的可復位延時線延時單元

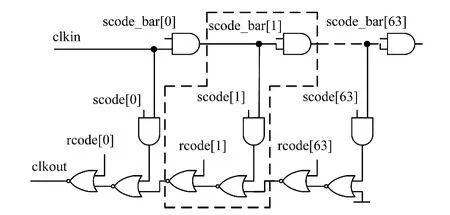

文獻[15]的可復位延時線方案如圖5所示,輸入時鐘信號clkin需要經過前置延時電路后才能進入延時線中,前置延時電路增加了系統的固有延時,限制了系統的最高工作頻率。

圖5 文獻[15]中的可復位延時線延時單元

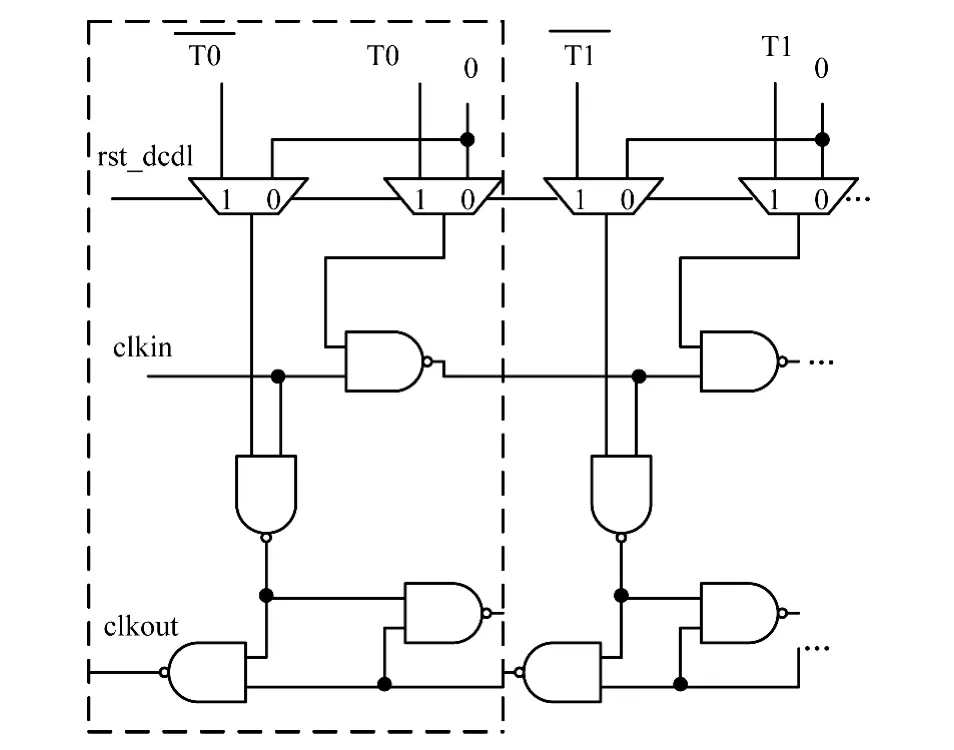

為了解決以上2種方案存在的問題,本文設計了一種改進型可復位延時線方案,如圖6所示。

圖6 改進型可復位延時線延時單元

每個延時單元由2個與門和2個或非門組成,如圖6中虛線框內所示。信號scode由SAR控制字b[5:0]譯碼而來,當scode為高電平時,輸入時鐘信號clkin從該單元進入延時線,并向左傳輸,相反,時鐘信號clkin不從該單元進入延時線。信號rcode={scode[62:0],1’b0}|{64{rst_dcdl}},信號 scode_bar=~{scode|{64{rst_dcdl}}},當這2個信號為高電平時,完成DCDL的復位功能,清楚殘留在DCDL中的clk_edge信號。改進后的延時線既不需要前置延時電路也不需要二選一數據選擇器,在提高系統最高工作頻率的同時,減小了芯片面積。

4 仿真結果與對比

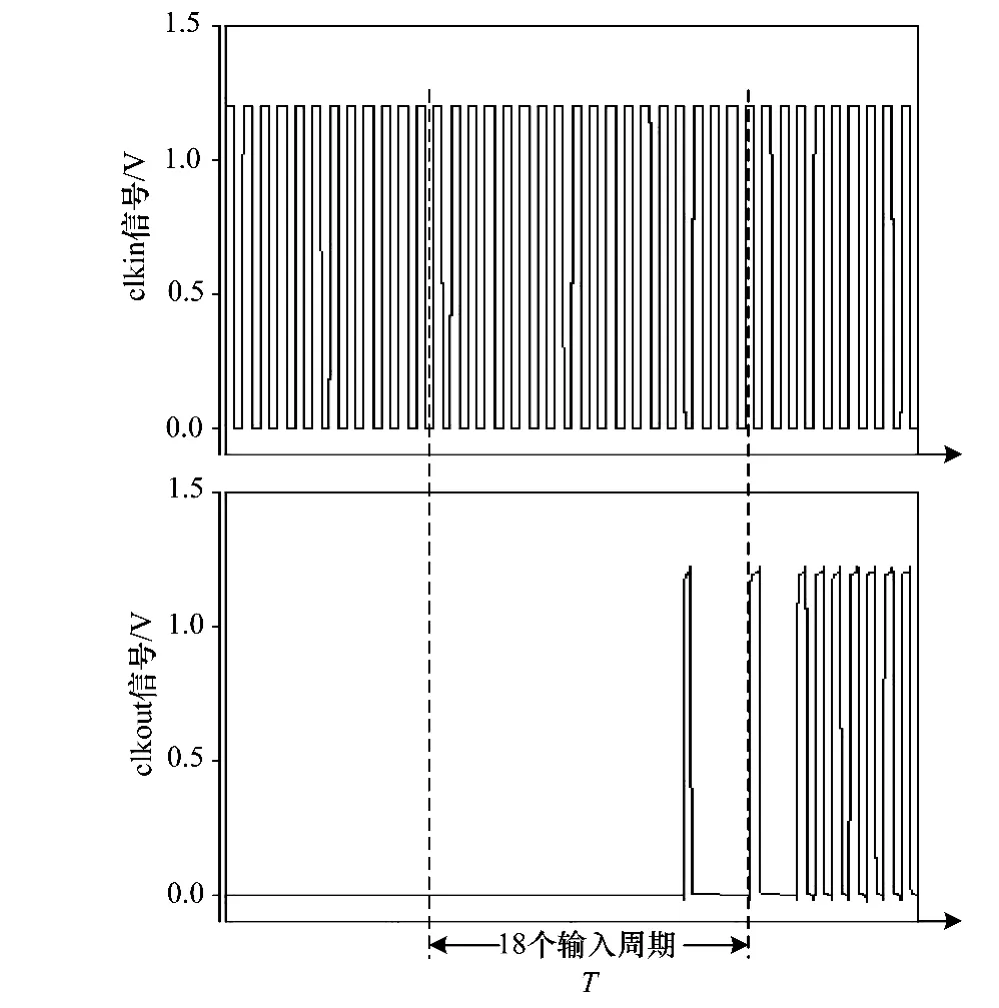

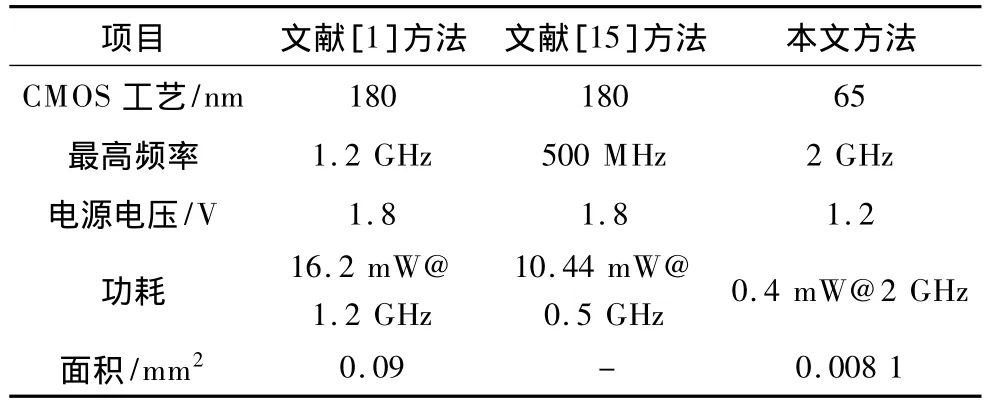

圖1所示的全數字逐次逼近寄存器延時鎖定環采用TSMC CMOS 65nm LP工藝標準單元實現,核心電路版圖所占的面積為0.008 1 mm2。版圖后仿真結果表明其工作頻率范圍為250 MHz~2 GHz,功耗為0.4 mW@2 GHz,整個工作頻率范圍內,鎖定時間為18個輸入時鐘周期。圖7所示為輸入時鐘為2 GHz時的鎖定過程。圖8所示為輸入時鐘為250 MHz時的鎖定過程。

圖7 輸入時鐘為2 GHz時系統的鎖定過程

圖8 輸入時鐘為250 MHz時系統的鎖定過程

文獻[1,15]方法與本文方法的性能對比如表1所示,表明本文的設計在提高最高工作頻率的同時,減少了核心電路版圖所占的面積。

表1 性能對比

5 結束語

根據動態電壓/頻率調整低功耗SoC中時鐘同步問題的要求,本文提出一種改進型可復位數控延時線方法。利用數字集成電路設計流程實現了一個寬工作頻率范圍、小面積、無諧波鎖定和解決無零延時陷阱的全數字逐次逼近寄存器延時鎖定環。仿真結果表明,采用該方案的延時鎖定環能滿足DVFS SoCs的要求。下一步工作方向為加快延時鎖定環的鎖定速度等。

[1] Yao C Y,Ho Y H,Chiu Y Y,et al.Designing a SAR-based All-digitalDelay-locked Loop with Constant Acquisition Cycles Using a Resettable Delay Line[J].IEEE Transactions on Very Large Scale Integration Systems,2014,22(9):1-8.

[2] 徐太龍,薛 峰,蔡志匡,等.快速全數字逐次逼近寄存器延時鎖定環的設計[J].計算機工程,2014,40(4):262-268.

[3] 徐太龍,陳軍寧,孟 堅,等.全數字延時鎖定環的研究進展[J].小型微型計算機系統,2014,34(6):1371-1374.

[4] DehngGuang-Kaai,Hsu June-Ming,Yang Ching-Yuan,et al.Clock-deskew Buffer Using a SAR-controlled Delay-locked Loop[J].IEEE Journal of Solid-state Circuits,2000,35(8):1128-1136.

[5] Flynn D.IntelligentEnergy Management:An SoC Design Based on ARM926EJ-S[C]//Proceedings of the 15th Hot Chips Conference. Berlin, Germany:Springer,2003.

[6] Chen Weicheng,Yang Rong-Jyi,Yao Chia-Yu,et al.A Wide-range All-digital Delay-locked Loop Using Fastlock Variable SAR Algorithm[C]//Proceedings of International Symposium on Intelligent Signal Processing and Communication Systems.Washington D.C.,USA:IEEE Press,2012:338-342.

[7] Yao Chia-Yu,Ho Yung-Hsiang.A Fast-locking Widerange All-digital Delay-locked Loop with a Starting SAR-bit Prediction Mechanism[C]//Proceedings of International Symposium on VLSI Design,Automation,and Test.Washington D.C.,USA:IEEE Press,2013:1-4.

[8] Chung Ching-Che,Chang Chia-Lin.A Wide-range Alldigital Delay-locked Loop in 65 nm CMOS Technology[C]//Proceedings of International Symposium on VLSI Design, Automation, and Test.Washington D.C.,USA:IEEE Press,2010:66-69.

[9] Chen Yougang,Tsao H W,Hwang C S.A Fast-locking All-digital Deskew Buffer with Duty-cycle Correction[J].IEEE Transactions on Very Large Scale Integration Systems,2013,21(2):270-279.

[10] Park J H,Jung D H,Ryu K,et al.ADDLL for Clockdeskew Buffer in High-performance SoCs[J].IEEE Transactions on Very Large Scale Integration Systems,2013,21(7):1368-1373.

[11] Wang Lei,Liu Leibo,Chen Hongyi.An Implementation of Fast-locking and Wide-range 11-bit Reversible SAR DLL[J].IEEE Transaction on Circuit and Systems,2010,57(6):421-425.

[12] Yang Rong-Jyi, Liu Shen-Iuan. A 40-550 MHz Harmonic-free All-digital Delay-locked Loop Using a Variable SAR Algorithm[J].IEEE Journal of Solid-state Circuits,2007,42(2):361-373.

[13] Lin Weiming,Chen Chao-Chyun,Liu Shen-Iuan.An All-digital Clock Generator for Dynamic Frequency Scaling[C]//Proceedings of International Symposium on VLSI Design,Automation,and Test.Washington D.C.,USA:IEEE Press,2009:251-254.

[14] Dehng Guang-Kaai,Lin Jyh-Woei,Liu Shen-Iuan.A Fast-lock Mixed-mode DLL Using a 2-b SAR Algorithm[J].IEEE Journal of Solid-state Circuits,2001,36(10):1464-1471.

[15] Huang K,Cai Z K,Chen X,et al.A Harmonic-free All Digital Delay-locked Loop Using an Improved Fastlocking Successive Approximation Register-controlled Scheme[J].IEICE Transactions on Electronics,2009,92(12):1541-1544.