基于ARM9+FPGA的便攜式視頻展示臺的設計

梁皓東,張國平

(華中師范大學物理科學與技術學院,湖北武漢 430079)

基于ARM9+FPGA的便攜式視頻展示臺的設計

梁皓東,張國平

(華中師范大學物理科學與技術學院,湖北武漢 430079)

目前市場上的便攜式視頻展示臺普遍功耗大、成本高。針對此問題,基于對ARM9和FPGA的嵌入式實時圖像處理平臺的研究,提出了一種便攜式視頻展示臺的設計方案。充分利用ARM9高性能、低功耗、低成本等特點,結合FPGA傳輸處理高分辨率圖像的能力,設計了便攜式視頻展示臺,其具有體積小、易攜帶、低功耗、低成本和高清顯示等特點。此外,詳細介紹了各模塊Linux設備驅動的設計。

便攜式視頻展示臺;嵌入式Linux;LCD控制器;SDRAM控制器;VGA時序

視頻展示臺是將實物、文稿、圖片和過程等信息轉換為圖像信號輸出在投影機、顯示器上展示出來的一種演示設備。便攜式視頻展示臺由于具有體積小、易于攜帶等優點,被廣泛用于教學、大型會議及產品展示等場合,具有較大的研究前景。市場上的視頻展示臺普遍存在體積大、功耗高、價格貴等特點。本文采用并行嵌入式處理結構,設計了基于ARM9和FPGA的便攜式視頻展示臺,在最大限度實現高分辨率圖像實時處理與顯示的同時,也使圖像處理平臺體積更小、功耗更低、成本更低。其內容主要包括高清圖像的采集與存儲,基于FPGA的SDRAM控制器的設計、ARM9和FPGA的通信方式以及各模塊基于Linux平臺的驅動設計。此視頻展示臺輸出分辨率為1 024×768,60 Hz。

1 系統硬件設計

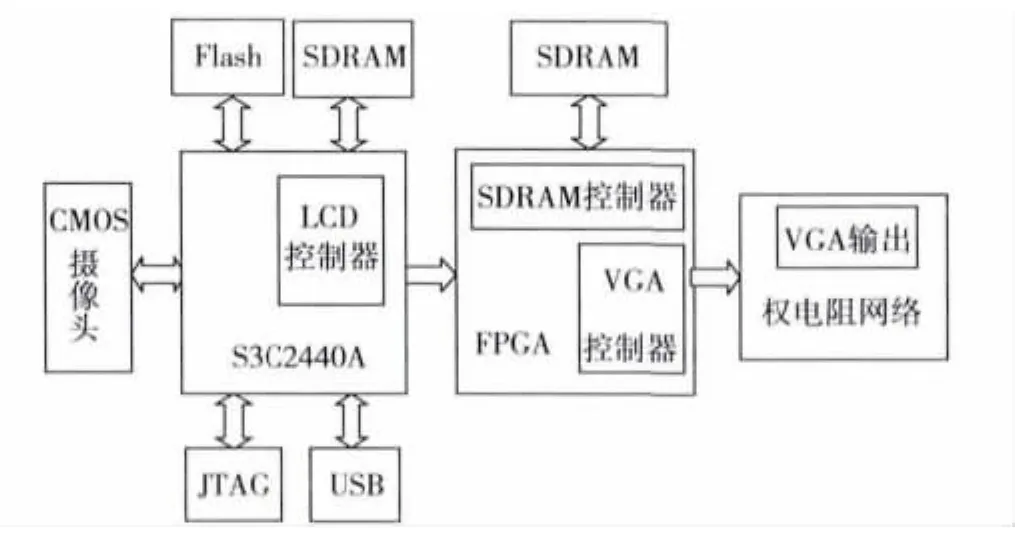

本便攜式視頻展示臺的設計方案主要由兩個模塊構成:ARM9主控模塊和FPGA從模塊,如圖1所示。ARM9主控模塊采用具有極快讀寫速度的2片32 Mbit/s的SDRAM來保證Linux操作系統的流暢運行。主要功能是控制實物、文稿、圖片和過程等視頻信號的采集與存儲,并把采集到的信號通過自身攜帶的LCD控制器并行送入FPGA從模塊,這能很好地解決其他設計通過SPI總線串行傳送圖像導致的傳輸圖片大小和速率受限的問題。

圖1 硬件系統圖

FPGA從模塊的主要功能是把從LCD控制器傳送過來的LCD接口信號送入高速SDRAM進行緩存,并通過SDRAM控制器把SDRAM中緩存的信號讀出送入具有模數轉換功能的權電阻網絡中,將LCD接口信號轉換成與VGA掃描邏輯相匹配的時序信號。

此外,為了給實物、文檔、圖片或者演示過程提供照明光源,本方案在OV9655攝像頭旁邊加了一圈LED小燈,并通過步進電機來控制照明小燈的高度,保證良好的采集視野,小燈的暗滅與高度變化采用按鍵來操作。硬件采用基于ARM9內核的三星S3C2440A處理器,其具有高性能、低功耗、低成本等特點。采用Altera公司的FPGA處理器EPC3T14417N,這是一款性能較好但成本較低的FPGA芯片,滿足本設計圖像數據的處理要求。

2ARM9主控模塊

2.1 視頻采集硬件接口及其分析

本部分采用攝像頭接口控制單元CAMIF和I2C總線來控制和傳輸具有130萬像素的OV9655攝像頭采集實物、圖片、文檔或者過程等視頻數據。選擇CMOS傳感器是因為它有功耗低、編程方便、成本低等優點。其主要引腳及功能描述如下:CAMCLKOUT是CPU輸出的采樣時鐘,幀同步信號VSYNC、行同步信號HREF、像素時鐘信號PCLK由OV9650內部產生,輸入到S3C2440A芯片中,用于對圖像采集進行控制[1]。此外,本設計充分利用了OV9655攝像頭在Linux系統下的照相功能,可把實物或者文檔的照片保存在Flash中進行回放。按照系統的要求,在配置攝像頭信號輸出模式時,選擇P通道模式,輸出數字RGB556信號。

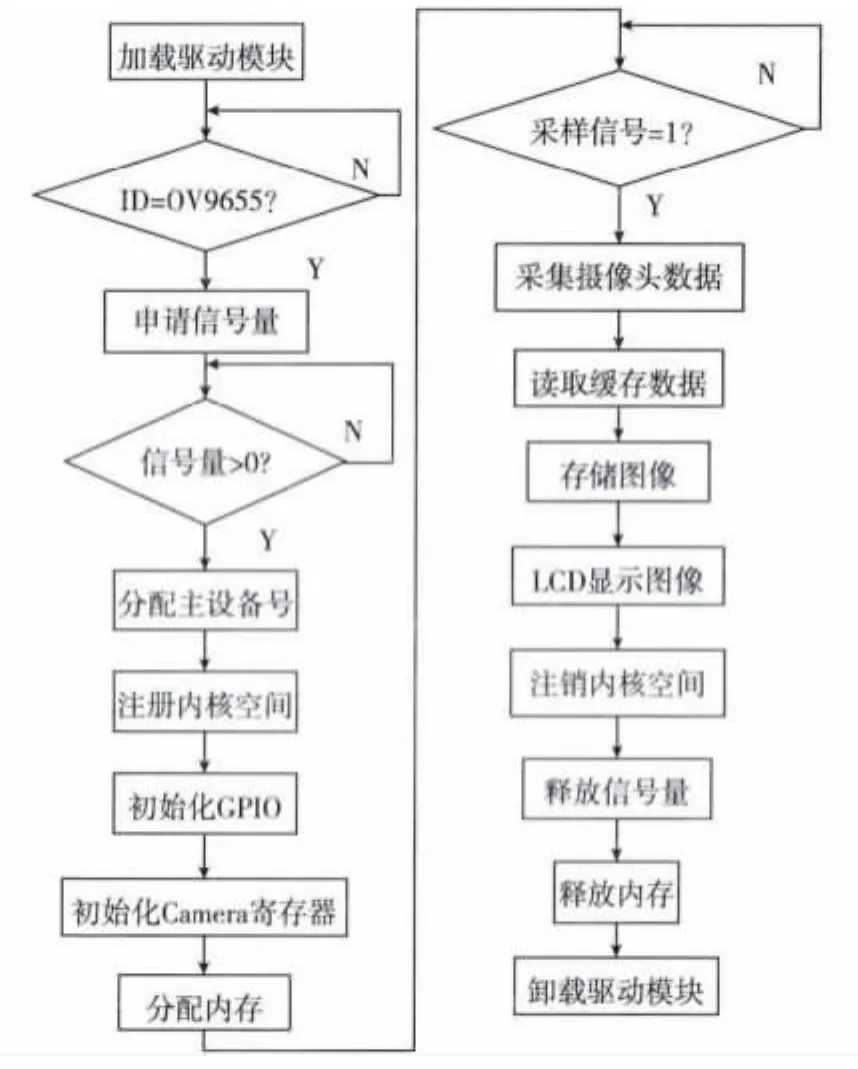

2.2 視頻采集驅動設計

在 Linux 2.6.30/drivers/media/video 目錄下建立OV9655.c、CAMERAIF.c 和 SCCB.c 三 個 源 文 件。OV9655.c負責設備初始化、與內核的通信;CAMERAIF.c管理攝像頭寄存器的配置;SCCB.c用于I2C數據傳送[2]。其驅動設計流程圖如圖2所示。

圖2 攝像頭驅動設計流程圖

修改 Linux 2.6.30/drivers/media/video目錄下的Kconfig、Makefile文件,添加新增攝像頭驅動信息,把驅動設置為<M>類型,表示屬于可加載型驅動以避免重新編譯內核。編譯源文件,生成3個加載模塊:V9655.ko,CAMERAIF.ko 和 SCCB.ko,通過串口復制到開發板[3]。

3 FPGA從模塊

3.1LCD控制器接口和VGA接口描述

S3C2440A帶有LCD控制器,可以很方便地控制驅動掃描式接口的TFT顯示。其主要功能引腳有:像素時鐘信號引腳 VCLK/LCD,場同步信號引腳 VFRAME/VSYNC,行同步信號引腳 VLINE/HSYNC,VD[23:0]是RGB數字信號輸出端口。LCD控制器能夠傳輸圖像數據和產生需要的控制信號、本設計中ARM9通過并行接口按照24位傳送給FPGA.

VGA接口使用模擬RGB通道,逐點、逐行掃描,其關鍵信號有5個,分別是行同步信號、場同步信號、紅色模擬信號、綠色模擬信號和籃色模擬信號[4]。

本設計引入FPGA從模塊對高分辨率圖像進行緩存,并根據VGA接口時序,把LCD接口信號轉換成XVGA接口信號輸出,同時可以利用FPGA內異步FIFO解決不同時鐘域間通信速率匹配的問題。

3.2 FPGA從模塊的設計

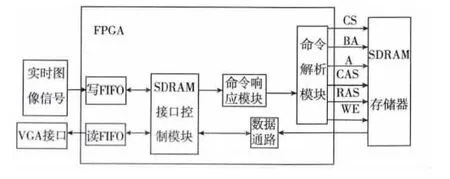

FPGA從模塊的重點是實現對SDRAM的讀寫控制,本文借助FPGA內部的邏輯資源設計SDRAM控制器實現SDRAM讀寫控制,達到用SDRAM緩存高分辨率實時圖像的目的。

3.2.1 SDRAM 控制器

本文借助FPGA片內的2個異步FIFO作為SDRAM的讀寫緩存。SDRAM控制器結構圖如圖3所示。

圖3 SDRAM控制器結構圖

SDRAM控制器主要由接口控制模塊、數據通路模塊與命令解析模塊、命令響應模塊組成[5]。各模塊功能為:

1)接口控制模塊:SDRAM初始化完成后,用戶可以通過控制器的接口模塊輸入指令控制SDRAM數據的讀寫。

2)命令響應模塊:響應外部讀寫要求并產生狀態指令給命令解析模塊。

3)命令解析模塊:命令解析模塊用于接收狀態指令并生成合適的操作命令給SDRAM存儲器。

4)數據通路模塊:負責對SDRAM進行數據讀寫,使數據按照一定的時序有效地寫入寫出。

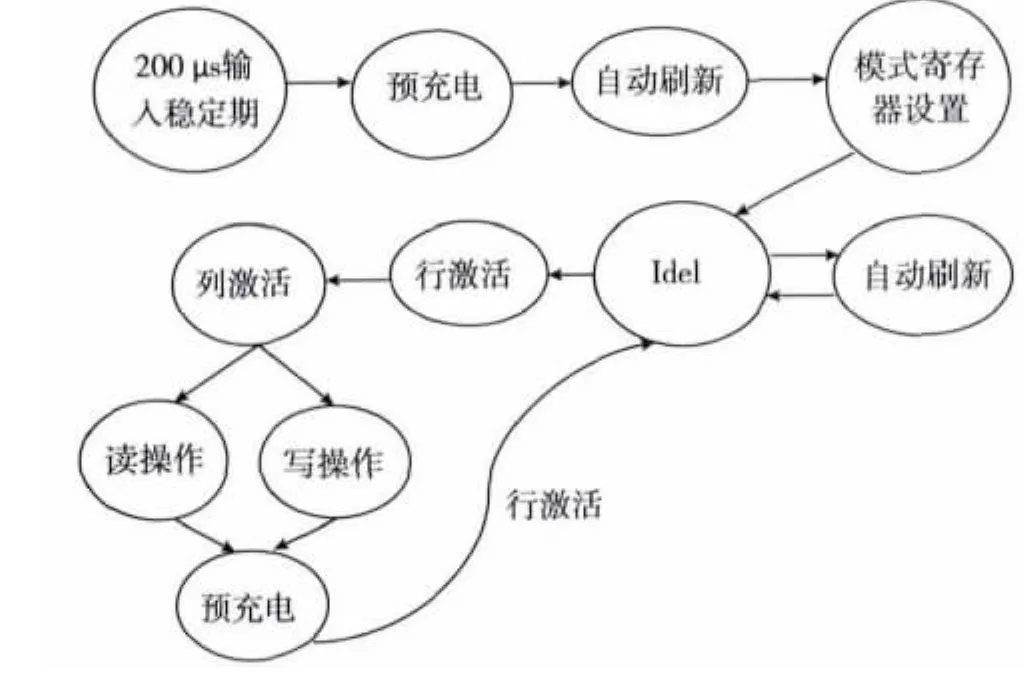

本方案的SDRAM采用頁模式突發讀寫方式以提高SDRAM的數據吞吐量。根據SDRAM的寄存器特點,FPGA對SDRAM的讀寫控制如圖4狀態機所示[6]。FPGA從模塊使用Verilog HDL硬件描述語言實現。

圖4 SDRAM控制器狀態機圖

3.2.2 SDRAM控制器的實現及時序仿真

用Verilog語言在Quartus9.0的開發環境中進行仿真,并通過Modelsim工具對SDRAM的工作狀況進行仿真驗證[7],圖5、圖6、圖7分別為SDRAM 在初始化、突發寫、突發讀時的工作時序。其中SDRAM_CMD包括:[4]CKE,[3]CS,[2]RAS,[1]CAS,[0]WE。初始化過程依次發出了將近200 μs的空閑狀態、預充電、自動刷新和模式寄存器設置等命令;寫過程依次發送激活、寫命令以及一些時間要求(tRCD,tRCD,tRP);讀過程依次發出激活、讀命令以及一些時間要求(tRCD,CAS Latency,tAC,tRP)。

圖5 SDRAM初始化時序時序仿真圖(截圖)

3.3 VGA驅動設計方案

圖6 SDRAM寫時序寫時序仿真圖(截圖)

圖7 SDRAM讀時序仿真圖(截圖)

在FPGA從模塊中,把緩存在SDRAM中的LCD接口信號送到FPGA片外的權電阻網絡進行模數轉換就能送往VGA接口顯示。VGA顯示是借用了S3C2440自帶的LCD控制器功能實現的,只要根據VGA時序修改LCD控制器相關寄存器即可,這和普通的TFT液晶屏的驅動類似,此方式在很大層面上降低了VGA驅動開發的難度。

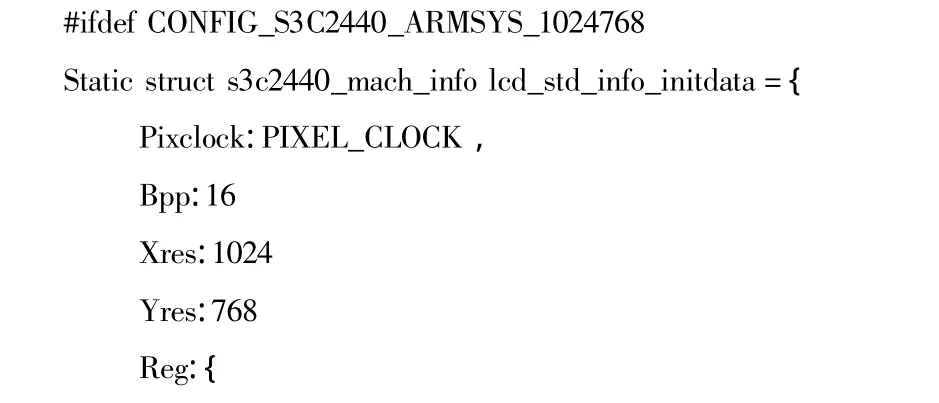

在本設計中S3C2440A的HCLK=100 MHz,VCLK=40 MHz,根據公式VCLK=HCLK/[(CLKVAL+1)×2],故需設置CLKVAL=0.25。VSYNC(幀頻)的計算式為Frame_Rate=1/{[(VSPW+1)+(VBPD+1)+(LINEVAL+1)+(VFPD+1)]×[(HSPW+1)+(HBPD+1)+(HFPD+1)+(HOZVAL+1)]×[2×(CLKVAL+1)/(HCLK)]},則幀頻為25.78 Hz,經過 FPGA 從模塊的SDRAM高速緩存后,幀頻可以達到60 Hz,分辨率是1 024×768。根據XVGA顯示時序特點,配置S3C2440A的 LCD 控制寄存器 LCDCON1 ~ LCDCON5[8],就能實XVGA輸出。相關寄存器設置如下LCD初始化代碼所示。

由于Linux2.6.30內核已經很好地支持了LCD顯示,因此,驅動并不需要重新編寫,只要進行適當的修改。打開內核源代碼,找到arch/arm/mach-s3c2440/machsmdk2440.c文件,修改LCD的初始化代碼,包括寄存器的初始值、LCD的長寬等。LCD初始化代碼修改部分如下所示:

修改好LCD初始化代碼后,重新編譯內核并生成內核鏡像zImage,然后復制內核鏡像zImage到/tftpboot/目錄中。

4 系統效果測試驗證

編譯內核并生成內核鏡像,然后將內核鏡像移植入本便攜式顯示系統開發板中。將便攜式顯示系統與投影儀相連接,對本便攜式顯示系統進行測試論證。圖8是本便攜式視頻展示臺的投影效果驗證截圖,輸出分辨率為1 024×768,60 Hz。通過觀察測試結果,本方案切實可行,對實物、圖片、文檔或者過程的顯示效果清晰,無抖動、無卡頓。

圖8 便攜式視頻展示臺的效果(截圖)

5 小結

根據市場對視頻展示臺的大量需求但價格貴、功耗高的現狀,提出了基于ARM9+FPGA的便攜式視頻展示臺的設計方案。本方案充分發揮ARM和FPGA各自的特性,在實現便攜式視頻展示臺體積小、低成本和低功耗的基礎上,最大限度地實現圖像的高清流暢顯示。ARM9主控制模塊利用自身攜帶的Camera接口和LCD控制器,實現了高清圖像的采集和圖像數據在ARM9主控模塊和FPGA從模塊模塊之間的并行傳輸,提高了傳輸速度。FPGA從模塊設計了一種SDRAM控制器,實現了高分辨率圖像實時顯示,也解決了在多個時鐘域間進行信號通信的問題。方案采用模塊化的設計原則,降低了開發成本和難度。

:

[1]張挺飛,樊永生,孫凌云.基于FPGA+ARM的智能圖像門控系統[J].電視技術,2012,36(17):156-158.

[2]樊圍棟,石紅瑞,張健.嵌入式LINUX下CMOS攝像頭驅動的設計與實現[J].工業儀表與自動化裝置,2010(3):68-70.

[3]李亞峰,歐文盛.ARM嵌人式Linux系統開發從入門到精通[M].北京:清華大學出版社,2007.

[4]廖永清,丁旭昌,付建國,等.基于FPGA的VGA圖像動態顯示控制器的設計與實現[J].電視技術,2011,35(17):52-54.

[5]劉冬,焦明華,程飛龍.基于可編程邏輯器件的高速SDRAM控制器的實現[J].電腦知識與技術,2012,32(8):7816-7825.

[6]侯宏錄,張文芳.基于FPGA的SDRAM 控制器設計方案[J].兵工自動化,2012,31(2):57-60.

[7]向厚振,張志杰,王鵬.基于FPGA視頻和圖像處理系統的FIFO緩存技術[J].電視技術,2012,36(9):41-43.

[8]尹柱霞,鄭喜鳳,于洪濤.ARM+FPGA控制的LED脫機屏系統設計[J].液晶與顯示,2010,25(2):262-266.

Design of Portable Video Showcase Based on ARM9 and FPGA

LIANG Haodong,ZHANG Guoping

(School of Physics and Technology ,Central China Normal University,Wuhan 430079,China)

Currently,portable video showcases on the market usually have big energy consumption and high cost.To solve this problem,a new kind of portable video showcase based on ARM9 and FPGA embedded real-time image processing platform is put forward.ARM9’s high performance,low power consumption,low cost and other characteristics are taken full advantage in this scheme.As the ability of FPGA which can transport and process high-resolution images is combined,the designed portable video showcase have some characteristics,such as small,easy to carry,low energy consumption,low cost,high definition display and so on.Additionally,the Linux device driver design of each module is discussed in detail.

portable video showcase;Linux;LCD controller;SDRAM controller;VGA timing

TP302.1;TP391

A

【本文獻信息】梁皓東,張國平.基于ARM9+FPGA的便攜式視頻展示臺的設計[J].電視技術,2014,38(3).

湖北省自然科學基金項目(2012FFC023)

梁皓東(1988— ),碩士生,主研嵌入式系統設計,嵌入式linux驅動開發;

張國平(1969— ),教授,博士生導師,主研光通信、光電子技術、圖像處理、認知無線電。

責任編輯:魏雨博

2013-06-26