多核DSP的多路同步時鐘信號設(shè)計

汪安民,韓道文

(1. 同方電子科技有限公司研究所,九江 332009;2. 解放軍電子工程學(xué)院)

?

多核DSP的多路同步時鐘信號設(shè)計

汪安民1,韓道文2

(1. 同方電子科技有限公司研究所,九江 332009;2. 解放軍電子工程學(xué)院)

多核數(shù)字信號處理器(DSP)具有豐富的外設(shè)接口,每個外設(shè)接口具有各自獨立的參考時鐘。由于多核DSP具有較快的數(shù)據(jù)處理能力,對外設(shè)接口的時鐘要求較高。當(dāng)多個接口協(xié)同工作時,對時鐘的同步要求較高。本文介紹了多核數(shù)字信號處理器TMS320C6678的時鐘設(shè)計,通過時鐘芯片CDCM6208提供多路不同工作頻率的時鐘信號到DSP,文中介紹了時鐘芯片的初始化和設(shè)置以及詳細(xì)的軟硬件設(shè)計方法。

多核DSP;時鐘;CDCM6208

引 言

多核處理器是最近快速發(fā)展的電子器件,單個芯片內(nèi)集成了多個同構(gòu)或者異構(gòu)的處理器,使得其計算處理能力得到較大幅度的提高。DSP處理器由于其具有較高的數(shù)字處理能力,得到較廣泛的應(yīng)用。多核DSP芯片以目前性能較高的TMS320C66系列為例,其中TMS320C6678(以下簡稱C6678)含有8個處理器。這些處理器可以獨立工作,也可以并行聯(lián)合工作。當(dāng)它們聯(lián)合工作時,相互之間通信和握手就非常重要,尤其是在對時間要求較高的場合,時鐘的穩(wěn)定和同步就非常關(guān)鍵。時鐘的穩(wěn)定和同步對系統(tǒng)設(shè)計、時鐘源、時鐘分配、電路布線、時鐘線屏蔽等都提出較高的要求。

本文利用CDCM6208時鐘分配芯片,以此輸出多路時鐘,提供到8核DSP芯片C6678,提供出DSP核工作時鐘、DDR3數(shù)據(jù)讀寫時鐘、RapidIO和PCIe數(shù)據(jù)傳輸時鐘、千兆網(wǎng)絡(luò)加速器等時鐘信號。文中介紹了詳細(xì)的電路設(shè)計、時鐘芯片配置以及多核DSP的配置,相關(guān)片內(nèi)設(shè)備的初始化等。

1 C6678及其結(jié)構(gòu)

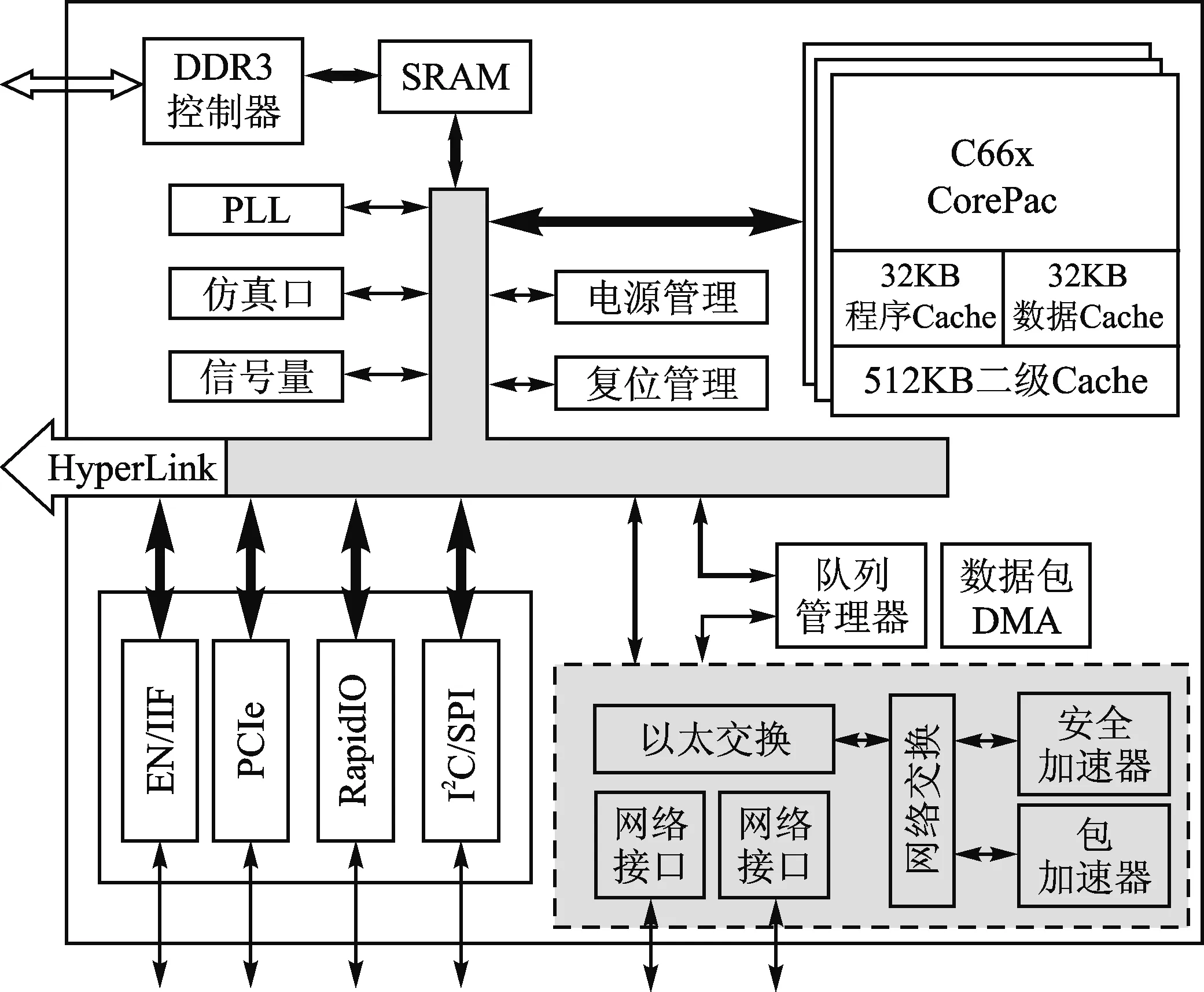

C6678是TI公司多核處理器中的一款8核浮點型DSP,最高工作頻率達(dá)到1.25 GHz,單核可以提供40 GMAC定點計算或者20G FLOP浮點計算能力,單個芯片可以提供320G MAC或者160G FLOP計算能力。C6678的片內(nèi)結(jié)構(gòu)如圖1所示。

圖1 C6678內(nèi)部結(jié)構(gòu)圖

C6678的每個核具有32 KB的程序、32 KB的數(shù)據(jù)以及512 KB的2級Cache存儲空間,芯片片內(nèi)具有一個4 MB的共享SRAM。C6678具有DDR3控制器接口,可以外接DDR3,直接尋址范圍達(dá)到8 GB。C6678的片內(nèi)外設(shè)有RapidIO、PCIe、EMIF以及SPI、I2C總線等接口。這些接口通過片內(nèi)的高速互聯(lián)總線和各個處理器交互數(shù)據(jù)。

和網(wǎng)絡(luò)相關(guān)的片內(nèi)設(shè)備如圖1右下角灰色模塊所示,主要包括兩個對外的SGMII接口、以太交換和網(wǎng)絡(luò)交換模塊,以及用于數(shù)據(jù)管理的安全加速器和包加速器,是為了快速檢測數(shù)據(jù)的校驗以及協(xié)議是否遵循網(wǎng)絡(luò)標(biāo)準(zhǔn),對于錯誤的數(shù)據(jù)直接丟棄,降低CPU的負(fù)擔(dān)。為了加快網(wǎng)絡(luò)和CPU的數(shù)據(jù)交換,片內(nèi)的隊列管理器用于管理網(wǎng)絡(luò)包或者網(wǎng)絡(luò)幀的緩存,分發(fā)等功能。這些數(shù)據(jù)都采用數(shù)據(jù)包DMA讀/寫,不需要CPU參與。

C6678的其他片內(nèi)設(shè)備包括PLL、仿真口、信號量、電源管理和復(fù)位管理等模塊。其中PLL配置CPU和外設(shè)的工作時鐘;仿真口用于連接仿真器,實現(xiàn)對軟件運行的監(jiān)控;信號量實現(xiàn)對DSP/BIOS操作系統(tǒng)中信號量的控制;電源管理實現(xiàn)整個芯片電流電壓的控制;復(fù)位管理配置啟動的方式,硬復(fù)位進(jìn)行全啟動,軟復(fù)位進(jìn)行部分啟動。

2 CDCM6208及其結(jié)構(gòu)

CDCM62xx系列芯片是TI公司針對多核處理器專門開發(fā)的時鐘產(chǎn)生、驅(qū)動和分配芯片。CDCM6208是該系列的第二代產(chǎn)品,相比于第一代CDCM6208的最大優(yōu)點就是功耗大幅度降低,從第一代的2~3 W降低到0.5 W左右。而其功能、指標(biāo)和體積沒有弱化。CDCM6208有兩路可選時鐘輸入,8路時鐘輸出。8路輸出中的4路只能做整數(shù)倍分頻,另外4路可以做小數(shù)倍分頻,滿足多核芯片的各種不同的時鐘需求。8路時鐘支持LVPECL、CML、HCSL以及LVDS信號電平,最大支持800 MHz的時鐘頻率,滿足RapidIO和PCIe這些高速接口需求。時鐘抖動小于265 fs。其控制可以通過標(biāo)準(zhǔn)的SPI或者I2S接口實現(xiàn),非常方便靈活。TI公司提供針對該芯片專門開發(fā)的圖形化控制軟件,用戶選擇所要設(shè)置的時鐘工作方式、輸出頻率等參數(shù),該軟件生成其內(nèi)部寄存器的值,通過SPI或I2S接口寫入就完成整個芯片的配置。

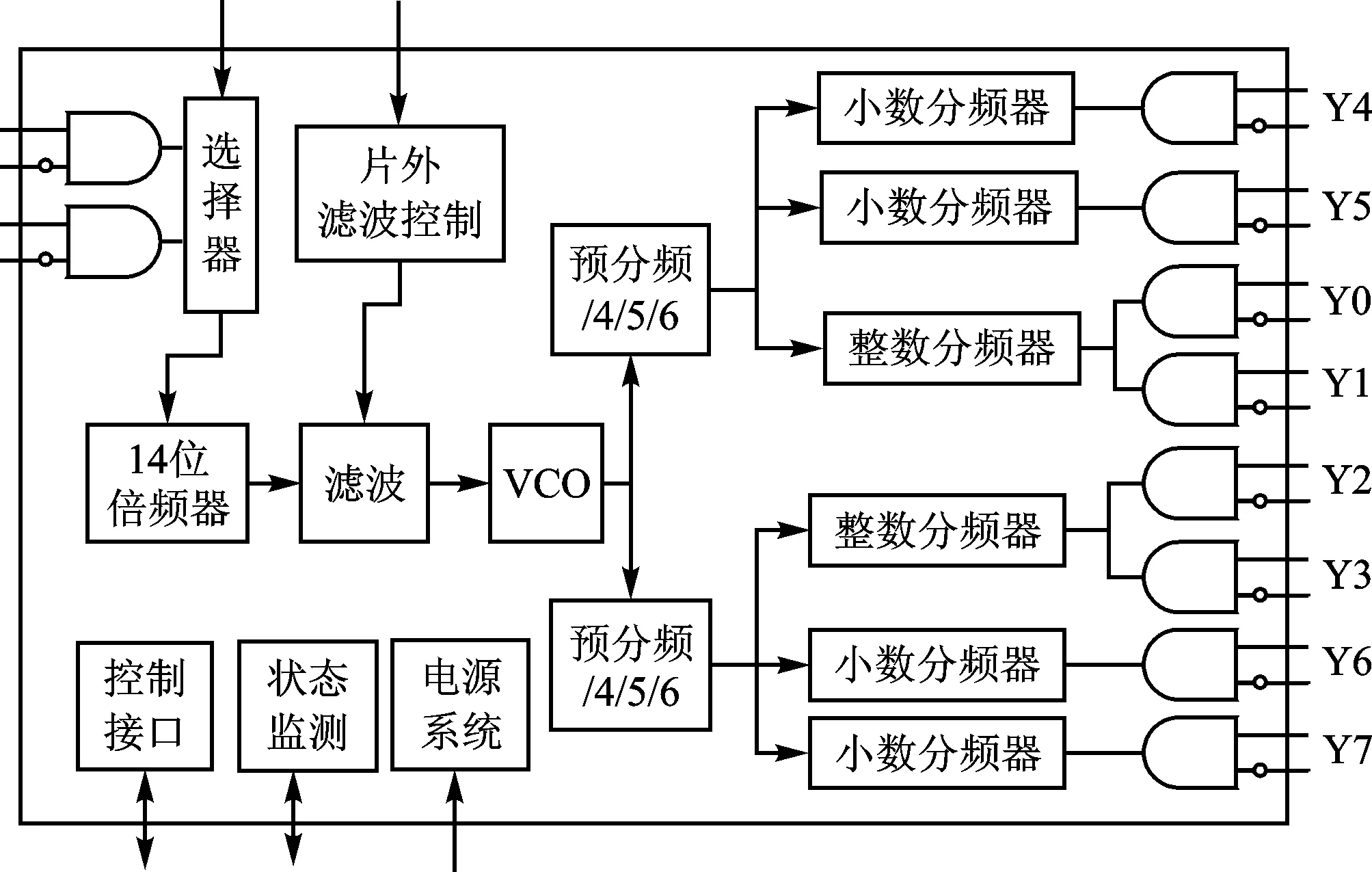

CDCM6208的內(nèi)部結(jié)構(gòu)如圖2所示。從圖中可以看出,可選兩路時鐘輸入后,首先經(jīng)過一個14倍頻器,作為參考時鐘驅(qū)動片內(nèi)VCO產(chǎn)生時鐘信號。為了提高時鐘相位噪聲,倍頻后信號經(jīng)過一個片內(nèi)的濾波器,該濾波器可以由片內(nèi)提供阻容電路設(shè)置。VCO時鐘功分到兩路預(yù)分頻器,預(yù)分頻器只能4、5或者6分頻。預(yù)分頻后時鐘再次進(jìn)入后期的分頻器。每個預(yù)分頻器功分到兩個小數(shù)分頻器和一個整數(shù)分頻器。分頻后信號驅(qū)動后輸出。從圖2右邊輸出可以看出,整數(shù)分頻器輸出的Y0和Y1兩路時鐘頻率一樣,Y2和Y3時鐘頻率一樣。小數(shù)分頻的Y4~Y7可以各自設(shè)置。CDCM6208的這種時鐘配置限制了其應(yīng)用,但好處是降低了功耗,目前這種配置滿足絕大部分多核處理器的要求,尤其是TI公司的C66系列以及AK2系列多核DSP可以實現(xiàn)無縫連接。

圖2 CDCM6208內(nèi)部結(jié)構(gòu)圖

3 硬件設(shè)計

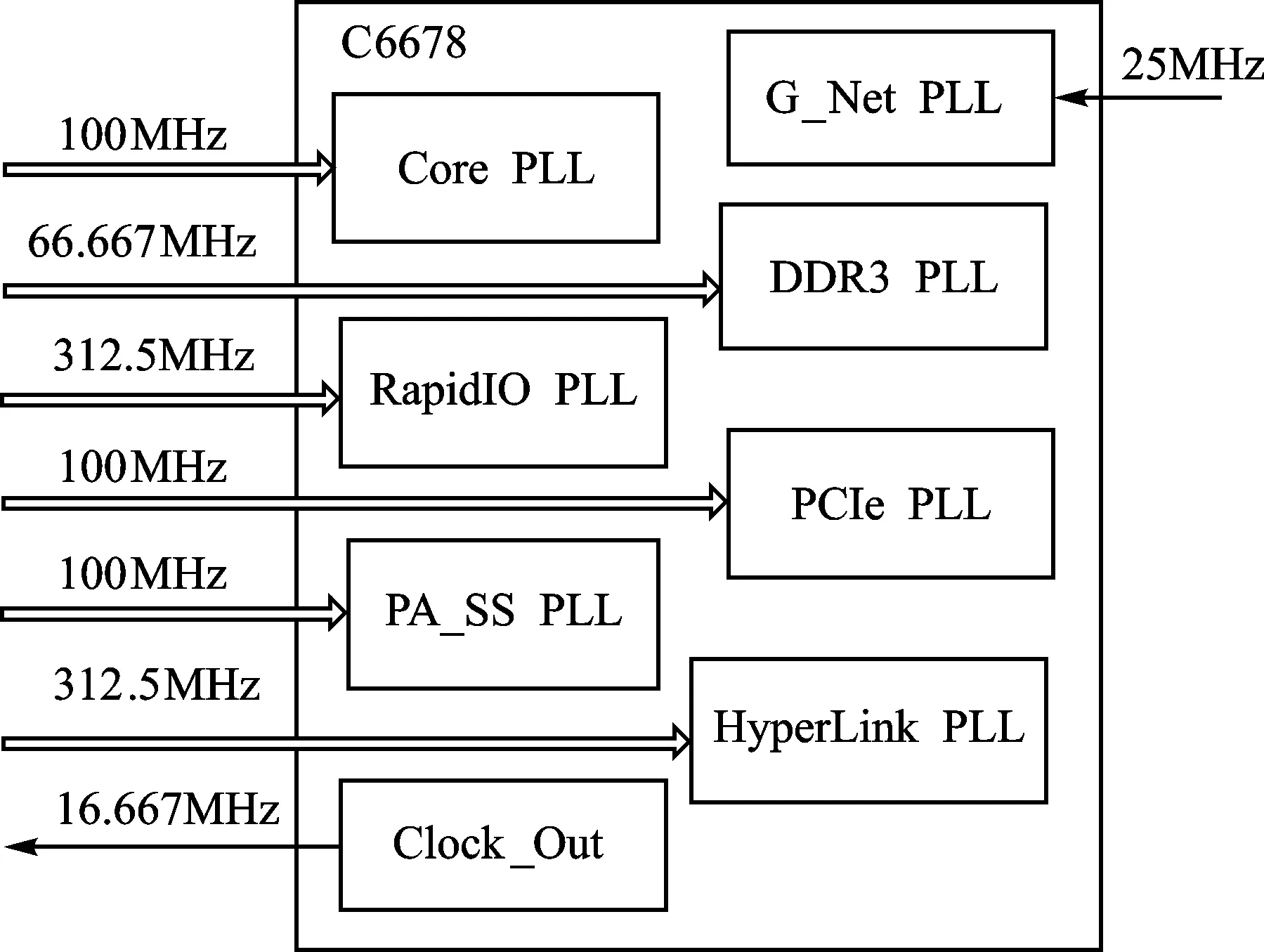

根據(jù)TMS320C6678的應(yīng)用,所需要的時鐘如圖3所示。

圖3 C6678的時鐘信號

其主要時鐘包括:①內(nèi)核運行時鐘,該時鐘輸入是100 MHz,DSP片內(nèi)PLL將其鎖定到工作頻率,最高為1 GHz,最低為700 MHz。②RapioIO接口和HyperLink超級連接接口工作時鐘,這兩路時鐘輸入都為312.5 MHz,RapioIO倍頻4、8、10、16,工作在1.25 GHz、2.5 GHz、3.125 GHz和5 GHz。HyperLink倍頻到40、80、100、160,工作在12.5 GHz、25 GHz、31.25 GHz和50 GHz。③PCIe接口時鐘和PA_SS網(wǎng)絡(luò)加速器時鐘,這兩路時鐘都是輸入100 MHz,內(nèi)部倍頻后相應(yīng)的工作時鐘,滿足各自接口傳輸時鐘要求。④DDR3時鐘,該時鐘輸入為66.667 MHz,倍頻20或者25倍,工作在1333.33 MHz或者1666.7 MHz。這些時鐘在DSP片內(nèi)都各有獨立的PLL電路設(shè)置,其工作原理和設(shè)置方法基本一致。圖3中的單獨25 MHz是專門為千兆網(wǎng)提供的工作時鐘,由一個單獨的晶體提供。C6678還提供一路時鐘輸出信號,默認(rèn)輸出為核時鐘的1/6,圖中為16.667 MHz,輸出時鐘可以檢測C6678是否正常工作。

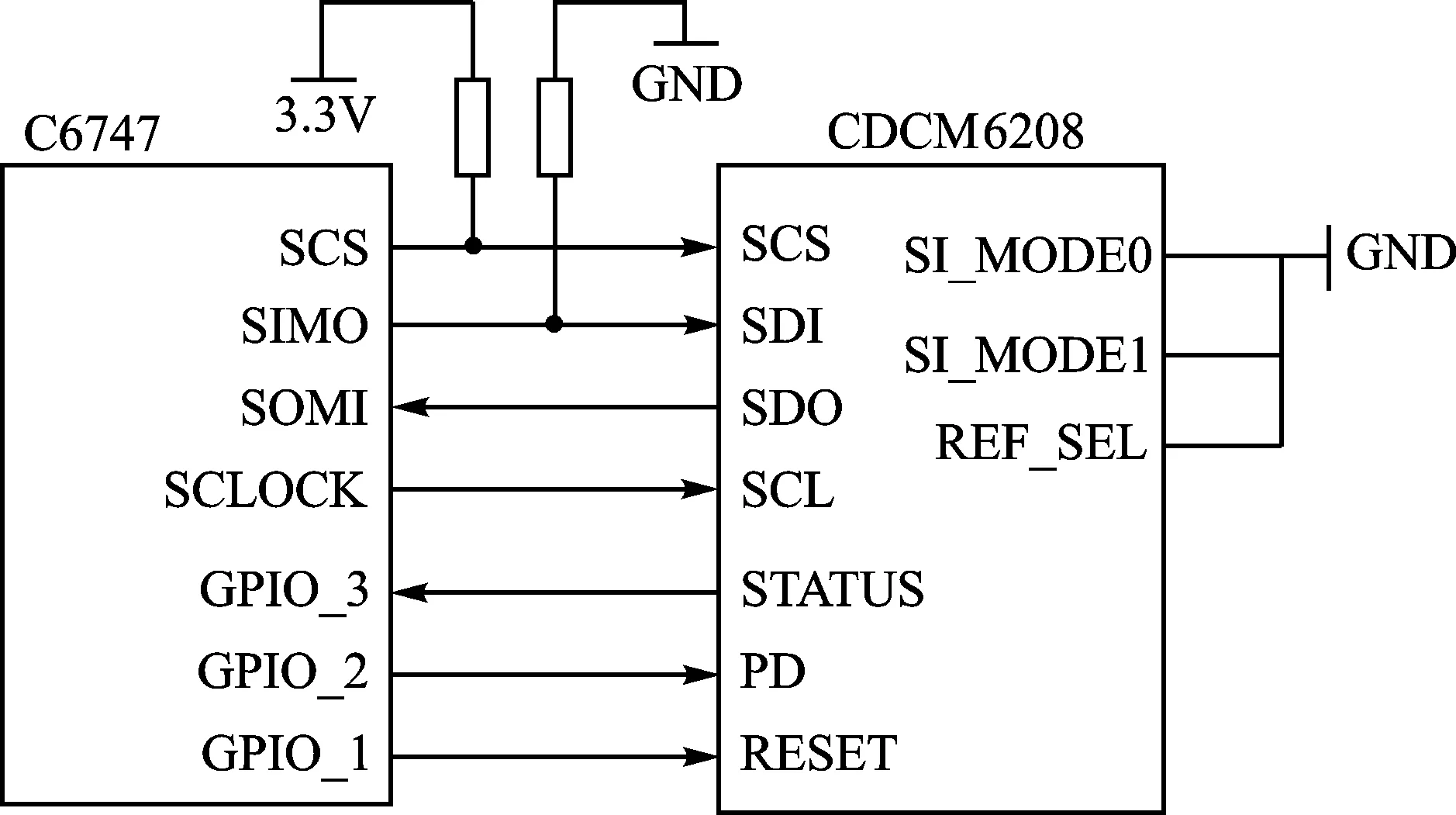

由于C6678的核時鐘由CDCM6208提供,所以對CDCM6208的設(shè)置只能由另外一個處理器完成,只要該處理器具有SPI或者I2S接口即可。本文使用低功耗的DSP芯片C6747來實現(xiàn)多CDCM6208的設(shè)置。C6747和CDCM6208的接口如圖4所示,采用標(biāo)準(zhǔn)4線制SPI接口控制,為了避免干擾提高傳輸可靠性,在SPI的片選信號的寫信號分別上拉和下拉,這樣在空閑下其引腳狀態(tài)不會被干擾。在控制CDCM6208之前,需要對其進(jìn)行復(fù)位,圖中使用一個通用GPIO引腳控制,當(dāng)CDCM6208配置成功后,會提供一個狀態(tài)檢測信號,該信號連接到C6747的GPIO引腳,用來判斷是否正確配置。圖中C6747還使用一個引腳控制CDCM6208的低功耗設(shè)置,當(dāng)該引腳為高時,CDCM6208進(jìn)入低功耗模式。

圖4 C6747和CDCM6208的接口

4 軟件設(shè)計

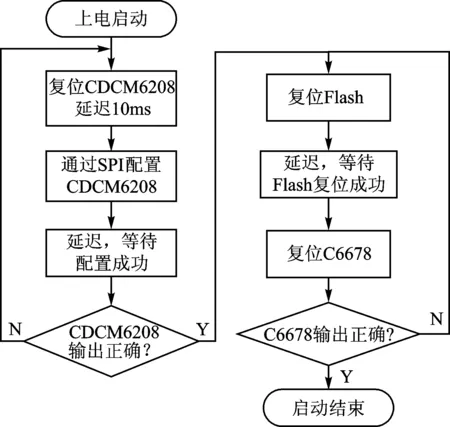

由于系統(tǒng)采用C6747控制CDCM6208時鐘信號,所以C6747的軟件是系統(tǒng)整個初始化的關(guān)鍵,C6747的初始化軟件主要包括對CDCM6208的復(fù)位、配置和檢測以及對C6678的復(fù)位、C6678外掛Flash的復(fù)位等工作。整個系統(tǒng)的軟件流程如圖5所示。

圖5 軟件流程

上電啟動后,C6747軟件加載成功后,復(fù)位CDCM6208,為確保復(fù)位成功,C6747要等待10 ms才能通過SPI接口配置CDCM6208。配置完成后,C6747可以查詢CDCM6208的狀態(tài)輸出引腳,檢測是否配置成功。如果配置失敗,重復(fù)復(fù)位、配置、檢測這幾個步驟。配置成功后,表明CDCM6208已經(jīng)輸出準(zhǔn)備時鐘到C6678,但在此之前,C6678仍然處于復(fù)位狀態(tài)。由于C6678的程序保存在片外Flash中。所以,C6747要首先復(fù)位Flash,等待其復(fù)位后,再復(fù)位C6678,查詢C6678的輸出狀態(tài),確定C6678是否正常工作。如果輸出不正常,仍然重復(fù)復(fù)位Flash、復(fù)位C6678和檢測這幾個步驟,直到初始化成功。

結(jié) 語

[1] 丁有源,汪安民.基于多核任務(wù)并行處理的DSP軟硬件設(shè)計[J].單片機(jī)與嵌入式系統(tǒng)應(yīng)用,2012(5).

[2] Texas Instruments Inc. Clocking Design Guide for KeyStone Devices,2012.

[3] Texas Instruments Inc. 2:8 Clock Generator, Jitter Cleaner With Fractional Dividers (Rev. D) CDCD6208 Datasheet,2012.

Synchronous Multi-clocks Based on Multicore DSP

Wang Anmin1, Han Daowen2

(1. Research of Tongfang Science and Technology Ltd., Jiujiang 332009, China ;2. Electronic Engineering Institute of PLA)

These are many interfaces on multicore DSP, and each clock should be set independently. Higher frequency and steadiness is required for these clocks to fit the multicore DSP. These clocks are originated from one high precision reference clock. TMS320C6678 clock design is introduced, getting diversified clock based on CDCM6208. The paper introduces how to set CDCM6208, and the design of hardware and software is described.

multicore DSP;clock;CDCM6208

TP336

A

珍

2013-11-22)