基于FPGA和NIOS的慣導組件測試系統研究

張志文,彭 彥

(西安工業大學電子信息工程學院,西安710032)

基于FPGA和NIOS的慣導組件測試系統研究

張志文,彭 彥

(西安工業大學電子信息工程學院,西安710032)

針對慣導組件產品測試中多種信號輸出的測量需求,設計了一種基于FPGA和NIOS II軟核的雙模式慣導組件數據采集系統。該系統以FPGA和USB CY7C68013芯片為核心,實現對4個慣導組件輸出的48路脈沖進行頻率計數和對8個慣導組件輸出8路串口數據的接收,最后通過USB芯片將采集得到的數據上傳至測控計算機,并由計算機進行保存、處理和顯示。該設計降低了采集電路復雜度,提高了產品測試效率和采集系統的可靠性、穩定性。

慣導組件;現場可編程門陣列;NIOS II軟核;USB芯片;數據采集

1 引 言

慣性導航系統的核心是慣導組件,通常由陀螺儀和加速度計組成。慣導組件在投入使用前要經過嚴格測試,測試平臺一般為一個帶溫箱的三軸轉臺,將慣導組件固定在轉臺上,通過改變轉臺的位置和速率,并在不同溫度下進行測試,從而得到慣導組件的各種狀態信息。這些信息以脈沖或串口數據的形式輸出,由采集系統進行測量或接收,然后由計算機進行處理得到慣導組件的特性參數。慣導組件的測試需在不同溫度下進行多次測試,不同溫度點還需要保溫和冷卻,通常需要數天時間,因此需要一個可靠、穩定的慣導組件數據采集系統。通常國內慣導組件測試系統都是使用PCI卡來采集數據,并需要脈沖和串口兩種采集卡,這種采集卡通常價格較貴,采集路數有限,還需計算機支持相應的PCI插槽[1],采集電路也較復雜,數據傳輸出錯時也不易排查原因。

針對這種情況,提出了一種基于FPGA和NIOS軟核的設計方案,集成脈沖測量和串口數據接收于同一系統。基于FPGA設計了脈沖計數采集電路,并在FPGA中建立一個帶有多個串口模塊的NIOS II軟核處理器,控制脈沖和串口數據的采集,最后利用USB芯片將數據上傳到計算機中處理。

2 系統方案設計

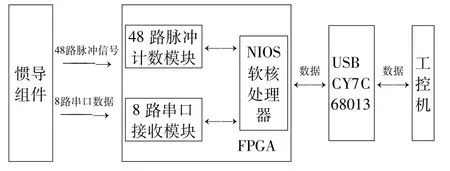

根據慣導組件數據采集系統的要求,既能對4個慣導組件輸出的48路脈沖信號(每個慣導組件輸出6路陀螺儀信號和6路加速度計信號)進行頻率計數,又能接收經過導航計算機板處理過的8個慣導組件輸出的串口數據。因此是一個多模式的數據采集系統,采集系統結構框圖如圖1所示。

圖1 采集系統結構框圖

在上圖中,FPGA芯片采用了ALTERA公司的CycloneⅢEP3C16Q240C8型號芯片。該芯片內部擁有15408個邏輯單元、支持20個全局時鐘網絡和4個鎖相環,并支持多種外設接口[2],完全滿足系統邏輯設計需求。48路脈沖計數模塊通過Verilog語言編寫完成,8路串口數據接收模塊通過在NIOS II軟核處理器中構建8個UART外設核來實現。NIOS II軟核通過定時器每5ms讀取一次脈沖計數器的計數值,然后通過CY7C68013 USB芯片發送到上位機。串口數據通過設定好波特率的UART核來接收,NIOS II軟核通過中斷方式接收串口數據并存儲,同樣通過USB芯片發送到上位機。上位機用VC++6.0設計MFC應用程序,接收USB芯片發送上來的數據,然后對其進行保存、處理和顯示。

3 FPGA內部邏輯設計

3.1 48路脈沖計數器設計

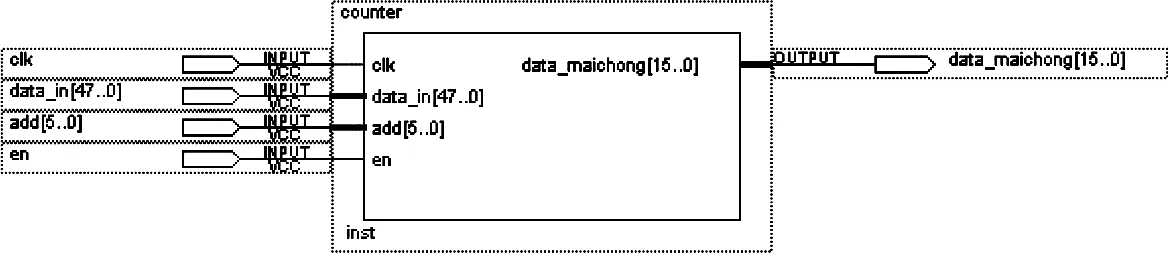

設計使用Quartus II 9.0開發軟件完成,通過Verilog語言編寫48路帶有鎖存器的16位計數器,對脈沖上升沿進行計數,NIOS II軟核處理器每5ms提供一個鎖存信號鎖存48路計數器的計數結果,并依次選通48路地址讀取計數值保存,然后發送到USB芯片的FIFO再上傳給上位機。48路計數器模塊如圖2所示,data_in為48路脈沖信號輸入,add為選通地址,en為鎖存信號。data_maichong為上傳的脈沖計數值。

圖2 48路脈沖計數器模塊圖

3.2 NIOS II軟核及8路串口模塊設計

使用集成于Quartus II軟件中SOPC Builder工具可以很方便構建Nios II軟核。本系統中FPGA外設使用了HY57V641620FTP-6的SDRAM芯片作為數據存儲器和EPCS4芯片作為程序存儲器,由此軟核需要構建的模塊有:CPU處理器、EPCS控制器、SDRAM控制器、定時器控制器,8個UART控制器以及其他各種IO接口[3]。

系統中要求同時接收8個慣導組件輸出的8路串口數據,所以要在軟核中構建8個UART模塊,設置好串口波特率和中斷優先級。外部電平轉換電路采用MAX488串口芯片,將422電平轉化成UART接口的TTL電平,這樣串口模塊就能完成數據的收發。通常MCU很少帶有4個以上的串口,涉及多串口通訊時不可避免要進行串口擴展,而在Nios II軟核系統中,串口數量和波特率都可以自由調整,同時串口模塊集成于FPGA內部,免去了使用多串口卡或串口擴展芯片帶來的復雜電路,使整個系統的可靠性和穩定性得到了保證。

4 USB傳輸模塊設計

USB模塊采用Cypress公司的CY7C68013A-128AXC型號的USB芯片作為該模塊的核心。該芯片集成USB2.0收發器,串行接口引擎(SIE)和增強型8051內核,并具有4KB FIFO存儲器,支持8位或16位數據接口,內部SIE可以工作在全速(12Mb/s)和高速(480Mb/s)傳輸速率下[4]。

CY7C68013與外部的接口主要有三種方式:端口模式、GPIF控制器模式和SLAVE FIFO模式。其中SLAVE FIFO模式是一種從屬模式,外部邏輯或外部處理器可以直接連接并控制FIFO端點,不需要內部8051的參與就能完成數據的高速傳輸[5]。系統選用了SLAVE FIFO接口模式與FPGA連接。由于FPGA中已經建立了NIOS軟核處理器,其工作頻率可達200MHz以上,遠超過8051內核的最高工作頻率48MHz,數據處理和傳輸完全由NIOS軟核處理器控制完成,避免了在串口波特率較高時,8051工作頻率有限情況下可能導致的數據出錯和丟失情況。

CY7C68013中包含了3個64字節的端點緩沖區(EP0、EP1IN和EP1OUT)和4KB FIFO緩沖區。FIFO中的EP2、4、6、8用于高帶寬數據傳輸,端點最大緩沖1024字節。由此采用了EP2、6兩個端點用來分別傳輸脈沖和串口數據,使用EP0端點用于上位機和FPGA之間控制命令的發送。

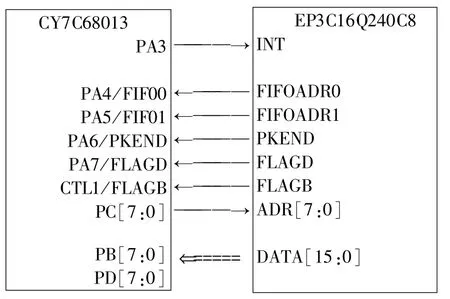

SLAVE FIFO模式下FPGA與USB的接口如圖3所示。

圖3 FPGA與USB接口連接圖

其中PA3用于提供中斷信號進入模式選擇,FIFO0和FIFO1用于選通FIFO端點,PKEND、FLAGD、FLAGB用于設定引腳的工作方式,PC[7:0](ADR[7:0])用于向FPGA發送模式選擇命令,DATA[15:0]用于發送數據。

5 系統軟件設計

系統軟件設計主要包括三部分:NIOS中下位機程序、USB固件程序和上位機應用程序。

5.1 NIOS下位機程序設計

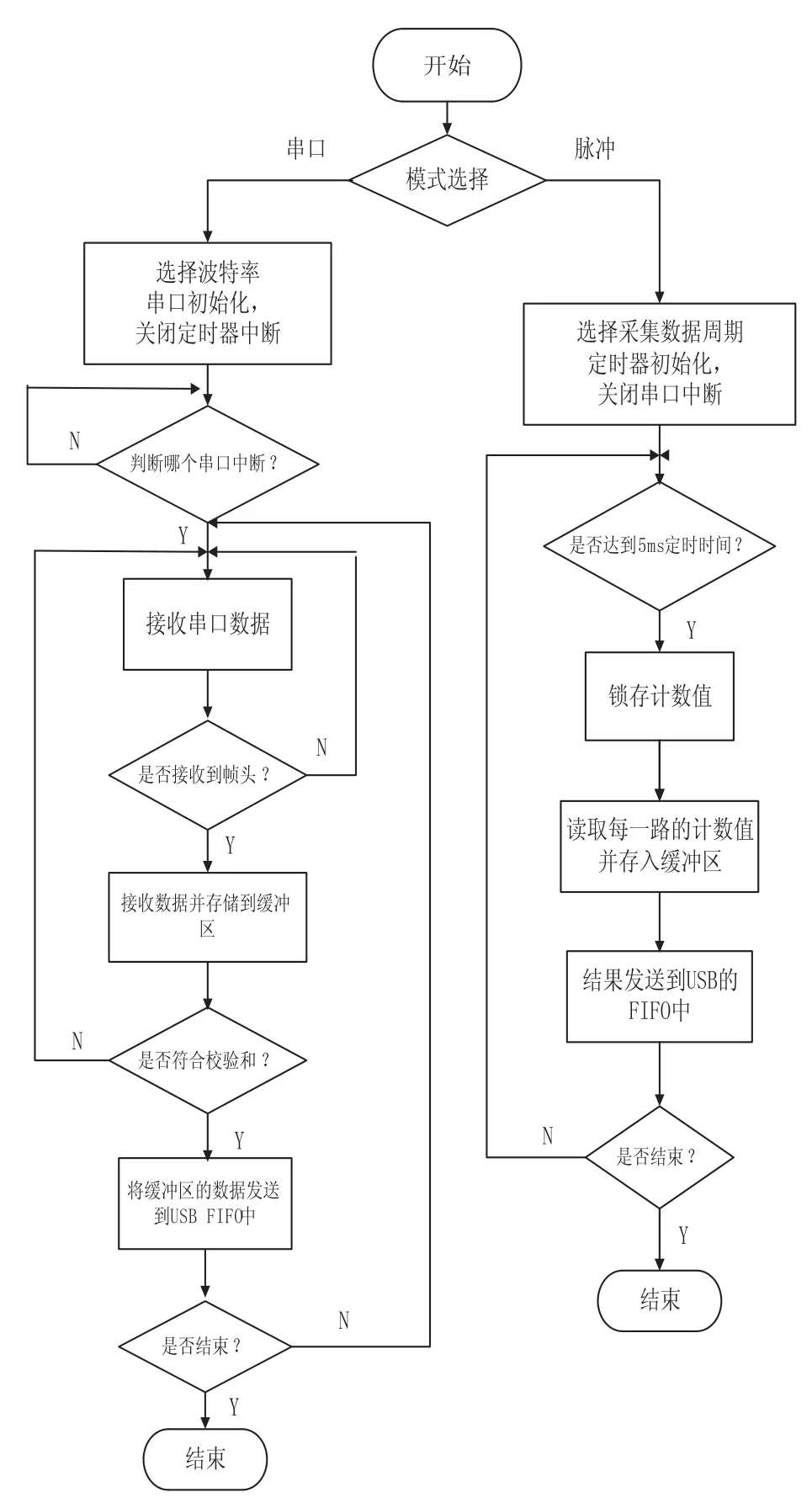

NIOS II軟核中的下位機程序是整個系統運行的核心,使用NIOS II IDE集成開發環境進行開發,主要包括三部分:模式選擇程序,脈沖數據接收程序和串口數據接收程序。

(1)模式選擇程序

選擇脈沖和串口兩種模式,另外還有采集脈沖周期和串口波特率的選擇。通過設定USB PA3腳引入一個外部PIO中斷(最高優先級)進入到中斷程序中,然后讀取PC[7:0]上的8位二進制數值,使用該值的最高位作為模式選擇判斷位(1為串口,0為脈沖),低4位代表波特率選擇,中間3位代表采集周期選擇。

(2)脈沖接收程序

依靠在軟核中建立的定時器控制器設定定時器每5ms中斷一次,進入定時器中斷服務程序后,首先用API函數向計數器寫入鎖存信號en,然后依次向計數器的選通地址端寫入48路脈沖的地址,根據該地址讀取48路脈沖計數值并分別存儲起來,最后主程序將計數值發送到USB FIFO中。

(3)串口接收程序

串口模塊要求接收8路RS-422數據,每路數據是一個49字節的數據幀,實驗中使用單片機數據源每5ms發送一次。設定頭兩個字節為幀頭,中間46個字節為慣導組件的狀態信息數據,最后一個字節為中間46字節的校驗和。8路串口數據通過中斷方式按字節進行接收,按中斷優先級的高低分別響應。接收數據時首先判斷幀頭,然后接收數據存放在緩沖區并與校驗和對比,確認無誤后主程序將數據發送到USB的FIFO中。

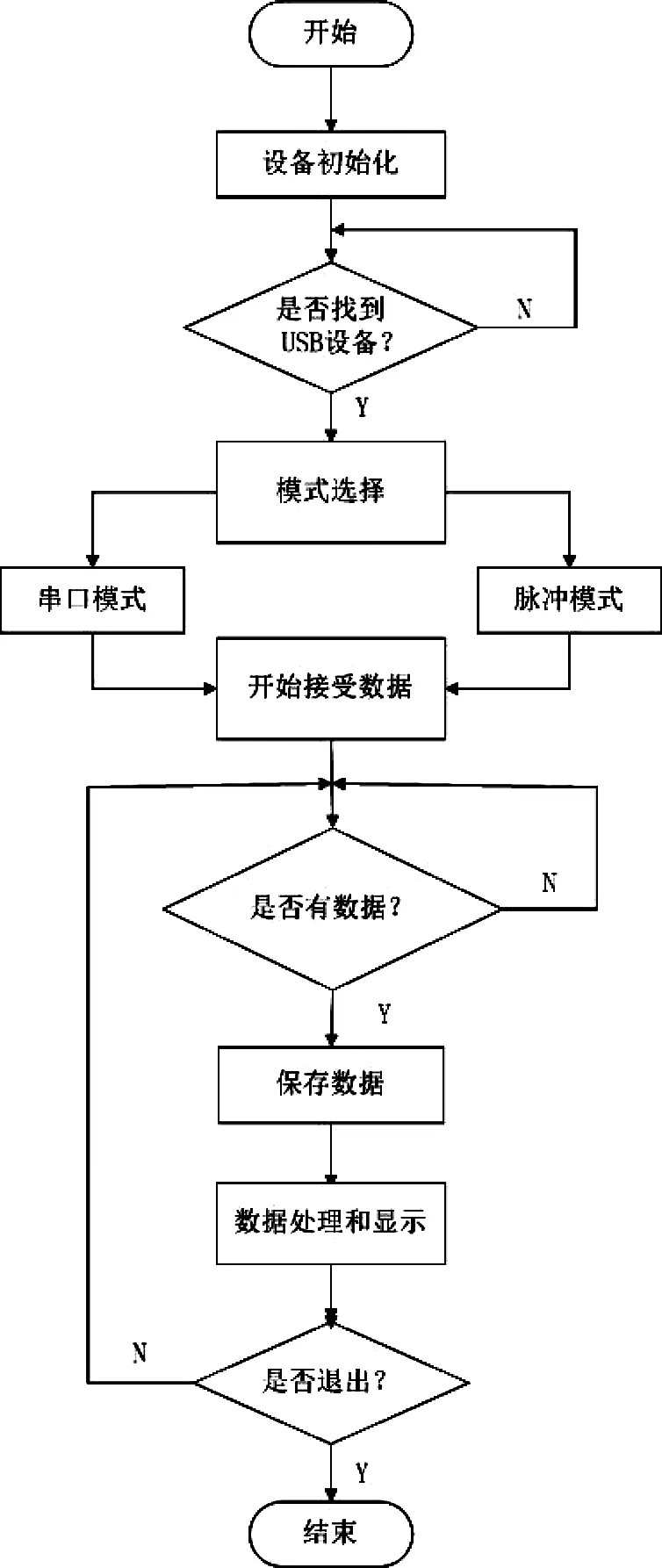

下位機程序流程圖如圖4所示。

5.2 USB固件程序設計

USB固件程序是用來控制芯片完成所設定的功能,系統中使用了CY7C68013的SLAVE FIFO接口模式。首先CY7C68013上電之后會調用TD_Init()函數來完成初始化狀態寄存器的配置[5],包括選擇接口模式、外部主控制器使能、以及端點的方向、緩沖倍數、發送方式的配置等。

下一步對各端點的FIFO進行設置,啟用EP2端點接收脈沖的數據,16位計數器48路脈沖5ms的數據量為48個字節,所以設定包的大小為960字節(最大1024字節)。啟用EP6端點接收串口的數據,下位機處理過程中對每路串口的每幀數據作了1個字節的標記,每一路變成50個字節,8路串口每5ms數據量為400字節,設定包的大小為800字節(最大1024字節)。設定程序如下所示:

EP2AUTOINLENH=0x03;

SYNCDELAY;

EP2AUTOINLENL=0xC0;//設置包大小為960字節,接收脈沖數據

SYNCDELAY;

EP6AUTOINLENH=0x03;

SYNCDELAY;

EP6AUTOINLENL=0x20;//設置包大小為800字節,接收串口數據

SYNCDELAY;

圖4 下位機程序流程圖

上位機對下位機發送命令(模式選擇等)通過Cypress標準固件框架使用控制傳輸來實現,只需在DR_VendorCmnd函數中加入處理過程即可。這部分程序可以利用自定義上位機發送的SETUPDAT令牌包來傳送8位二進制數值命令。

CY7C68013屬于EZ-USB FX2芯片系列,其配套的設備驅動程序EzUsb.inf為EZ-USB通用驅動程序(GPD),該文件包含了硬件設備驅動程序的安裝信息[6],安裝完成后計算機將獲取的USB外設信息與EzUsb.inf文件中信息進行匹配,找到相應的USB設備驅動程序。

5.3 上位機應用程序設計

上位機程序開發采用VC++6.0中的MFC進行編程開發,VC編程的應用程序利用USB總線接收數據,再由MFC實現對數據的接收、解算處理、顯示和保存。

上位機程序訪問USB設備時,首先調用Win 32函數CreateFile()來得到USB設備句柄,通過DeviceIoControl()函數訪問設備驅動程序[7],該函數發送命令到設備驅動程序,連接USB設備,然后通過USB總線接收上傳的數據。

上位機程序的流程圖如圖5所示。

圖5 上位機程序流程圖

6 實驗結果

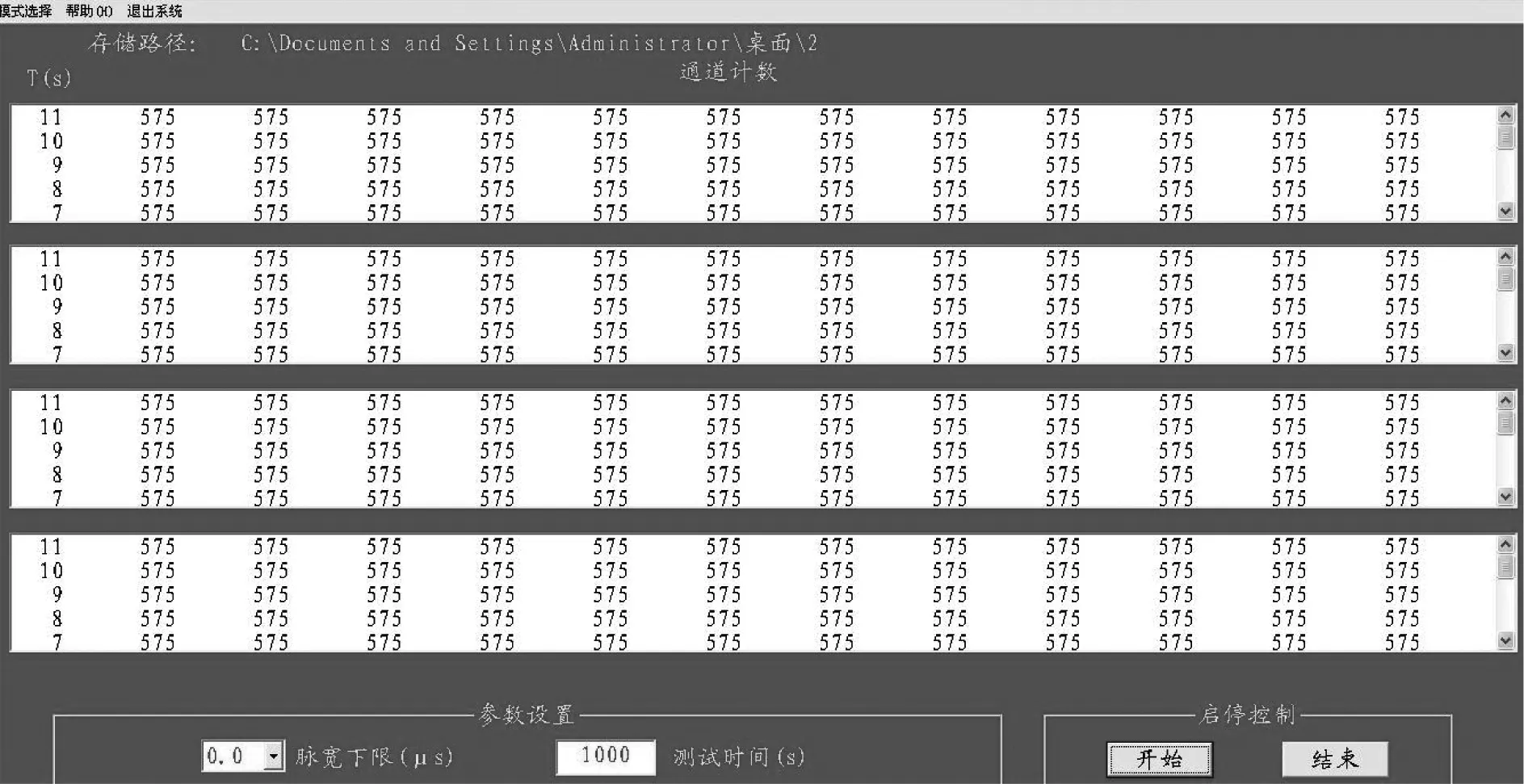

采集系統的測試在實驗室中進行,使用SP1641D信號發生器作為脈沖信號源,用多路開關板擴展為48路同源信號。信號源輸出信號為575Hz時,測量結果如圖6所示。在實驗室多次測量后發現,在低頻時脈沖計數值準確,高頻時脈沖計數值有1-2個誤差,總體誤差率在允許范圍內,符合慣導組件的測試要求。

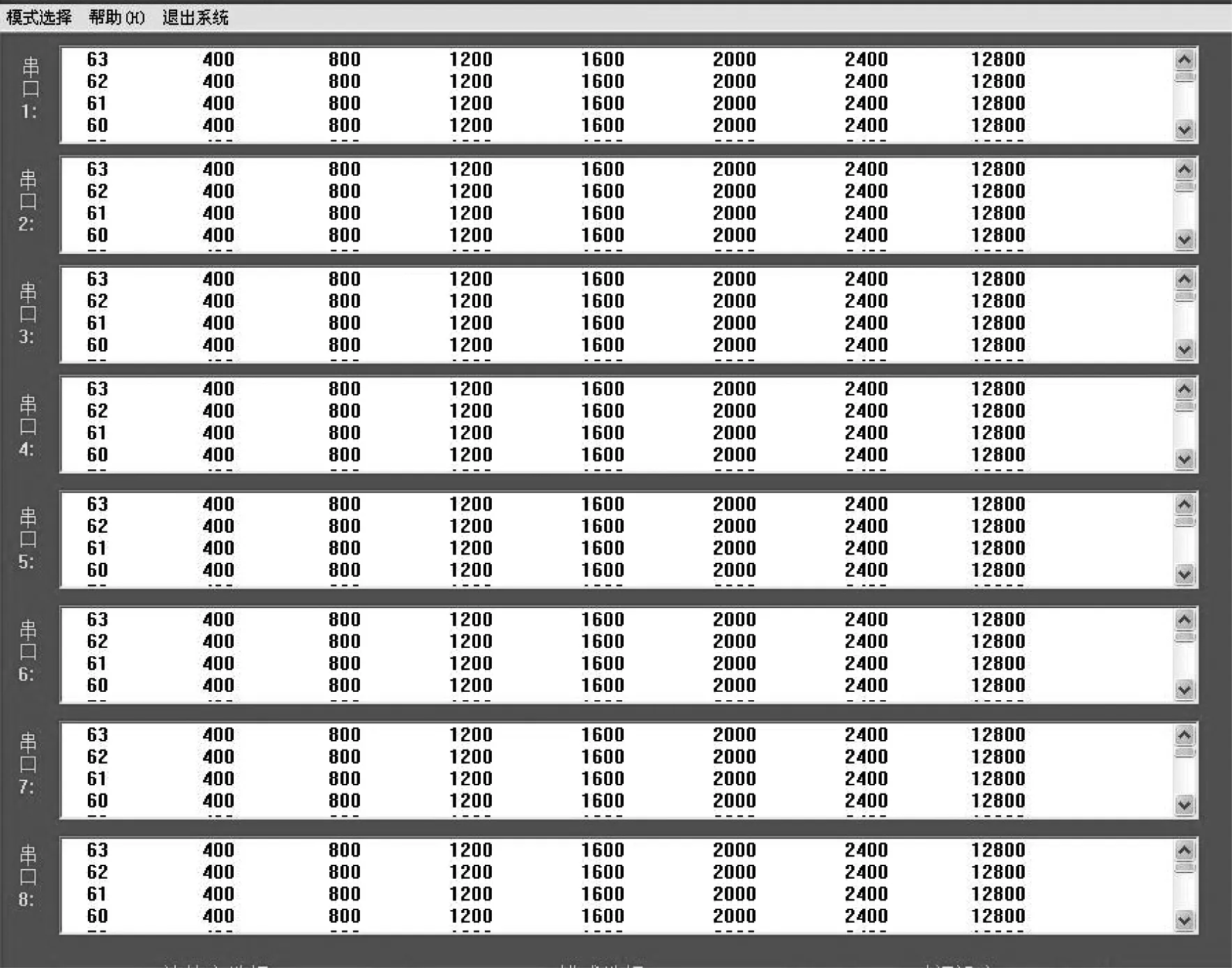

串口測試使用了ST89C52單片機構成的多串口信號發生器,可以輸出RS-422和RS-232串口信號,測試結果如圖7所示,接收的數據準確無誤,8路串口同步率良好。

7 結束語

這種針對慣導組件測試所采用的設計,集成脈沖測量和串口數據接收于同一系統,可對多個產品的不同信號輸出同時測試,節約了資源,降低了成本。與傳統的測試系統相比,SOPC設計高度集成,降低了電路復雜度,提高了測試效率和系統的可靠性、穩定性。同時本系統安裝簡便,操作界面人性化,后期便于維護升級,可以作為慣導組件測試的新設備。

圖6 48路脈沖測量結果

圖7 8路串口數據接收結果

[1]張志文,趙浩.慣導組件的脈沖輸出測控系統[J].西安:西安工業大學學報,2009,29(5):461.

[2]Altera Corporation.CycloneⅢDevice Handbook[DB/OL].2007.07.http://www.altera.com.

[3]李蘭英.Nios II嵌入式軟核SOPC設計原理及應用[M].北京:北京航空航天大學出版社,2006:26-184.

[4]錢峰.EZ-USB FX2單片機原理、編程及應用[M].北京:北京航空航天大學出版社,2006.

[5]CypessSemiconductor Corporation.Impementing an 8-bit Asynchronous Peripheral Interface Utilizing the EZ-USB FX GPIF/Slave FIFOs[M/OL].2002.

[6]駱毅.撓性陀螺組合脈沖測試及系統標定[D].西安:西安工業大學,2012:32-43.

[7]孫鑫,余安平.VC++深入詳解[M].北京:電子工業出版社,2007:453-568.

[8]夏宇聞.Verilog數字系統設計教程(第2版)[M].北京:北京航空航天大學出版社,2008.

[9]袁志軍.基于FPGA的高速率多串口擴展的設計與實現[D].哈爾濱:哈爾濱工業大學,2008.

Research on Testing System for Inertial Navigation Com ponents Based on FPGA and NIOS

ZHANG Zhi-wen,PENG Yan

(School of Electronics Information Engineering,Xi’an Technological University,Xi’an 710032,China)

For the requirement of measuring the output of multiple signals in the test of inertial navigation components,a dual-mode data acquisition system of inertial component is designed on the basis of FPGA and NIOS IIsoft-core.The system takes FPGA and USB CY7C68013 as its core to count the 48 ports pluses outputted by 4 inertial navigation components and receive serial port data of 8 ports outputted by 8 inertial navigation components.In the end,the collected data will be uploaded to a controlling computer through a USB chip,and saved,processed,displayed by the computer.This design reduces complexity of the acquisition circuit,raisesmeasurement efficiency and promotes the reliability and stability of the acquisition system.

Inertial navigation component;FPGA;NIOS IIsoft-core;USB chip;Data collection

10.3969/j.issn.1002-2279.2014.01.023

TP274

:A

:1002-2279(2014)01-0085-05

張志文(1957-),男,陜西西安市人,教授,碩士生導師,主研方向:計算機測控技術、智能化儀表。

2013-09-18