基于PCIE2.0的物理層彈性緩沖器設計

鄭 乾,晏 敏,趙建中,李 優,張 鋒

(1.湖南大學物理與微電子科學學院,長沙410082;

2.中國科學院微電子研究所專用集成電路與系統研究室,北京100020)

基于PCIE2.0的物理層彈性緩沖器設計

鄭 乾1,2,晏 敏1,趙建中2,李 優2,張 鋒2

(1.湖南大學物理與微電子科學學院,長沙410082;

2.中國科學院微電子研究所專用集成電路與系統研究室,北京100020)

彈性緩沖器是PCIE,USB等高速串行總線物理層接收器的重要組成部分,用于物理層接收器中恢復時鐘與本地時鐘的頻率補償和相位同步,對信號的傳輸質量起著重要作用。基于PCIE2.0協議,采用存儲器常半滿的實現方式,設計一款深度、寬度均為10的彈性緩沖器。該彈性緩沖器應用于PCIE2.0的物理層設計中,并采用SMIC 55 nm CMOS工藝實現。芯片測試結果表明,該彈性緩沖器滿足PCIE2.0協議的要求,可正常工作于500 MHz的時鐘頻率下,實現恢復時鐘與本地時鐘的頻率和相位補償,保證了接收器正常接收數據。

彈性緩沖器;頻率補償;SKP指令集;半滿方式;異步FIFO

1 概述

PCI Express(PCIE)是第三代高性能 I/O總線,主要用于計算機與通信平臺等應用的外圍I/O互連[1]。PCIE總線采用串行高速差分總線替代傳統的并行總線,并采用端到端的連接方式,能夠獲得更高的系統吞吐量,正在逐漸全面取代PCI和AGP總線,成為新的局部總線工業標準[2]。采用PCIE總線進行通信時,發送器采用差分對的方式發送串行差分信號,接收器則采用時鐘和數據恢復電路從接收到的串行差分信號中恢復出時鐘和發送器傳送過來的串行數據[3]。由于發送器與接收器均有自己的獨立時鐘源,兩者的時鐘頻率及相位可能存在一定的偏差,即接收端恢復出來的時鐘與本地的參考時鐘可能存在一定偏差。當數據從恢復時鐘域傳至本地時鐘域時,需要進行跨時鐘域處理,保證信號傳輸的品質。PCIE總線采用彈性緩沖器進行頻率補償和相位同步[4],保證數據正常傳輸。針對PCIE總線的實際工程應用,本文采用半滿方式設計了一款彈性緩沖器。

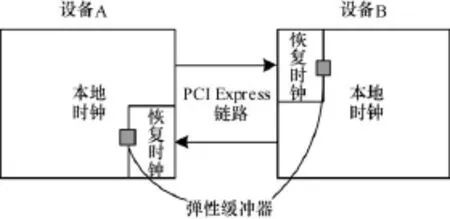

2 彈性緩沖器

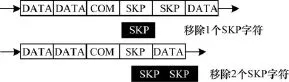

彈性緩沖器的作用在于橋接2個存在一定偏差的時鐘域以補償頻率和同步相位[5],即采用一個時鐘域(恢復時鐘)存放數據進入緩沖器,采用另一個時鐘域(本地時鐘)從緩沖器中移出數據,同時監測自身的狀態并且在適當的時候插入或移除特定字符來補償頻率偏差,避免溢出錯誤,如圖1所示。

圖1 橋接2個不同時鐘域的彈性緩沖器

2.1 時鐘頻率補償

PCIE2.0協議規定總線的最高傳輸速率為5 Gb/s,容許的誤差范圍是+/-300 ppm,即總線允許的頻率范圍為4.998 5 GHz~5.001 5 GHz[6]。由于參考時鐘源不同,發送器與接收器的時鐘頻率可能出現微小偏差。如果用單元間距 UI來計算的話, 5 Gb/s的一個時鐘單元間距為 200 ps,由于有+/-300 ppm的余裕,因此最壞情況下時鐘單元間距分別為199.94 ps和200.06 ps,即兩端最大時鐘間距偏差為0.12 ps。因而約每隔1 666個周期,可能位移一個時鐘單元間距[1]。既然時鐘有差異,那么勢必要對數據進行緩存處理,才能避免錯誤的發生。在PCI Express總線中,通常在傳送的SKP指令集中插入或移除SKP字符來補償這種時鐘頻率偏差。

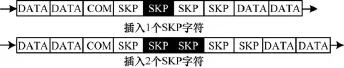

2.2 SKP指令集

PCIE總線協議規范了SKP指令集,該指令集由1個COM字符加3個SKP字符組成,如圖2所示。發送端將在一定字符間隔間發送SKP指令集[6]。因為在最差情況下,2個時鐘域之間大概每經過1 666個周期位移一個時鐘單元間距,所以SKP指令集的傳輸間隔必須小于1 666個時鐘周期。根據PCI Express總線協議規范,發送端在1 180個~1 538個字符時間間隔(不是位時間)輸出SKP指令集,而彈性緩沖器在接收到SKP指令集時,最多可插入或移除2個SKP符號以補償兩端的時鐘頻率偏差。之所以不是位時間,是因為SKP符號的插入和移除每次都是整個字符在處理[7]。插入和移除的位置通常位于第一個SKP字符之后,目的是保證極性的正確性以避免8b/10b解碼過程發生極性錯誤。

圖2 SKP指令集

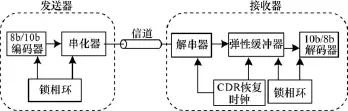

2.3 彈性緩沖器作用域

典型用于PCIE等高速接口的彈性緩沖器架構如圖3所示。彈性緩沖器位于解串器之后,8b/10b解碼器之前。因為彈性緩沖器是以符號的層次來補償頻率偏差,所以必須位于解串器之后。另外,PCIE總線協議規范了一種環回模式[7],即PCI Express設備可以將接收到的10位數據原封不動地通過發送端傳送回去,數據必須通過彈性緩沖器進行同步,所以必須位于8b/10b解碼器之前。

圖3 高速接口彈性緩沖器典型架構

2.4 彈性緩沖器容量

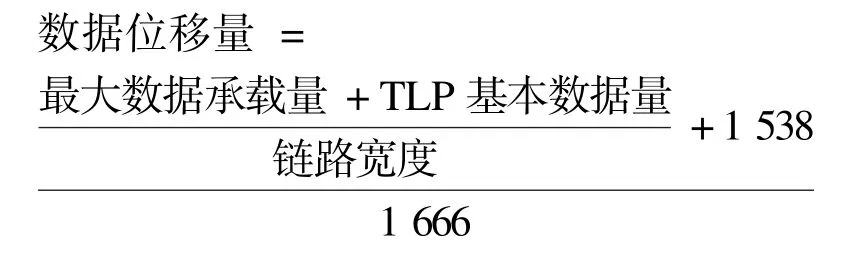

SKP指令集通常依據規定的時間間隔周期性送出,但當TLP數據交易層封包很大的時候,必須等到整TLP封包發送完之后,才將累積的待傳送SKP指令集發送出去[5]。所以,需要考慮彈性緩沖器的深度以保證最大TLP數據傳送時,也能正常補償時鐘偏差而不出現溢出狀態。

彈性緩沖器的大小通常取決于3個因素,分別是:傳送SKP指令集的時間間隔,設備支持的最大數據承載量(payload)及鏈路寬度[5]。SKP指令集字符間隔則明文指出為1 180個~1 538個字符,即最大間隔為1 538個字符。彈性緩沖器最大數據位移量的計算公式如下:

PCIE總線允許的最大數據承載量是4 096個字符,TLP基本數據量則包括數據框開始符號(1個字符)、封包次序符號(2個字符)、封包標頭(16個字符)、ECRC(4個字符)、LCRC(4個字符)以及數據框的退出符號(1個字符)總共28個字符[7]。而SKP指令集字符間隔則明文指出為1 180個 ~1 538個字符。

根據最大數據位移量計算公式可知,最壞情況即當兩端PCI Express設備以x1的連接狀態存在時,輸出端剛好必須輸出SKP指令集的時候,輸出最大數據承載量的封包。計算可得數據位移量為3.4個。

3 彈性緩沖器原理及實現

3.1 基本原理

彈性緩沖器實質上是一個異步FIFO[8],其寫時鐘為恢復時鐘,其讀時鐘為本地時鐘,FIFO深度則取決于數據最大位移量。

若彈性緩沖器的讀寫時鐘頻率一致,彈性緩沖器正常傳送SKP指令集[9],如圖4所示。

圖4 正常的SKP指令集傳送示意圖

若寫時鐘頻率小于讀時鐘頻率時,讀出的數據多于寫入的數據,彈性緩沖器在檢測到SKP指令集輸出時,根據實際的數據位移量在SKP指令集的第一個SKP字符之后插入1個或2個SKP字符[9],如圖5所示。

圖5 插入SKP字符的SKP指令集傳送示意圖

若寫時鐘頻率大于讀時鐘時,寫入的數據多于讀出的數據,彈性緩沖器在檢測到SKP指令集輸入時,根據實際的數據位移量在SKP指令集的第一個SKP字符之后移除1個或2個SKP字符[9],如圖6所示。

圖6 移除SKP字符的SKP指令集傳送示意圖

3.2 實現方式

彈性緩沖器的實現方式通常有2種:常半滿方式和流程控制方式[5]。常半滿方式采用把緩沖器維持在半滿狀態的方式實現,當檢測到SKP指令集的時候,若彈性緩沖器不處于半滿狀態,寫時鐘頻率小于讀時鐘頻率時,保持讀地址指針不變,輸出插入的SKP字符,寫時鐘頻率大于讀時鐘頻率時,則保持寫地址指針不變,將寫入的SKP字符移除[10]。流程控制方式則不同于常半滿方式,該方式不把緩沖器維持在半滿狀態,而是只維持在一個底端進入點的狀態[11],當檢測到SKP指令集的時候,若寫時鐘頻率大于讀時鐘時,其工作過程與常半滿方式是一致的,而寫時鐘頻率小于讀時鐘頻率時,則產生相應的使能信號,控制讀時鐘而不讓讀時鐘進行讀操作。常半滿方式與流程控制方式均有各自的優缺點,常半滿方式實現的彈性緩沖器其緩沖器深度較深,等待時間較長,但其電路實現簡單,而且不用門控時鐘,有利于DFT的實現。流程控制方式則可降低緩沖器的深度,相應等待時間較短,但需要添加額外的電路模塊去產生相應的使能信號,較復雜,同時該使能信號必須控制后續解碼器等電路的時鐘,即會產生門控時鐘,不利于DFT的實現。本文基于常半滿方式實現彈性緩沖器。

4 半滿彈性緩沖器結構設計

根據彈性緩沖器容量計算知道,當PCIE總線允許的最大數據承載量是4 096個字符時,數據的位移量為3.4個,故彈性緩沖器的深度應該為8,以滿足4個字符的位移量。考慮到讀寫時鐘本身存在相位偏差,故實際設計彈性緩沖器的深度為10,以保證在最差情況下彈性緩沖器依然能正常工作。

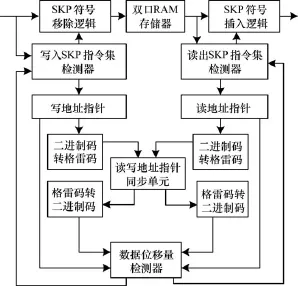

本文的常半滿彈性緩沖器的基本結構如圖7所示,包括讀寫地址指針模塊、讀寫地址指針同步模塊、數據位移量檢測模塊、SKP指令集檢測與增刪模塊和存儲器模塊。

圖7 彈性緩沖器基本結構

4.1 讀寫地址指針

讀寫地址指針模塊用來控制存儲器的讀寫地址指針。因為彈性緩沖器的深度為10,需要4位來編碼10個地址。考慮到讀寫地址指針以逐一遞增的方式改變,故采用二進制碼的編碼方式,即從0000~1111中選取10個地址。考慮地址指針比較需要在同一個時鐘域進行,而且采用格雷碼實現時鐘域過渡,故選取的地址范圍為0011~1100,讀地址read_addr從0011開始,寫地址write_addr從1000開始,循環變化,插入或移除SKP字符時保持地址不變。

4.2 讀寫地址指針同步

讀寫地址指針分別在讀寫時鐘控制下遞增,由于讀寫時鐘存在一定范圍的頻率差或者相位差,直接進行比較容易造成錯誤判斷,因此需將讀寫地址指針分別同步到同一個時鐘域下。二進制碼的編碼方式存在同時多位變化,為了避免毛刺的產生,需將二進制碼轉換為格雷碼,同步到另一個時鐘域,再將格雷碼轉換成為二進制碼[12]。

4.3 數據位移量檢測

數據位移量檢測模塊主要在于根據讀寫地址指針的差值來判斷實際緩沖器中的數據位移量。理論上讀寫地址指針的初始差值應該為5。因為2個時鐘可能存在相位偏移,所以超前時鐘域對應的讀寫地址指針的初始差值為6,滯后時鐘域對應的讀寫地址指針的初始差值為5。彈性緩沖器開啟后,根據位移量的大小產生相應的控制信號,對于寫時鐘域,當位移量大于6時產生over信號,當位移量大于7時產生over_more信號,當位移量等于0時,產生彈性緩沖器full信號。對于讀時鐘域,當位移量小于4時,產生under信號,當位移量小于3時,產生under_ more信號,當位移量等于0時,產生彈性緩沖器empty信號。

4.4 SKP指令集檢測與增刪

SKP指令集檢測與增刪模塊在于檢測數據流中的SKP指令集并根據數據位移量檢測模塊產生的控制信號進行SKP字符插入或移除。由于COM字符為K28.5字符,SKP字符為K28.0字符,因此分別用k28p5_wr、k28p0_wr、k28p5_rd、k28p0_rd分別代表寫入COM字符,寫入SKP字符,讀出COM字符,讀出SKP字符。為了保證檢測到SKP指令集以及在第一個SKP字符之后插入或移除SKP字符,采用三級流水線對這6個信號進行鎖存。同時,根據數據位移量模塊的控制信號,產生remove_skp以及insert_skp信號控制SKP字符的移除以及插入。當over_more信號有效時,對寫入的SKP指令集移除2個SKP字符,當over_more信號無效,over信號有效時,對寫入的SKP指令集移除一個SKP字符。當under_more信號有效時,對輸出的SKP指令集插入2個SKP字符,當under_ more信號無效,under信號有效時,對輸出的SKP指令集插入一個SKP字符。

4.5 存儲器模塊

該彈性緩沖器存儲單元位寬為10 bit,深度為10,故沒有采用專門的存儲單元庫實現,而是采用寄存器來實現。即寄存器實現的雙口RAM結構。

5 彈性緩沖器的仿真驗證與電路實現

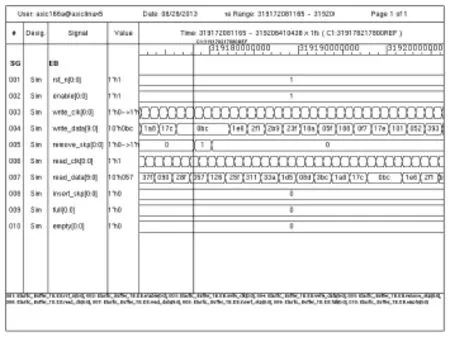

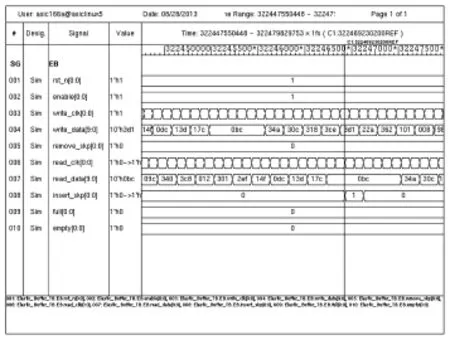

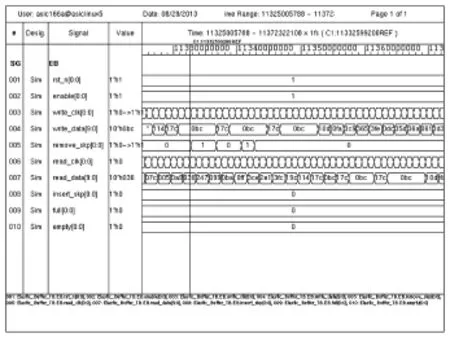

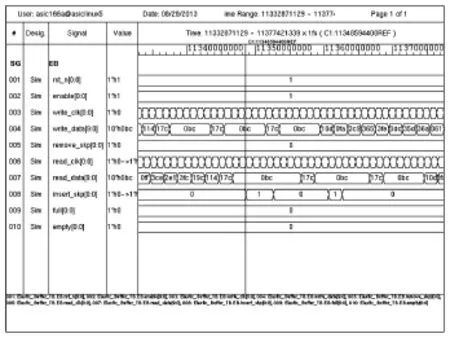

本文的彈性緩沖器設計采用Verilog HDL硬件描述語言設計,通過VCS做功能仿真驗證。仿真結果如圖8~圖11所示。

圖8 移除單個SKP字符的仿真結果

圖9 插入單個SKP字符的仿真結果

圖10 累積移除3個SKP字符的仿真結果

圖11 累積插入3個SKP字符的仿真結果

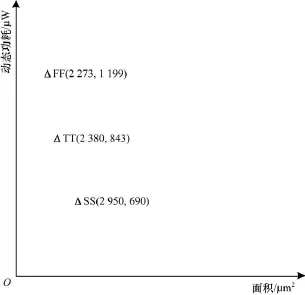

本文彈性緩沖器采用SMIC 55 nm CMOS工藝在不同的工藝角下進行綜合,讀、寫時鐘頻率均為500 MHz,并采用較為保守的時序約束,綜合所得電路的功耗和面積如圖12所示。其中,SS代表PVT:ss corner,1.08 V,125℃;TT代表 PVT:tt corner,1.2 V,25℃;FF代表PVT:ff corner,1.32 V, -40℃。

圖12 彈性緩沖器面積與動態功耗綜合結果

6 結束語

本文設計一種彈性緩沖器,將該彈性緩沖器集成到PCIE2.0的物理層設計中,并采用SMIC 55 nm CMOS工藝進行流片,測試結果表明,該彈性緩沖器完全滿足PCIE2.0協議的具體要求,讀寫時鐘達到500 MHz,實現了頻率補償和相位同步,且數據能夠正常傳送。

[1] Budruk R,Anderson D,Shanley T.PCI Express System Architecture[M].[S.l.]:MindShare,Inc.,2003.

[2] 王 齊.PCI Express體系結構導讀[M].北京:機械工業出版社,2010.

[3] Dhawan S K.Introduction to PCI Express——A New High Speed Serial Data Bus[C]//Proc.of Nuclear Science Symposium Conference Record.[S.l.]:IEEE Press,2005:687-691.

[4] Intel Corporation.PHY Interface for the PCI Express, SATA and USB 3.0 Architectures[EB/OL].(2013-10-23).http://www.intel.com/content/www/us/en/io/pciexpress/phy-interface-pci-express-sata-usb30-architectures. html.

[5] Winkles J.Elastic Buffer Implementations in PCI Express Devices[EB/OL].(2003-11-12).http:// www.docin.com/p-118906415.html.

[6] 劉瑞梅,韓曉毅.PCI Express總線PHY接口技術分析[J].河北建筑工程學院學報,2010,28(1):129-133.

[7] 陳乃塘.從PCIe探索彈性緩沖器真義[J].電子測試, 2005,(10):48-51.

[8] Cummings C E.Simulation and Synthesis Techniques for Asynchronous FIFO Design[EB/OL].(2005-06-16).http://www.docin.com/p-46476833.html.

[9] 陳乃塘.PCI Express數據連接層與物理層(上)[J].電子測試,2004,(8):39-50.

[10] 劉奇浩,翁惠輝.65 nm工藝下基于PCI Express2.0協議的物理編碼子層設計[J].中國集成電路,2013, (3):40-45.

[11] Michelogiannakis G,Balfour J,Dally W J.Elastic-buffer Flow Control for On-chip Networks[C]//Proc.of the 15th International Symposium on High Performance Computer Architecture.Raleigh,USA:IEEE Press, 2009:151-162.

[12] Schutti M,Pfaff M,Hagelauer R.Data Transfer Between Asynchronous ClockDomainsWithoutPain[D]. [S.l.]:Research Institute for Integrated Circuits,2000.

編輯 任吉慧

Design of Elastic Buffer at Physical Layer Based on PCIE2.0

ZHENG Qian1,2,YAN Min1,ZHAO Jian-zhong2,LI You2,ZHANG Feng2

(1.School of Physics and Electronics,Hunan University,Changsha 410082,China;

2.ASIC&System Department,Institute of Microelectronics of Chinese Academy of Sciences,Beijing 100020,China)

Elastic buffer is a very important function in receiver at high-speed serial protocols such as PCI Express (PCIE)and USB.The frequency delta and phase delta are managed perfectly to ensure data integrity by the elastic buffer when bridging local clock domain and recovered clock domain.This paper proposes elastic buffer logic in primed method to satisfy PCIE2.0 protocol specification.The width and depth of the elastic buffer are both 10.The proposed logic is integrated into Physical Layer(PHY)and implemented based on 55 nm CMOS process of SMIC.The result to be measured well agreeds with the actual requirement.It can work well under the frequency of 500 MHz and ensure data to

ata correctly.

elastic buffer;frequency compensation;SKP instruction set;half-full method;asynchronous First Input First Output(FIFO)

1000-3428(2014)10-0071-05

A

TN942

10.3969/j.issn.1000-3428.2014.10.014

國家“863”計劃基金資助項目(2011AA010403)。

鄭 乾(1987-),男,碩士研究生,主研方向:高速接口電路設計,計算機體系結構設計;晏 敏,副教授;趙建中,助理研究員;李 優,博士研究生;張 鋒,副研究員。

2013-11-04

2013-12-10E-mail:zhengqian@hnu.edu.cn

中文引用格式:鄭 乾,晏 敏,趙建中,等.基于PCIE2.0的物理層彈性緩沖器設計[J].計算機工程,2014, 40(10):71-75.

英文引用格式:Zheng Qian,Yan Min,Zhao Jianzhong,et al.Design of Elastic Buffer at Physical Layer Based on PCIE2.0[J].Computer Engineering,2014,40(10):71-75.