高速通信系統PCB的電磁兼容性設計*

陳 巖,陳 曦

(中國電子科技集團公司第30研究所,四川成都610041)

0 引言

隨著綜合業務和多媒體通信的快速發展,直接對通信系統提出了高速交換、大容量數據傳輸的設計要求。如:40 Gb/s、100 Gb/s以太網、SDH線路和背板高速傳輸,都對時鐘、信號線方面提出了具體要求。當信號頻率超過1 GHz,互連關系必須充分考慮傳輸線、電源、疊層、板材電參數等諸多因素的影響,在PCB的疊層、布局布線、阻抗匹配、高速差分線等設計方面均與設備的信號質量、電磁干擾和性能相關。而要如何做好這些,則需要在高速電路的PCB設計過程中進行完整的電磁兼容設計。

1 高速通信系統的電磁兼容性

高速通信系統主要應用對處理性能和傳輸速率都要求較高的場合,常選用高性能嵌入式CPU,如:MIPS、PowerPC、ARM 等,核 心 工 作 頻 率 可 達1.5 GHz以上;常選用超高速通信接口,如:XAUI(萬兆以太網)、SATA(并串與串并轉換)、PCIE等,傳輸速率都在Gb/s以上。所以在進行信號完整性(SI)設計時常見問題主要包括:反射、串擾、振鈴、過沖、地彈等[1]。

反射:反射就是信號在傳輸線上的回波,一般由于在傳輸線上阻抗不連續引起,部分能量會被反射回源端。

串擾:是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。

振鈴:振鈴表現為信號反復出現過沖和下沖,在電平門限上下抖動,振蕩呈欠阻尼的狀態。振鈴主要由于傳輸線上過度的寄生電感和電容,引起收端與源端的阻抗失配造成。

電磁干擾(EMI),包括傳導干擾和輻射干擾[2]。傳導干擾是指通過電介質把一個電網絡上的信號耦合到另外一個電網絡;輻射干擾指干擾源通過空間把其信號耦合到另外一個電網絡。由于高速器件對干擾敏感,很容易接收到高速假信號并給出響應,有時會對板卡正常工作產生致命的影響。

電磁兼容(EMC),它是研究在有限空間、時間和頻譜資源等條件下,各種電氣設備可以共同工作的科學,研究的重點之一在于如何盡可能的降低電路的 EMI。

2 高速通信系統的PCB設計

2.1 系統架構設計

由于通信設備的PCB設計重點和難點往往集中于高速差分線、高速并線總線和電源的設計上,這幾部分的設計是否滿足要求很大程度上直接關系到板卡最終是否可用。

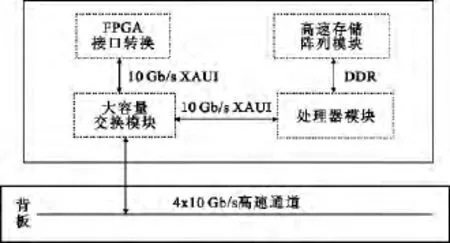

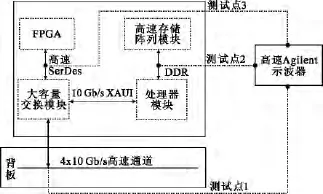

所以本節結合某通信設備中高速路由板的設計,重點詳細介紹高速板卡的PCB設計方法。該路由轉發板主要應用于骨干網的核心交換設備。板卡采用CPU、存儲陣列、FPGA和交換芯片的硬件架構,EMC設計難點主要在于:①CPU、DDR和FPGA信號頻率較高,切換速度快;②系統需要滿足40 Gb/s實時業務的處理,對系統性能要求很高;③PCB面積小,芯片引腳密度高、屬高密度板設計;④電源種類繁多,很多模擬電源,對電源紋波要求非常高;⑤用戶對設備的電磁兼容指標要求嚴格,上述要求對板卡的EMC設計提出了巨大的挑戰。圖1簡單展示了該板卡的硬件設計架構。

圖1 板卡硬件架構Fig.1 Hardware architecture of board

FPGA采用Xilinx公司的V5系列芯片,配合外圍電路組成。該芯片是Xilinx公司推出的高性能FPGA,邏輯資源豐富,同時支持高速SerDes接口。

處理器模塊與外圍的高速存儲陣列模塊之間采用DDR接口,DDR采用源同步接口,選通信號DQS使用雙沿來采樣數據 DQ,目標速率達到1 600 Mb/s,并行傳輸總線速率非常高。其中時鐘鎖相環的抖動、偏斜、PCB布線偏斜、同步開關噪聲、串擾和碼間干擾都會對芯片的時序產生影響,在PCB設計中必須重點考慮。

交換芯片與背板之間采用4路XAUI接口,每路XAUI傳輸速率達10 Gb/s。同層串擾、噪聲、損耗、抖動等問題都會對高速差分信號產生影響,最終表現在誤碼率和系統的EMI上。

2.2 具體PCB設計

通信設備中高速總線的SI和EMC直接影響到板卡的性能,在設計中,如何防止高速信號在傳輸線上的反射、串擾,降低電磁干擾,保證信號完整性是高速總線的設計重點,在本設計采取了如下的設計方法和步驟:

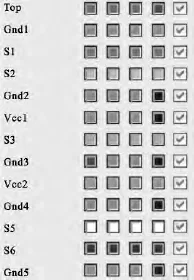

1)疊層設計:文中的高速PCB板卡均采用多層板設計(見圖2),通過增加地平面數量來改善板卡的EMC。增加地平面的作用在于保證了每層信號都有特性阻抗較低的地平面作為參考平面,而且可以有效的避免信號層間信號線的串擾。在本設計中,高速XAUI、SerDes差分線和DDR信號選擇信號質量最好的S1層和S2層走線。

圖2 高速路由板PCB設計Fig.2 PCB sheet of structure

2)布局布線設計:綜合系統信號流、不同種類功能進行布局,如:CPU等數字電路、鎖相環等模擬電路、接口電路、電源和時鐘;按照信號流向關系,盡可能保證XAUI、SerDes差分線和DDR高速并行總線走線最短,時鐘信號走線盡可能短,同時對參考時鐘和關鍵信號采用包地的方式進行處理,降低關鍵信號的電磁干擾和電磁輻射。對于傳速速率不高的低速信號線盡量避免信號線周圍有強輻射,同時進行單端50 Ω的阻抗匹配的處理。

在文中的設計中,單端信號采用線寬0.15 mm,外部間距大于0.2 mm的約束條件。差分信號采用如下的約束條件:布線長度不超過38.1 mm,線寬0.15 mm,內部線間距0.15 mm,外部線間距大于0.5 mm,差分阻抗采用100 Ω匹配,精確匹配差分對走線,誤差控制在0.15 mm以內。

3)高速差分線設計。差分信號接收端接收到的信號是差分信號線間的電壓差,在高速通信總線中,由于差分線的長度不同會引起兩根線間出現相位差,從而破壞差分信號的磁場抵消作用并產生EMI。在本設計中,XAUI、SerDes差分總線保證了差分線對長度誤差控制在0.05 mm以內[3]。

以本系統的高速差分時鐘設計為例:本系統中的高速時鐘設計需要提供4路125 MHz時鐘分別提供給FPGA。2路156.25 MHz時鐘提供給FPGA作為XAUI接口參考時鐘和工作時鐘。本設計中選用專用的高精度晶振和IDT公司的專用時鐘合成芯片來產生精度非常高的差分時鐘。在高速差分鐘的PCB布線選用TOP層的微帶線,原因在于:雖然信號層S1、S2相比TOP層的電磁干擾更小,但是必須通過過孔換層,這樣會增加信號的傳輸延遲;同時保證差分信號之間的緊耦合,保證差分線對的線間距小于或等于線寬,這樣處理來有效的抵消磁場和電場的互耦合,并減少對外的電磁輻射。

4)采用源端和終端阻抗匹配:匹配電阻主要起到了吸收反射的作業,同時也能保證總線正常傳輸差分電壓。在本設計中,差分線端采用封裝為0402貼片電阻,并靠近接收引腳(控制在5 mm內)。同時,在電阻中間通過電容接地來濾除共模噪聲。

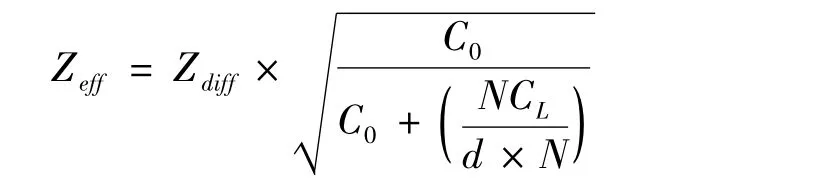

匹配公式選用Xilinx公司推薦的終端匹配電阻計算公式,公式如下所示:

式中,Zeff為差分線差分阻抗,Zdiff為差分線特性阻抗,約為單端傳輸線阻抗2倍。C0為傳輸線感抗特性;CL為終端負載的電容特性;N為總線上負載個數;d為總線上相鄰槽位之間間距。

5)背板接插件選擇:高速信號常遇到由于線路阻抗不匹配而出現的信號反射,印制線阻抗在板卡生產過程可以嚴格控制,但是在背板接插件處因無法控制容易出現信號反射。本設計選用無源背板方式,采用ATCA架構的高密度、高速度的差分接插件,保證了信號在背板連接器上反射盡可能小,同時高速信號的過孔選擇了微通孔也保證了過孔對信號影響最小。

綜上所述,作者在PCB設計過程中采用合理的疊層設計,根據信號流和分類進行了最優化布局,既保證了信號的參考平面完整,又大幅度降低了印制板的電磁輻射;按照高速線布線規則重點對高速差分信號和時鐘進行了約束和設計,同時對高速信號進行了阻抗匹配,既保證了高速信號完整性,又最大程度避免了信號的反射。通過以上處理最大程度上做到了設備的電磁兼容設計最優化。

2.3 電源完整性設計

電源信號的質量很大程度上會直接影響到板卡上信號的質量,尤其對于芯片模擬電源如果引入的噪聲較大會直接影響使用。

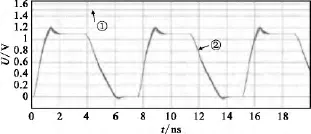

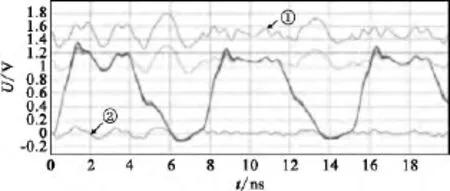

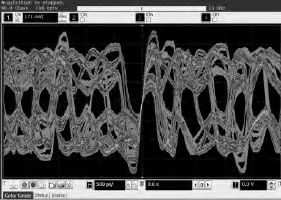

圖3展示了在理想電源(線①)條件下,信號對地漂移(線②)非常小;圖4展示了一旦電源層(線①)和地層(線②)上疊加了噪聲,信號紋波明顯增加。

圖3 理想電源和信號關系Fig.2 Relationship between ideal power and signal

圖4 實際電源和信號關系Fig.3 Relationship between practical power and signal

作者曾經在其他項目的電源設計時遇到過如下的問題:①在進行芯片的模擬電源設計時未選用紋波較小的LDO芯片,而選用了DC-DC芯片,導致模擬電源紋波較大,導致芯片工作穩定性較差;②對于電壓相同類型不同的電源未采用磁珠進行隔離,導致不同芯片之間電源出現相互干擾,噪聲增大,影響板卡工作的穩定性。所以文中在充分總結電源部分設計經驗的基礎上,在設計電源完整性設計時采用了以下的處理手段:

1)合理布局,模數分離。電源布局采用電流方向進行,同時輸入模擬電源和本板的數字電源、電源和地層之間盡可能進行隔離,電源和信號部分盡可能遠離,最大程度降低外界輸入的電源的噪聲對信號的干擾。

2)對不同類型電源盡可能采用獨立的電源模塊供電。對于電壓相同,類型不同的電源,采用磁珠進行隔離,降低電源間串擾。對于電流較小的模擬電壓采用線性電源供電。

3)電源包地處理。由于電源層和地層之間磁場的不停變化,在電路板邊緣會向外輻射電磁波,稱之為邊沿效應,采用電源層內縮,地平面包裹的方式,保證了電源層輻射的磁場只在地層傳導。

4)多種濾波電容組合。為降低電源輸出端產生的紋波及電流沖擊對板卡的干擾,在電源的輸入、輸出端通過添加高頻電容、電解電容并配合電感組成濾波電路,過濾不同頻段噪聲。

這里在電源設計過程中首先在合理布局,模數分離的前提下,采取了獨立供電措施,最大程度降低了不同電源間的串擾;進行了電源包地處理,減小了電源的電磁輻射;最后配合RC、LC濾波電路組合,最大程度吸收了電源噪聲,降低了電源紋波。通過本設計保證了電源的電磁兼容設計最優。

3 實驗與驗證

為了對板卡的信號完整性和EMI進行驗證,搭建測試平臺對板卡進行全面測試,測試系統框圖如圖5所示。

圖5 板卡SI和EMI測試平臺Fig.5 SI and EMI test platform

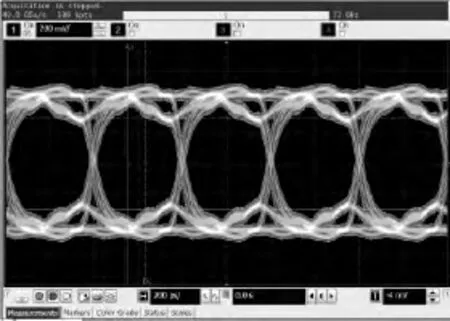

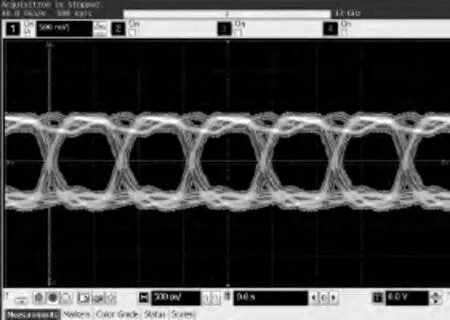

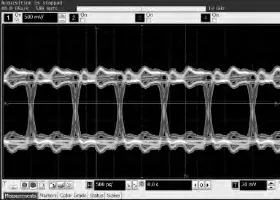

測試中使用了Agilent公司高帶寬、高采樣率示波器,型號 DSA91304A,帶寬13 GHz,采樣率可達40 GSa/s。選擇了3個關鍵信號作為測試點,通過測試點的眼圖、頻譜圖來對信號質量作較為全面的分析和評估[4]。圖6、圖7和圖8分別表示測試點1、2和3的眼圖,從每個眼圖的張開度、信號的建立保持時間來看,信號漂移和抖動很小,穩定可靠;同時測試了某塊因疊層設計錯誤而導致層間信號出現串擾的板卡的千兆鏈路信號,信號眼圖如圖9所示。從眼圖來看,信號抖動明顯,眼圖不規則,信號質量較差,有較大的時序風險,所以該板卡在實際使用過程中經常出現丟包的情況。

圖6 測試點1眼圖Fig.6 Point 1 eye diagram

圖7 測試點2眼圖Fig.7 Point 2 eye diagram

圖8 測試點3眼圖Fig.8 Point 3 eye diagram

圖9 串擾信號眼圖Fig.9 Crosstalk signal

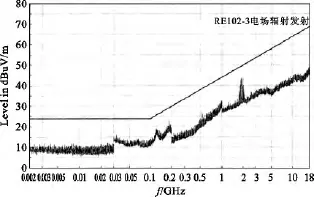

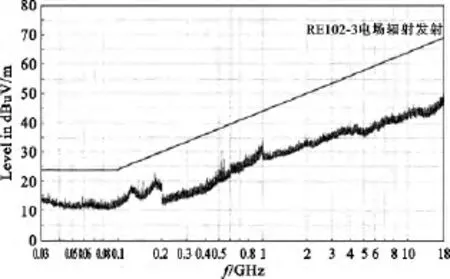

使用德國R&S公司EMI測試系統,按照某標準對整機進行了電磁兼容測試,測試設備在不同頻率范圍下的電磁輻射強度。圖10給出了根據RE102-3標準,在垂直極化下,頻率范圍為 0.002~18 GHz的電場輻射發射圖,從圖上看設備在2 GHz頻點左右有較強輻射;圖11給出了根據RE102-3標準,在水平極化下,頻率范圍為0.03~18 GHz的電場輻射發射圖,從圖上來看設備在500 MHz左右電磁輻射信號較強。總體來看,整機的電磁輻射冗余較大的控制在標準之內,較好的滿足指標的要求。

圖10 垂直極化電磁輻射Fig.10 Horizontal polarization EMI diagram

圖11 水平極化電磁輻射Fig.11 Vertical polarization EMI diagram

4 結語

文中針對高速通信系統PCB的電磁兼容設計原則和方法,結合項目實際進行了詳細論述,先后提出了高速信號完整性、疊層、布局布線設計方法和實施原則;高速差分總線、時鐘設計的約束原則以及電源完整性的設計原則,最后通過實驗對本設計的信號完整和電磁兼容性能進行了充分的驗證,實驗結果表明,本系統在信號完整性和電磁兼容性方面都能夠滿足設計要求。

綜上所述,通信系統PCB設計工程師,應該深刻理解EMC、傳輸線理論,仔細分析和總結引起各種信號畸變的原因,不斷的提高自身的設計水平,同時在設計中靈活應用EMC的設計方法和原則,大幅提升設備的性能。

[1]ERIC BOGATIN.信號完整性分析[M].李玉山譯.北京:電子工業出版社,2005.ERIC BOGATIN.YUSHAN LI translated.Signal integrity analysis[M].Beijin:Electronic Industry Press,2005.

[2]岳春華,尹征琦.高速PCB電磁兼容的研究[J].電子質量,2007(08):92-94.YUE Chun-hua,YI Zheng-qi.High Speed PCB EMC Research[J].Electronic Quality,2007,(08):92 -94.

[3]邱劍.差分線對的 PCB設計要點[J].通信技術,2010,43(06):221 -223.QIU Jian.Main Point on PCB Design of Differential Signal[J].Communications Technology,2010,43(06):221 -223.

[4]高曉宇,楊龍劍.高速串行通道的信號完整性問題分析[J].通信技術,2013,47(06):44 -47.GAO Xiao-yu,YANG Long-jian.SIAnalysis of High-Speed Serial Channel[J].Communications Technology,2010,47(06):44-47.