基于FPGA的紅外相機時序構造設計

韓紅霞,孫 航,曹立華

(中國科學院 長春光學精密機械與物理研究所,吉林 長春 130033)

1 引 言

光電跟蹤測量設備是能夠跟蹤空中飛行目標,并給出目標方位值和俯仰值的設備。紅外相機是根據物體的熱輻射成像的相機,目前在軍事、醫療、航天等很多領域都廣泛應用。光電跟蹤測量設備采用紅外相機跟蹤目標,可以在目標與背景亮度差值不大的情況下仍然穩定跟蹤,然而紅外相機的使用壽命是有限的,大型紅外相機的使用壽命一般是2 000~5 000h,如果頻繁地開啟相機,必然會縮短設備的使用年限,同時大靶面紅外相機基本依賴進口而且價格昂貴,更換相機不僅會增加成本而且會耗費很長的訂貨時間。為減少紅外相機的開機時間,節省項目開發成本,設計了紅外相機時序構造系統,在進行項目調試和實驗時,采用構造的紅外相機輸出信號,提供給后續圖像處理等系統作為數據源,在進行實際的跟蹤任務時再開啟紅外相機。設計的基于FPGA的紅外相機時序構造系統輸出的信號時序與真實的紅外相機輸出時序保持一致,輸出的像素值數據采用漸變數,可以作為圖像傳輸系統、圖像處理等后續系統的數據源,以供其進行編程和調試,調試成功之后直接將程序應用到紅外相機信號的傳輸、處理等操作,這樣就省去了程序開發、調試和驗證時頻繁的啟動紅外相機的過程,節省了相機的開機時間,同時也延長了設備的使用年限,節約了項目的開發成本,因此基于FPGA的紅外相機時序構造系統設計具有很強的工程實踐意義。

2 系統結構設計

2.1 硬件平臺結構設計

基于FPGA的紅外相機時序構造系統硬件平臺主要包括電平轉換單元、FPGA邏輯設計單元、時鐘處理單元以及串口數據收發單元等,其中FPGA邏輯設計單元是設計的核心,實現系統的時序配置和邏輯控制,圖1給出系統硬件平臺設計框圖。

圖1 紅外相機時序構造系統硬件平臺設計框圖Fig.1 Hardware structure diagram of the IR camera sequence construction design

如圖1所示,晶振時鐘OS_CLK為系統提供輸入時鐘信號,由FPGA內嵌的PLL對其進行處理,產生系統的工作時鐘信號。串行數據輸入電平轉換芯片采用MAX3071,將RS422電平格式信號轉為LVTTL電平格式信號,提供給FPGA。相機信號接收芯片采用DS90CR288,將相機輸出的CameraLink電平格式信號轉換為LVTTL電平格式信號,提供給FPGA進行時序測量,時序測量完成之后FPGA編程構造紅外相機信號,代替紅外相機作為數據源,提供給后續圖像處理等系統,這樣在調試過程中就可以不再啟動紅外相機了。FPGA邏輯設計單元是整個系統設計的核心,實現所有的時序配置和邏輯控制,通過FPGA編程可以實現紅外相機時序的詳細測量和記錄、時序構造信號的輸出以及所有外圍芯片的邏輯控制等,FPGA芯片采用EP2C5-T144I8。相機構造信號發送芯片采用DS90-CR287,將FPGA輸出的LVTTL電平格式信號轉換為CameraLink電平格式信號,提供給圖像處理等后續單元。串行數據輸入電平轉換芯片采用MAX3071,將LVTTL電平格式信號轉為RS422電平格式信號,提供給后續系統。

2.2 FPGA邏輯結構設計

基于FPGA的相機時序構造設計中,FPGA是整個設計的核心器件,如圖1所示,FPGA邏輯設計中包括PLL模塊、時序測量/記錄模塊、場同步信號FVAL產生模塊、行同步信號LVAL產生模塊、數據有效信號DVAL產生模塊以及漸變數據信號DATA產生模塊。

PLL模塊對輸入的晶振時鐘OS_CLK進行倍頻/分頻等處理,得到構造的像素時鐘信號CLK。時序測量/記錄模塊接收真實紅外相機的輸出信號,采用FPGA編程和SignalTap工具相結合的方法對相機的時序進行詳細測量,并記錄形成相機時序文件,作為模擬時序產生的依據。場同步信號產生模塊(FVAL_MAKE MODULE)以時序記錄文件為依據,編程實現場同步信號輸出。行同步信號產生模塊(LVAL_MAKE MODULE)以時序記錄文件為依據,編程實現行同步信號的輸出。數據有效信號產生模塊(DVAL_MAKE MODULE)以時序記錄文件為依據,編程實現數據有效信號的輸出。像素值信號即漸變數據產生模塊(DATA_MAKE_MODULE)通過編程實現在行有效的情況下輸出漸變數據,代替真實的像素值。

3 軟件設計

基于FPGA的紅外相機時序構造系統的軟件設計主要實現了真實紅外相機時序的詳細測量及記錄,時鐘信號的處理以及根據測量得到的時序構造與真實相機時序一致的時序信號。

3.1 時序測量及記錄

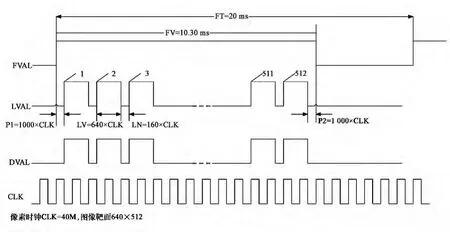

真實相機時序的測量是進行基于FPGA的紅外相機時序構造的前提,測量產生的時序記錄文件是進行后續時序構造程序的基礎。圖2以某紅外相機的時序測量為例,給出經過時序測量后得到的時序記錄文件示意圖。

圖2 某紅外相機時序記錄文件Fig.2 Sequence record file of an IR camera

如圖2所示,相機的時序記錄文件包括了像素時鐘信號CLK、場同步信號FVAL、行同步信號LVAL以及數據有效信號DVAL的相關信息。像素時鐘信號CLK由示波器測量得到,圖中相機像素時鐘為頻率40MHz,占空比1∶1的連續信號。場同步信號FVAL包括場周期FT和場有效時間FV,場周期信號可以由示波器測得,圖中場周期時間FT=20ms,場有效時間FV=10.30ms。行同步信號LVAL的測量需要采用FPGA編程和SignalTap工具結合測得,需要給出的行同步信息包括一場圖像中包含的有效行數、行有效時間LV、行消隱時間LN、起始行信號距離場起始信號的時間P1以及結束行信號距離場結束信號的時間P2,圖2中可見一場包含512行有效數據,LV=640×CLK,LN=160×CLK,P1=P2=100×CLK。數據有效信號DVAL的測量也需要采用FPGA編程和SignalTap工具結合測得,DVAL時序一般與LVAL信號時序相同。

3.2 時序構造

相機的時序構造是在已知相機時序文件的基礎上,構造與其時序一致的輸出信號,在進行調試等工作時,作為數據源提供給圖像傳輸、圖像處理等后續系統,以節省紅外相機的實際開機時間。

圖3 基于FPGA的時序構造流程圖Fig.3 Flow chart of the sequence conformation based on FPGA

時序構造軟件設計中,首先采用FPGA內嵌的鎖相環模塊PLL對輸入的晶振時鐘OS_CLK進行處理,得到構造的像素時鐘信號CLK;接著根據時序記錄文件中場同步周期FT及場有效時間FV,對時鐘信號進行計數處理,得到模擬的場同步信號FVAL;之后根據記錄文件中P1/P2/LV/LN的計數值以及一行中包含的有效行數,以FVAL為基準,編程實現模擬的行同步信號LVAL的輸出;之后根據數據記錄文件構造數據有效信號DVAL,一般情況下,DVAL信號與LVAL信號是相同的;最后在LVAL信號有效的情況下輸出漸變數,代替相機輸出的像素值。圖3給出基于FPGA的時序構造軟件流程圖。

在時序構造程序設計中,所有的測量值都以參數的形式在FPGA程序中體現,這樣對于不同的相機只要根據時序記錄文件修改相應的參數值即可,不用修改程序段,因此程序具有很強的可移植性。

3.3 具體程序設計

根據圖3所示的時序構造軟件流程圖,程序設計主要包括時鐘信號CLK產生模塊、場同步信號FVAL產生模塊、行同步信號LVAL產生模塊、數據有效信號DVAL產生模塊、漸變數據DATA產生模塊以及SignalTap時序驗證模塊等。由于篇幅原因,這里以場同步信號FVAL產生模塊為例,給出程序的具體設計。

首先根據輸入時鐘信號產生像素時鐘信號,外部的輸入時鐘OS_CLK頻率為50MHz,圖2所示時序文件中相機像素時鐘為40M,采用內部鎖相環模塊PLL對OS_CLK進行除5乘4處理,產生40M的像素時鐘。圖2所示,場同步信號FVAL周期為20ms,場同步有效時間約10.3 ms,根據公式(1)和公式(2)可以得到FT包括的時鐘周期數K1和FV包括的時鐘周期數K2。

式中:K1為場同步周期FT包括的時鐘周期數,FT為場同步周期,TCLK為時鐘周期;K2為場同步有效FV包括的時鐘周期數,LV為行同步有效長度(及包括的時鐘個數),LN為行消隱長度,Lnum為一場包括的行數,P1為行起始距離場起始的長度,P2為行結束距離場結束的長度。這樣計算得到場信號FT包括(20×106)/25=800000個時鐘周期,場同步有效FV包括(640+160)×511+640+1000+1 000=411 440個時鐘周期。根據如上計算,可以通過編程對時鐘信號進行精確計數,使得場同步信號持續800000個時鐘周期,場同步有效持續411 440個時鐘周期,場同步無效持續388 560個時鐘周期。以場同步FVAL構造為例,給出如下程序段設計。

以上程序通過計數的方式實現了場同步信號FVAL的構造,行同步LVAL、數據有效信號DVAL等信號的構造程序與場同步信號FVAL的構造程序結構基本相同。

4 時序驗證及實驗

4.1 時序驗證

按圖3所示的流程圖進行時序構造程序設計,輸出模擬的相機時序信號,之后,要進行時序驗證,若構造的時序信號與時序文件一致,則證明輸出的信號時序正確,可以提供給后續的圖像傳輸、圖像處理等系統作為數據源。時序驗證的方法是對輸出的信號進行實際測量,與時序文件進行比較,場同步信號FVAL采用示波器測量,其他信號采用SignalTap工具回采的方法進行測量。圖4給出采用SignalTap工具對構造的時序信號進行驗證的視頻截圖。

圖4 采用SignalTap工具驗證時序構造信號Fig.4 Using SignalTap tool to validate the sequence construction signal

圖4給出采用SignalTap工具驗證時序構造信號的效果圖,SignalTap文件以輸出的時鐘信號CLK為全局采樣時鐘,對輸出的場同步信號FVAL、行同步信號LVAL以及數據有效信號DVAL進行測試。圖4(a)顯示出輸出的行同步信號起始位置距離場同步信號起始位置參數P1為1 000個時鐘周期;圖4(b)顯示出行同步信號有效參數LV為640個時鐘周期,行同步消隱參數LN為160個時鐘周期;圖4(c)顯示出行同步結束位置距離場同步信號結束位置參數P2為1 000個時鐘周期。由圖4可知,輸出的構造信號時序與圖2的時序記錄文件完全一致,時序構造程序設計正確。

4.2 實驗

在驗證了時序構造程序正確的基礎上,對輸出的構造相機信號進行采集實驗,實驗組成框圖如圖5所示。如圖5所示,試驗中,相機信號輸入時序構造板,進行時序測量,根據紅外相機的真實時序構造與其時序一致的信號,輸出給圖像采集卡,圖像采集卡對構造的時序信號進行采集,將圖像顯示在顯示器上。

圖5 構造信號采集實驗結構框圖Fig.5 Experiment structure map of the construction signal collection

圖6給出采集得到的顯示圖像。

時序構造板卡輸出的場同步FVAL、行同步LVAL、數據有效DVAL及像素時鐘CLK信號與相機的時序完全一致,像素值用漸變數代替。

圖6(a)可以看出圖像穩定顯示,由于像素值是漸變數據,因此圖像亮度也是漸變的,圖像幀頻顯示為50Hz,靶面尺寸顯示640×512;圖6(b)采用Pixel Viewer工具顯示虛線框區域的像素值,可以看出像素值為穩定的漸變數值。實驗證明:基于FPGA的時序構造板卡輸出時序與相機時序完全一致,可以作為數據源提供給后續系統,在調試時代替紅外相機,以減少其開機時間。

圖6 時序構造板圖像輸出采集效果圖Fig.6 Collected image of the sequence construction board

5 結 論

基于FPGA的相機時序構造設計按照測量所得的紅外相機時序文件,構造與相機時序信號完全一致的信號,為圖像傳輸、圖像處理等后續系統提供數據源,以進行調試和實驗工作。實驗以某紅外相機為例,構造幀頻為50Hz,像素時鐘為40M,靶面尺寸為640×512,像素值為漸變數的輸出信號,并進行圖像采集。實驗表明:采用構造的相機信號作為信號源可以滿足圖像傳輸、圖像處理等系統的調試和實驗要求,效果良好。在調試實驗中采用構造的信號源代替實際的紅外相機,大量減少了紅外相機的開機時間,為項目節約成本,因此設計具有實際的工程應用價值。

[1] 熊文彬,蔣泉,曲建軍,等.基于FPGA實現的視頻顯示系統[J].液晶與顯示,2011,26(1):92-95.Xiong W B,Jiang Q,Qu J J,et al.Video display system based on FPGA [J].Chinese Journal of Liquid Crystals and Displays,2011,26(1):92-95.(in Chinese)

[2] 孫航,馮強,韓紅霞.基于FPGA的紅外序列圖像動態壓縮顯示[J].液晶與顯示,2011,26(8):551-554.Sun H,Feng Q,Han H X.Infrared sequence image dynamic compression display based on FPGA [J].Chinese Journal of Liquid Crystals and Displays,2011,26(8):551-554.(in Chinese)

[3] 宋振豐,李巖,于洋.數字圖像注入式紅外目標捕獲跟蹤訓練仿真[J].中國光學與應用光學,2010,13(2):194-200.Song Z F,Li Y,Yu Y.Simulation for IR capturing and tracking train based on digital image injection[J].Chinese Journal of Optics and Applied Optics,2010,13(2):194-200.(in Chinese)

[4] 李滿良,吳欽章.光電經緯儀CCD曝光中心測量系統的設計[J].光學精密工程,2013,21(5):1304-1310.Li M L,Wu Q Z.CCD exposure center measuring system for photoelectric theodolite[J].Opics and Precision Engineering,2013,21(5):1304-1310.(in Chinese)

[5] 許文海,吳厚德.超高分辨率CCD成像系統的設計[J].光學精密工程,2012,20(7):1603-1610.Xu W H,Wu H D.Design of ultra-high resolution CCD imaging systems[J].Opics and Precision Engineering,2012,20(7):1603-1610.(in Chinese)

[6] 冉峰,楊輝,黃舒平.面陣CCD彩色視頻圖像實時采集系統的設計[J].光學精密工程,2010,18(1):273-280.Ran F,Yang H,Huang S P.Design of real-time color video capture system for area array CCD [J].Opics and Precision Engineering,2010,18(1):273-280.(in Chinese)

[7] Levine P A,Saucer D J,Shallcross F V.High frame rata multi-port CCD Image and camera[J].SPIE,1992,1952:257-267.

[8] LIX Z,YU Z Y,SHANG F.Multifunction image target generator[J].Experimental Technology and Management,2002,19(4):36-37.