基于FPGA的以太網接口設計與實現

李 勛 ,劉文怡

(1.中北大學 電子測試技術國家重點實驗室,太原 030051;2.中北大學 儀器科學與動態測試教育部重點實驗室,太原 030051)

隨著互聯網硬件和軟件的迅猛發展,以太網接口成為目前使用最廣泛的網絡接口,具有接口簡單、通信速度高、傳輸距離遠、通信協議完善和工作性能穩定等優點,能夠實現遠程高速數據通信系統[1]。傳統以太網常采用主控芯片內部編寫以太網協議或在ARM等高性能處理器上運行操作系統,通過操作系統完成TCP/IP等復雜的通信協議,從而實現以太網通信[2],這兩種解決方案開發周期長、難度較大、成本較高。然而利用硬件協議棧芯片,只需要通過簡單的配置和外部線路連接就可以實現以太網的數據傳輸功能,這種方法開發難度小、集成度高且運行穩定,已成為實現以太網數據傳輸的首選方案[3]。

本文設計了一種利用FPGA控制硬件協議棧芯片W5300實現初始化配置、數據傳輸的以太網接口,并利用上位機UDP調試助手對其進行測試,實現了FPGA和上位機之間通信。

1 硬件設計

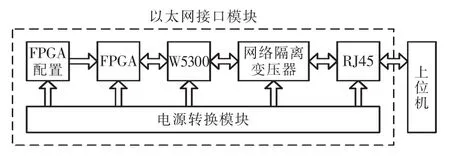

本文設計的以太網接口以FPGA為核心控制器,采用Xilinx公司Spartan-3系列XC3S400芯片,該芯片具有豐富的邏輯資源,易于配置;以太網接口協議芯片使用WIZnet公司生產的硬件協議棧芯片W5300。硬件結構如圖1所示,其工作原理:FPGA通過邏輯程序控制W5300數據總線、地址總線及讀寫、數據位選擇信號,通過編程控制這些信號實現對W5300的初始化配置、數據讀寫及上位機通信。上位機通過UDP調試助手軟件設置與接口模塊相對應的IP地址,通過發送“數據發送”和“數據接收”命令實現上位機與接口模塊中FPGA通信。

圖1 以太網接口硬件結構圖Fig.1 Ethernet interface hardware structure

硬件協議棧芯片W5300內部集成了10/100 M以太網控制器,MAC和TCP/IP協議棧,所以CPU不需要編寫復雜的TCP/IP協議,能夠大大地減小硬件接口設計和網絡編程的工作量,降低產品的開發難度和縮短開發周期,能夠實現可靠穩定的遠程數據通信系統。支持8個獨立端口同時連接,通信速率最高可達到80 Mb/s;與主機接口支持8/16 bit數據總線,支持2種主機接口模式;內部有128 KB TX/RX存儲器,可根據端口通信數據吞吐量動態調整其分配[4]。

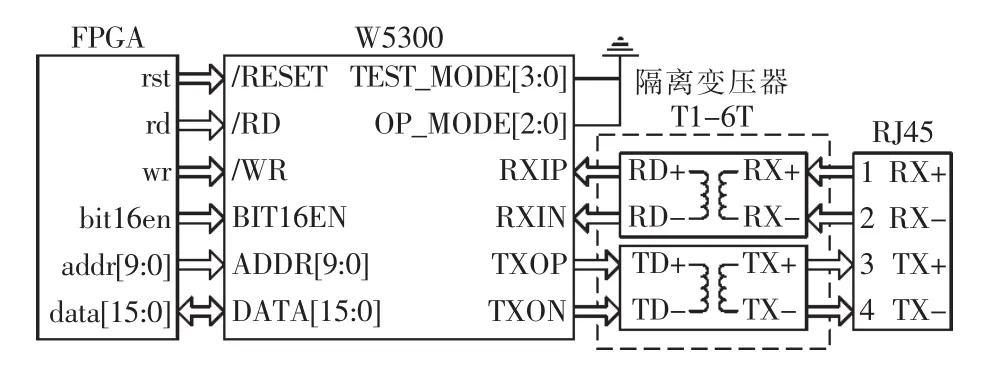

本文設計的接口主要是通過FPGA設置BIT16EN信號為高電平,實現16位數據總線工作模式,并采用直接尋址模式來實現數據的高速訪問,物理層使用W5300內部的PHY,并配置為全功能自動握手運行模式,即TEST_MODE[3:0]引腳和OP_MODE[2:0]引腳均接地。在以太網的設計中,外部接口的設計不可忽視,它關系到數據傳輸的抗噪聲能力和穩定性以及傳輸距離;在數據傳輸過程中為了增強W5300的差分信號抗干擾能力,防止不同電平通過網線傳輸損壞設備(在工作過程中,W5300需要3.3 V、1.8 V兩種不同電平),W5300與 RJ45之間采用網絡隔離變壓器T1-6T連接,其支持頻率高達300 MHz,既能滿足高速以太網的頻率要求,又能有效地保護接口電路。W5300芯片設有外置指示燈輸出,當網絡連接成功時,LINKLED引腳輸出低電平;當有數據包發送時,發送端TXLED輸出低電平,接收端RXLED輸出高電平,通過觀察外置指示燈,可以實時顯示以太網的數據傳輸動態。W5300以太網接口主要硬件連接原理如圖2所示。

圖2 W5300以太網接口硬件連接原理圖Fig.2 Connection schematic diagram of W5300 Ethernet interface hardware

2 邏輯程序設計

以太網接口邏輯程序設計部分主要通過Xilinx ISE12.1軟件平臺,選用硬件描述語言VHDL編寫狀態機程序,實現FPGA對W5300的配置及數據發送、接收控制,最終實現上位機與W5300的數據通信。

(1)W5300 配置模塊

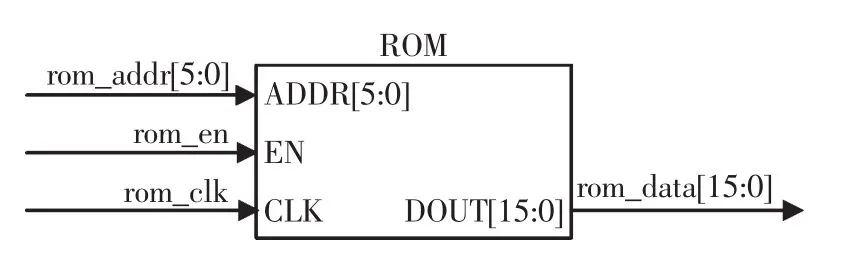

FPGA對W5300的配置模塊主要包括W5300初始化、對應SOCKETn端口配置。W5300的初始化主要分為三個步驟:主機接口設置,網絡信息設置和內部TX/RX存儲器的分配。在本文設計中,主要通過對26個不同寄存器的配置來完成W5300初始化。為了節省FPGA邏輯資源和靈活配置這些寄存器,FPGA邏輯控制程序調用了FPGA內部的IP核,通過構建深度為64B,位寬為16位的只讀單口塊ROM,將需要配置的寄存器的地址和其對應的寄存器值依次寫入初始化文件(.coe),并將該文件加載到BLOCK ROM中。在單口塊ROM中,當讀使能EN為高電平時有效,時鐘源CLK上升沿時,配置的數據從ROM端口輸出,寫進W5300數據線和地址線,其示意圖如圖3所示。

圖3 單口塊ROMFig.3 Single port block ROM

W5300只支持軟件復位,所以FPGA在上電后對W5300進行軟件復位。FPGA完成對W5300軟件復位之后就調用該IP核實現對W5300的初始化。本文選用SOCKET1進行數據通信,初始化完成之后 FPGA主要對 S1_MR、S1_PORT、S1_CR寄存器寫入對應地址和寄存器值實現對SOCKET1的端口配置,然后打開SOCKET1,并將其設置為UDP單道通信模式。FPGA完成對W5300配置之后,讀取S1_SSR寄存器值,判斷其是否處于UDP模式,若是則進入數據通信;反之,將該端口關閉,返回重新對W5300配置。

(2)W5300 通信控制模塊

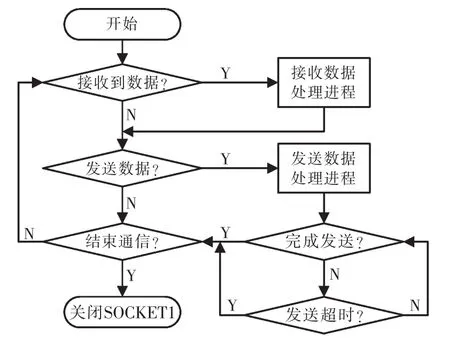

以太網接口與上位機通信包括數據接收和發送。W5300工作在UDP模式,UDP是一種報文通信協議,接收和發送數據不需要像TCP那樣建立SOCKET連接,就可以達到較高的傳輸速度[5],其通信流程如圖4所示。

圖4 UDP模式通信流程圖Fig.4 UDP mode communication flow

邏輯控制程序按照圖4通信流程編寫狀態機,首先讀取S1_RX_RSR寄存器,查詢W5300是否接到數據,若該寄存器接收數據字節長度大于0,則表明接收到數據,進入接收數據處理進程中。該進程主要負責處理內部RX存儲器中接收到的UDP數據,并將其讀取到FPGA中,數據全部讀取完后,執行RECV命令,即完成數據接收。數據接收完成之后跳轉到數據發送查詢,若S1_TX_FSR有足夠剩余空間時,將待發送的數據通過S1_TX_FIFOR依次寫入到TX存儲器中,并將發送數據字節數寫入到S1_TX_WRSR寄存器,然后運行SEND命令發送數據,判斷并清除發送完成、超時中斷,即完成數據發送。最后判斷是否結束通信任務,若結束任務,則將S1_CR寄存器設置為 “0x10”,W5300狀態變為SOCK_CLOSED,關閉SOCKET1端口;反之,返回開始查詢。

在通信過程中,程序的主要負責對W5300寄存器的讀寫控制、UDP傳輸協議的實現。當實時傳輸數據量較大時,對時序要求就非常嚴格,若時序不正常,將會導致數據的錯誤或丟失。為了滿足時序要求,本設計中FPGA程序利用控制狀態機數量來產生讀寫時序,硬件設計中FPGA選用40 MHz基準時鐘,并將W5300使能信號CS直接接地,一直保持有效狀態,每寫一次就控制/WR信號保持4個周期低電平,即100 ns,該時間大于芯片W5300寫時序最低要求50 ns;讀信號控制要求低電平有效時間大于65 ns,狀態機控制程序和寫信號一樣。

圖5 發送數據圖Fig.5 Sending data

圖6 讀取數據Fig.6 Reading data

3 實驗驗證

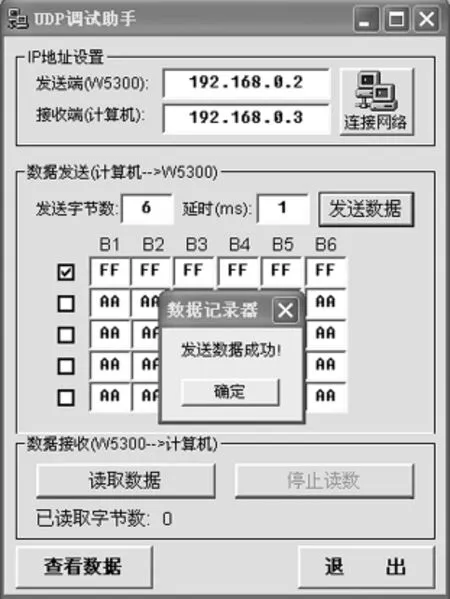

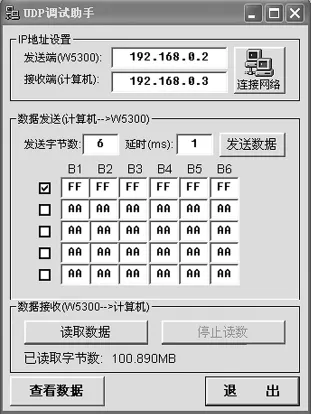

本文上位機使用UDP調試助手軟件,實現對FPGA控制的W5300以太網接口通信測試。該軟件采用VB編程,能夠實時顯示數據傳輸動態,易于可視化界面操作。如圖5、6所示,測試軟件設置W5300(發送端)的 IP 地址為:192.168.0.2,PC 機(接收端)的IP地址為192.168.0.3,連接網絡成功之后,就可以點擊“發送數據”或“讀取數據”發送命令給W5300,并通過W5300外置網絡LED指示燈亮滅情況判斷以太網連接、數據傳輸情況,進而實時觀察上位機與FPGA通信動態。

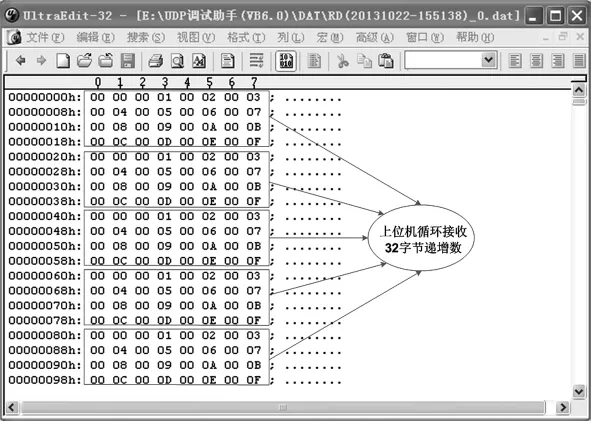

上位機UDP調試助手通過W5300以太網接口向FPGA下發“發送數據”命令,并設置發送字節數和延時時間,將6個字節的固定數“FF”下發給FPGA,如圖5所示;上位機發送“讀取數據”命令時,FPGA首先判斷接收到的數據是否為固定數“FF”,若接收到上位機發送的數據為固定數“FF”,則通過程序設置W5300,循環將32個字節的遞增數通過W5300接口上傳給上位機,如圖6所示。上位機軟件查看數據,導出FPGA通過W5300接口上傳的數據如圖7所示,分析數據,結果是循環的32個字節遞增數,與FPGA程序設置的上傳數據一致。通過UDP調試助手對本文設計的基于FPGA控制的W5300以太網接口進行數據傳輸測試,實驗結果表明該接口能夠可靠的實現上位機與FPGA之間的通信。

圖7 上位機接收數據圖Fig.7 PC receives data diagram

4 結語

本文介紹了一種基于FPGA控制的W5300以太網接口設計方案,并通過實驗驗證了其通信的可靠性和準確性。該接口結合了FGPA邏輯資源豐富,易于調用IP核,控制靈活的優點和W5300內部集成高速以太網控制器、TCP/IP協議棧等特性,通過簡單的配置和外部線路連接實現了以太網的數據傳輸功能,這種方法較于以太網通信傳統解決方案開發周期更短,難度更小,集成度更高,運行更穩定,該接口可以應用到以太網數據采集、檢測等領域,具有很高的實用性。

[1] LAN/MAN Standards Committee.IEEE Std.802.3-2005/Cor1-2006 Part 3:Carrier Sense Multiple Access with Collision Detection (CSMA/CD)Access Method and Physical Layer Specifications Corrigendum 1[S],2006.

[2] 雒珊,尹崗.基于ARM的以太網通信控制器的設計[J].電子測量技術,2009,32(10):133-135.

[3] 謝希仁.計算機網絡[M].北京:電子工業出版社,2008.

[4] WIZnet Device,Inc.High-performance internet connectivity solution-W5300[EB/OL].(2008).http:www.wiznet.co.kr.

[5] 張勇,甄國涌,王麗莉,等.基于W5300的以太網數據傳輸硬件設計及優化[J].化工自動化及儀表,2011,38(8):2-4.