基于FPGA的一種船用通信數字控制電路設計

隋波 , 陳玉林 , 高 嵬

基于FPGA的一種船用通信數字控制電路設計

隋波1, 陳玉林2, 高 嵬2

(1. 海軍駐大連地區軍事代表室, 遼寧大連; 2. 海軍工程大學電氣工程學院, 武漢 430033)

本文針對船用通信系統存在干擾的問題,設計了一種基于FPGA的數字控制電路,該電路可有效防止干擾,能很好的確保艦艇通信系統的正常工作。

FPGA 數字通信電路

0 引言

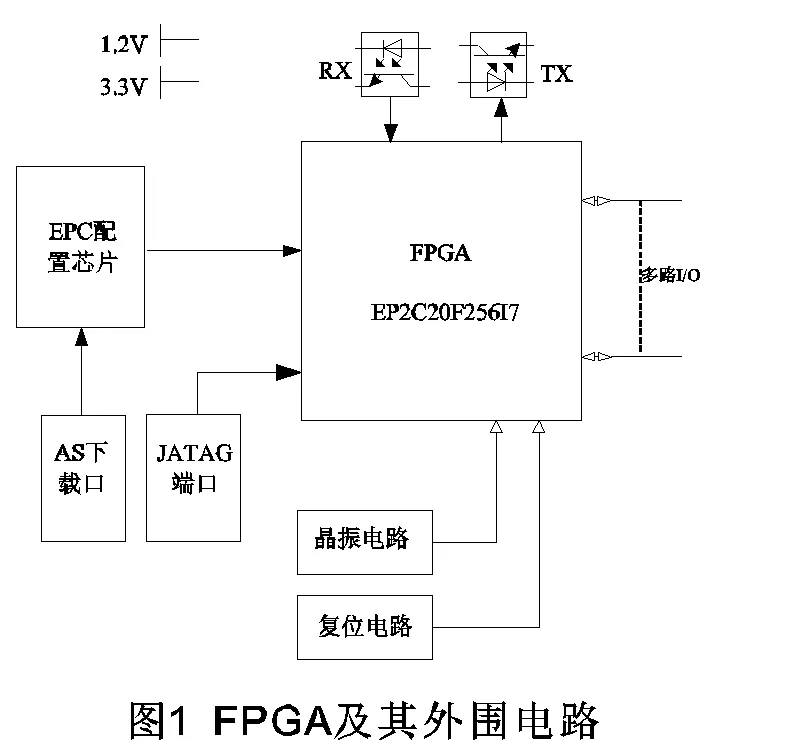

在所有數字元件中,FPGA發揮著控制核心的重要作用,具體包括:實現高速光纖通訊功能、多級有源門極驅動算法、故障保護邏輯、數字信號處理等。船用通信系統由于干擾嚴重,長期以來只能通過笨重的濾波裝置進行濾波,采用數字控制電路,可以有效的防止干擾,確保通信系統的正常運行。圖1顯示了FPGA及其外圍電路結構。

1 FPGA數字電路的要求

在中大功率IGBT數字驅動器中,以FPGA為核心的數字電路必須符合如下要求:

1)快速的運算能力和較小的延時。IGBT的開通和關斷過程在μ秒級[1],而驅動器要在IGBT開通和關斷的暫態過程中對IGBT的某些參數進行改變和控制。而且,欲調控這些參數,首先要通過監測電路中獲取這些參數的當前值,再通過FPGA的運算處理,將結果輸出至外電路,再作用于欲改變的電路。所以,必須盡可能減少FPGA的運算時間,一方面可以通過優化載入的FPGA的處理程序,一方面就需要提高FPGA的時鐘頻率,增加其運算速度。

2)較小的三維尺寸。小型化是電力電子器件發展趨勢之一,盡量減小驅動板的大小對變流器系統整體小型化有十分重要的作用。FPGA是驅動板中最大的數字器件,它的大小是決定整個驅動板大小的重要因素。此外,小的FPGA有利于驅動板中其它元件的布局,并為更多的輔助電路提供空間。

3)較好的電磁兼容性能。驅動板必須考慮變流器系統內惡劣的電磁環境,其自身也存在強弱電緊耦合,且要完成高速光纖通訊功能,因此電磁兼容性必須加以考慮。

4)豐富的接口電路。FPGA及數字電路內存在多種接口需求,如電源、時鐘、I/O、模擬接口等,所以數字電路必須能夠滿足這些接口需求。

2 數字控制電路的設計

綜合考慮以上因素,本設計最終采用ALTERA公司的EP2C20F256I7N型FPGA,此型號FPGA能夠較好的滿足上述四點要求。EP2C20F256I7N型FPGA的運算速度可達百兆Hz,即時鐘周期可達n秒級,能夠較好的滿足驅動板對處理速度的要求。16 mm×16 mm、BGA封裝,占用的面積比較小,引腳數為16×16,共256個引腳,可以完全滿足驅動板外圍電路對FPGA對其引腳的要求。其存儲容量也較大,預計能夠存儲所需要的各種程序。

同時,EP2C20F256I7N型FPGA應用于IGBT數字驅動器也存在一些不足,包括:

(1)所需要的電源種類較多,需要較多的電壓轉換芯片提供所需的電源電壓。EP2C20F256I7N型FPGA需要電壓值為3.3 V和1.2 V兩種不同的電源,而且1.2V電源需要分成三個相對獨立的電源為FPGA供電。這一方面使驅動板需要分出更多區域給電源芯片,另一方面,也為PCB設計中電源分區帶來了一定的困難。

(2)EP2C20F256I7N型FPGA為BGA封裝,而BGA封裝更易受環境中EMI的影響。在中大功率IGBT的應用場合,一般都存在較強的電磁干擾,這使得驅動板的安全運行受到一定的威脅。而且BGA封裝的FPGA引腳全部在FPGA的底部,在PCB制作過程中,需要精心考慮FPGA引腳布線,為驅動板設計來來了一定的困難。

(3)FPGA的輸入輸出端口為3.3 V電壓,即高電平3.3 V有效,相對與5 V電壓來說,3.3 V電壓較低,更容易受到驅動板電路中各種干擾的影響,降低了FPGA接受反饋信號和發出的控制指令的可靠性。

四、數字控制電路的功能簡介

如圖1,FPGA的配置電路包括:晶振電路,程序下載電路,系統復位電路,光纖通訊接口等四部分。

晶振電路為FPGA提供所需的時鐘周期,本設計中,晶振設計如圖2所示。電路中3.3 V電源為晶振電路供電,端口CLK0~CLK3連接至FPGA為FPGA提供時鐘周期,之所以提供四路,是為了提供備份時鐘周期。圖示晶振電路可輸出50MHz的時鐘周期,如需要更高頻率的時鐘周期,可以通過鎖相環提供。

在實際應用和實驗調試過程中,會用到系統復位功能,本設計采用如圖3電路為FPGA提供復位信號。SYS_RESET將復位信號輸出至FPGA端口。

FPGA通過AS下載口并通過EPC配置芯片實現驅動程序的加載,利用JATAG端口實現在線調試。這里不加贅述。

在驅動板工作過程中,需要從系統主控器中得到控制指令,同時也需要將IGBT運行狀態、故障信號上傳至系統主控器,這就需要實現FPGA與主控器的通訊功能基于隔離的需要和傳輸速度的考慮,本設計采用光纖設備實現FPGA與系統主控器的通訊功能。目前僅用于實驗,所以在電路中只使用了接受光纖端口HFBR2412T,用于接收實驗時發出的控制命令,其電路如圖4。輸出端TF_RECEIVE將光纖端口接受到的控制指令發送至FPGA,之所以使用3.3 V電源,是因為FPGA的I/O口使用的是3.3 V電源,光纖端口需要與其一致。FPGA有多路I/O端口與驅動板其它電路相連,主要實現采集數字化的IGBT狀態信號,發送控制指令等。

3 結論

針對船用通信系統干擾源多的特點,設計了一種基于FPGA的數字電路,該電路不僅能實現原有模擬電路的全部功能,還對干擾不敏感,具有較好的抗干擾效果。

[1] Schmitt G, Kennel R. Voltage gradient limitation of IGBTs by optimised gate-current pro?les[C].Power Electronics Specialists Conference.Rhodes: IEEE, 2008: 3592-3596.

A Digital Circuit Design for Communication Controlling in Vessels Based on FPGA

Sui Bo1, Chen Yulin2, Gao Wei2

(1. Naval Representatives office in Dalian, Dalian116021, Liaoning,China; 2. The School of Electric Engineering , NUE, Wuhan 430033, China)

TN919

A

1003-4862(2014)07-0042-02

2014-04-02

隋波(1980-),男,工程師。研究方向:艦船監造。