數(shù)字電壓表的VHDL程序設(shè)計(jì)與硬件實(shí)現(xiàn)

李亞峻,徐世超,黃建民,王 潔,馬 強(qiáng)

(天津科技大學(xué)電子信息與自動(dòng)化學(xué)院,天津 300222)

數(shù)字電壓表的VHDL程序設(shè)計(jì)與硬件實(shí)現(xiàn)

李亞峻,徐世超,黃建民,王 潔,馬 強(qiáng)

(天津科技大學(xué)電子信息與自動(dòng)化學(xué)院,天津 300222)

將FPGA與模數(shù)轉(zhuǎn)換器TLV571相結(jié)合設(shè)計(jì)了數(shù)字電壓表.用VHDL語(yǔ)言編程實(shí)現(xiàn)了模擬電壓的測(cè)量、模數(shù)轉(zhuǎn)換、計(jì)算與讀取,用狀態(tài)機(jī)完成了FPGA對(duì)TLV571的控制.將數(shù)字電壓、模擬電壓的BCD碼與ROM地址、數(shù)據(jù)一一對(duì)應(yīng),用查找表的方式從相應(yīng)的ROM地址中取出高4位和低4位BCD碼,對(duì)二者進(jìn)行BCD碼加法運(yùn)算即可獲得模擬電壓值.通過實(shí)驗(yàn)平臺(tái)測(cè)試驗(yàn)證了數(shù)字電壓表設(shè)計(jì)的正確性.

現(xiàn)場(chǎng)可編程門陣列;VHDL語(yǔ)言;模數(shù)轉(zhuǎn)換;BCD碼

目前的數(shù)字電壓表主要以單片機(jī)[1–2]和現(xiàn)場(chǎng)可編程門陣列(FPGA)[3–4]作為系統(tǒng)的控制核心.基于單片機(jī)設(shè)計(jì)的優(yōu)點(diǎn)是技術(shù)成熟、設(shè)計(jì)成本較低、編程靈活.但是,單片機(jī)系統(tǒng)的外圍電路由許多獨(dú)立元件連接而成,所以系統(tǒng)的復(fù)雜度高、抗干擾能力差、可靠性較低、功耗高.基于FPGA設(shè)計(jì)的優(yōu)點(diǎn)是測(cè)量精度高、速度快、讀數(shù)方便、抗干擾能力強(qiáng)、可擴(kuò)展性強(qiáng).另外,F(xiàn)PGA由可編程門陣列和可編程邏輯器件二者演變而來(lái),它既有前者的高集成度和通用性,又有后者的用戶可編程性[4].FPGA控制器的硬件功能完全由軟件編程實(shí)現(xiàn),調(diào)試方便,不需改變硬件電路即可實(shí)現(xiàn)系統(tǒng)更新,克服了基于單片機(jī)設(shè)計(jì)系統(tǒng)的缺點(diǎn)[5].

文獻(xiàn)[4]采用了基于FPGA的設(shè)計(jì)方法,但是在其VHDL程序設(shè)計(jì)中存在明顯不足:該程序用多個(gè)if嵌套語(yǔ)句編程實(shí)現(xiàn),隨著數(shù)據(jù)的有效位數(shù)增加,編程復(fù)雜度將增加,使程序的可讀性變差;而且,此方法對(duì)高4位和低4位BCD碼相加后進(jìn)行BCD碼調(diào)整,只考慮了求和后每一位十六進(jìn)制數(shù)大于9且小于等于15的情況,沒有考慮大于15、小于等于18的情況.

本文基于FPGA器件、用VHDL語(yǔ)言編程實(shí)現(xiàn)數(shù)字電壓表的設(shè)計(jì),介紹數(shù)字電壓、模擬電壓BCD碼與存儲(chǔ)器(ROM)地址、數(shù)據(jù)的關(guān)系,詳細(xì)闡述了BCD碼加法運(yùn)算的原理.

1 數(shù)字電壓表的總體架構(gòu)

1.1 數(shù)字電壓表的VHDL模塊化設(shè)計(jì)

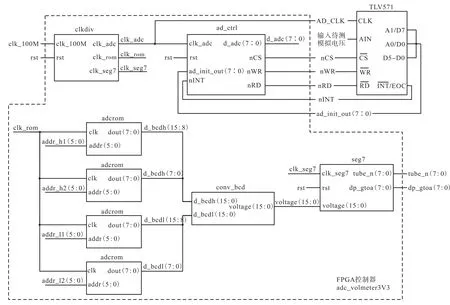

圖1中虛線框內(nèi)為采用VHDL語(yǔ)言編程實(shí)現(xiàn)的FPGA控制器adc_volmeter3V3.設(shè)計(jì)中采用了模塊化設(shè)計(jì)思想,每個(gè)模塊實(shí)現(xiàn)某種特定功能.時(shí)鐘分頻模塊clkdiv為其他模塊提供時(shí)鐘信號(hào),模數(shù)轉(zhuǎn)換控制器ad_ctrl控制外部的并行模數(shù)轉(zhuǎn)換器TLV571正常工作,ROM adcrom的地址和存儲(chǔ)數(shù)據(jù)分別對(duì)應(yīng)于數(shù)字電壓和模擬電壓值的BCD碼,BCD碼運(yùn)算控制器conv_bcd實(shí)現(xiàn)BCD碼的加法運(yùn)算,數(shù)碼管顯示控制模塊seg7實(shí)現(xiàn)被測(cè)電壓在4個(gè)數(shù)碼管上的動(dòng)態(tài)顯示.

圖1中各模塊輸入輸出端口連線上的標(biāo)識(shí)符表明該連線為FPGA控制器的內(nèi)部信號(hào)線,用于各模塊之間的連接,如clkdiv模塊為seg7模塊提供時(shí)鐘信號(hào)clk_seg7,ad_ctrl模塊輸出的數(shù)字電壓d_adc為adcrom模塊提供存儲(chǔ)模擬電壓值的地址addr.

1.2 FPGA器件與外設(shè)的連接

圖1中也顯示了FPGA器件與外設(shè)的連接關(guān)系.各模塊輸入輸出端口連線左右兩側(cè)的標(biāo)識(shí)符表示FPGA器件相應(yīng)引腳將與實(shí)驗(yàn)平臺(tái)上的外設(shè)進(jìn)行硬件連接.圖1右上角為FPGA器件與TLV571的連接關(guān)系,tube_n和dp_gtoa分別接數(shù)碼管的位選和段選端,clk_100,M接100MHz的外部晶振,rst接按鈕用于復(fù)位.

clkdiv模塊和seg7模塊有大量的VHDL源程序可供參考,這里不作介紹.下面重點(diǎn)介紹TLV571的工作原理與實(shí)現(xiàn)、數(shù)字電壓和模擬電壓值與ROM地址和數(shù)據(jù)的對(duì)應(yīng)關(guān)系、BCD碼的加法運(yùn)算.

2 AD轉(zhuǎn)換器TLV571的工作時(shí)序與FPGA控制

2.1 TLV571的工作時(shí)序

TLV571是8位并行AD轉(zhuǎn)換器,每次轉(zhuǎn)換需要16個(gè)時(shí)鐘周期.為了使其正常工作,需要先配置內(nèi)部的控制寄存器CR0、CR1.該芯片共有24個(gè)引腳,其中,A1/D7、A0/D6、D5~D0為數(shù)據(jù)輸入/輸出端,用于輸入對(duì)CR0(A1A0=00時(shí))和CR1(A1A0=01時(shí))的配置信息、輸出AD轉(zhuǎn)換后的8位數(shù)字電壓;片選、寫、讀、轉(zhuǎn)換完成標(biāo)志均低電平有效;待測(cè)電壓由AIN端輸入.

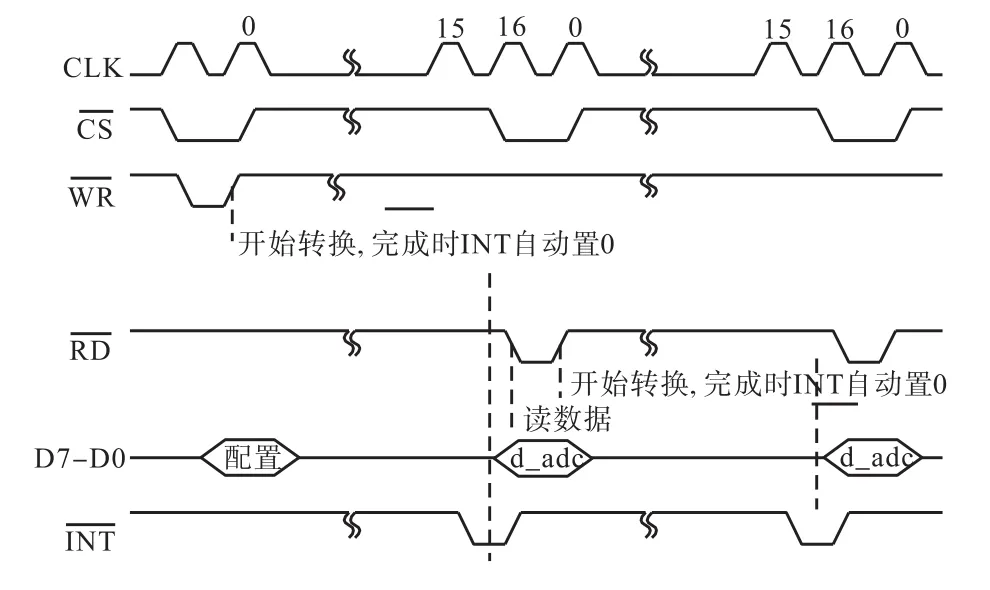

CR0、CR1配置不同則AD轉(zhuǎn)換器的工作時(shí)序有所不同[6].在本設(shè)計(jì)中CR0寄存器被配置為00,101,000(16進(jìn)制數(shù)為28,H),CR1寄存器被配置為01,000,000(16進(jìn)制數(shù)為40,H),即選擇由外部時(shí)鐘控制、用軟件方式啟動(dòng)、當(dāng)變?yōu)榈碗娖綍r(shí)表示AD轉(zhuǎn)換已完成、輸出8位二進(jìn)制數(shù),其工作時(shí)序如圖2所示.

圖2 TLV571工作時(shí)序圖(軟件啟動(dòng))Fig. 2 Timing chart of TLV571(software start)

2.2 TLV571的FPGA控制

圖1中的ad_ctrl模塊是TLV571的控制模塊,其VHDL語(yǔ)言編程采用了狀態(tài)機(jī)的方式.如圖3所示,共有8個(gè)狀態(tài)s0—s7,每個(gè)狀態(tài)下的片選信號(hào)nCS、寫信號(hào)nWR、讀信號(hào)nRD和AD轉(zhuǎn)換完成標(biāo)志nINT嚴(yán)格按照?qǐng)D2的工作時(shí)序進(jìn)行設(shè)置.

圖3 TLV571狀態(tài)轉(zhuǎn)換圖Fig. 3 Diagram of TLV571 state transition

3 模擬電壓BCD碼的存儲(chǔ)

已知FPGA實(shí)驗(yàn)平臺(tái)上的TLV571參考電壓為3.3V,因此數(shù)字電壓表的可測(cè)量范圍為0~3.3V.TLV571為8位并行輸出,可知其電壓最小分辨率為3.3V/256≈0.013V,即AD輸出數(shù)字電壓d_adc為00,000,001時(shí)所對(duì)應(yīng)的模擬電壓值為0.013V,據(jù)此可求出任意8位數(shù)字電壓所對(duì)應(yīng)的模擬電壓值.

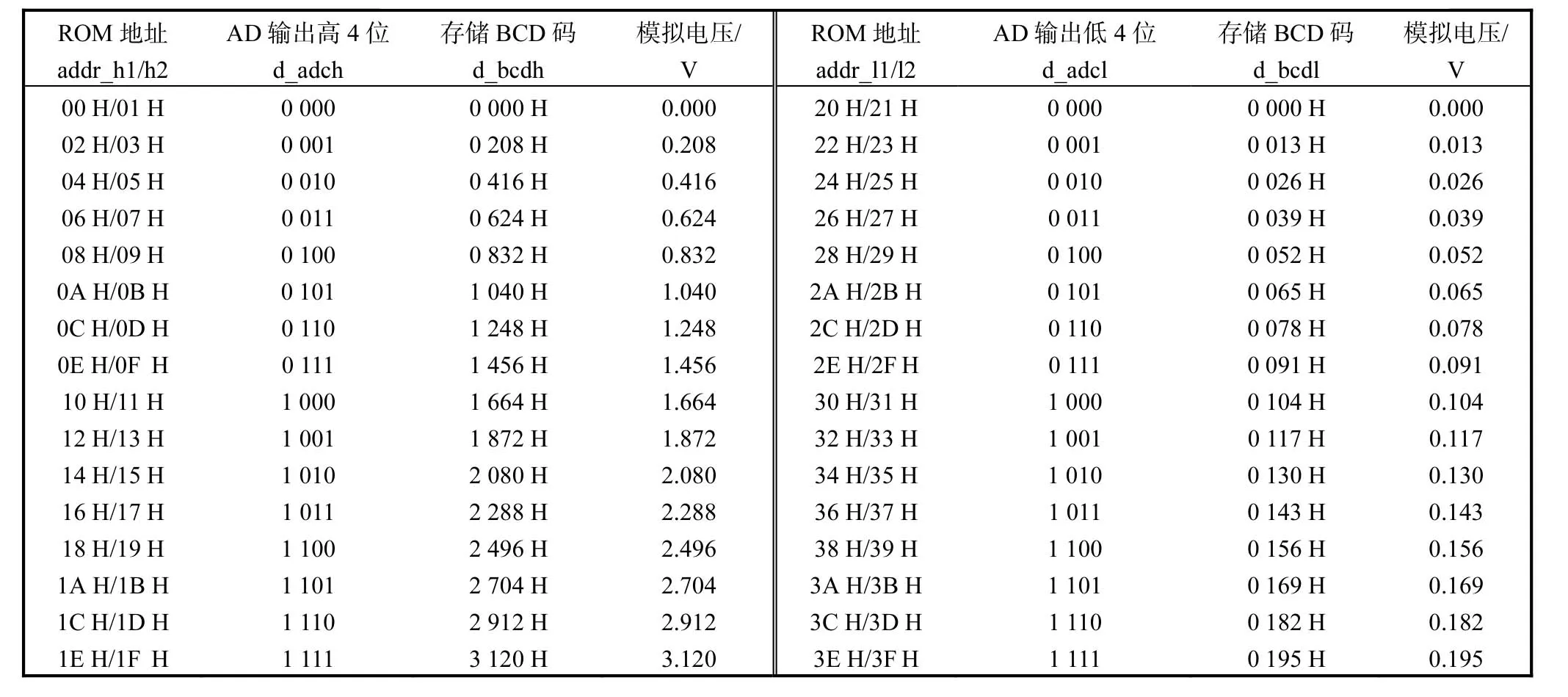

為了簡(jiǎn)化運(yùn)算,事先將數(shù)字電壓的高4位和低4位所對(duì)應(yīng)的模擬電壓值存儲(chǔ)在ROM中,如表1第2、4、6、8列所示,其中第2列d_adch和第6列d_adcl分別為d_adc的高4位和低4位.根據(jù)AD輸出的實(shí)際數(shù)字電壓,查表1后將d_adch和d_adcl所對(duì)應(yīng)的模擬電壓值相加即可得到待測(cè)模擬電壓值.例如當(dāng)d_adc為10,111,111時(shí),其高4位1,011和低4位1,111對(duì)應(yīng)的模擬電壓值分別為2.288V和0.195V,所以可得待測(cè)模擬電壓值為2.288+0.195=2.483V.

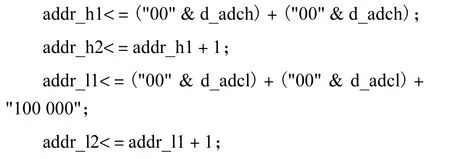

存儲(chǔ)器只能存儲(chǔ)二進(jìn)制數(shù),所以實(shí)際存儲(chǔ)在ROM中的數(shù)據(jù)是模擬電壓值的BCD碼,即用十六進(jìn)制表示的十進(jìn)制數(shù).ROM中存儲(chǔ)的數(shù)據(jù)與模擬電壓值對(duì)應(yīng),ROM地址與AD輸出的數(shù)字電壓d_adc對(duì)應(yīng).由表1可知,每個(gè)模擬電壓值所對(duì)應(yīng)的BCD碼由4位十六進(jìn)制數(shù)組成,ROM中的每個(gè)存儲(chǔ)單元可存放2位十六進(jìn)制數(shù),所以每個(gè)BCD碼占用2個(gè)存儲(chǔ)單元,32個(gè)BCD碼共占用64個(gè)存儲(chǔ)單元.由此可令ROM的低端地址00,H~1F,H存儲(chǔ)電壓值對(duì)應(yīng)的高4位BCD碼d_bcdh,ROM的高端地址20,H~3F,H存儲(chǔ)電壓值對(duì)應(yīng)的低4位BCD碼d_bcdl.而ROM地址與d_adch和d_adcl的對(duì)應(yīng)關(guān)系為:用d_adch乘以2作為ROM地址addr_h1,用d_adcl乘以2再加上偏移量20,H作為ROM地址addr_l1.

計(jì)算ROM地址的VHDL程序如下:

表1 數(shù)字電壓、模擬電壓與ROM地址、ROM數(shù)據(jù)的對(duì)應(yīng)關(guān)系Tab. 1 Correspondence among digital voltage,analog voltage,ROM address and ROM data

4 BCD碼加法運(yùn)算原理

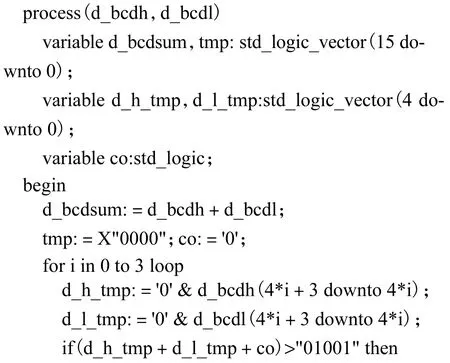

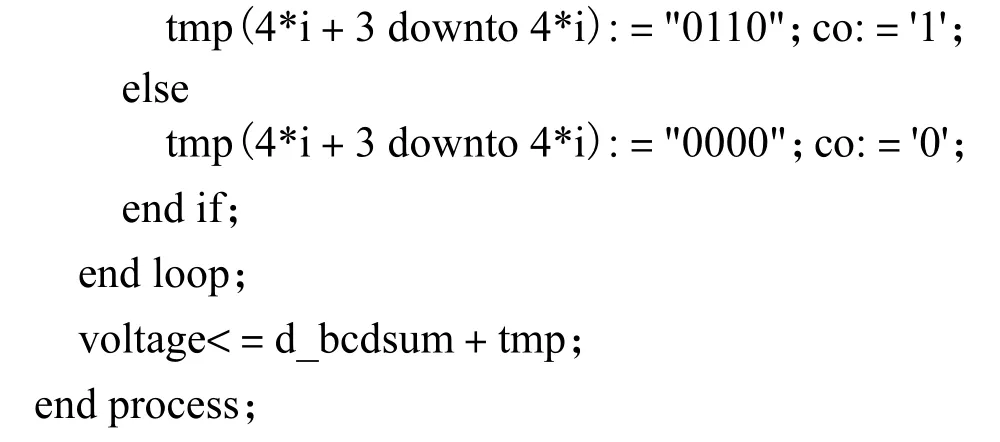

2個(gè)十進(jìn)制數(shù)相加逢十進(jìn)一,2個(gè)十六進(jìn)制數(shù)相加逢十六進(jìn)一,為了使2個(gè)與電壓值對(duì)應(yīng)的BCD碼在進(jìn)行加法運(yùn)算時(shí)能夠逢十進(jìn)一,需要對(duì)運(yùn)算規(guī)則進(jìn)行調(diào)整:設(shè)1個(gè)16位的中間變量tmp用于存儲(chǔ)調(diào)整值,設(shè)最低位的進(jìn)位位co=0.按照從低位到高位的順序,將2個(gè)BCD碼相同位之和與co相加.當(dāng)結(jié)果大于1,001(9)時(shí),tmp與之相同位賦值0,110(6),并使相鄰高位的co=1;當(dāng)結(jié)果小于等于1,001(9)時(shí),tmp與之相同位賦值0,000,并使相鄰高位的co=0.循環(huán)4次后將2個(gè)BCD碼之和與tmp按二進(jìn)制數(shù)相加,所得結(jié)果的十六進(jìn)制數(shù)表示即為2個(gè)BCD碼之和.VHDL程序段如下:

——大于9時(shí)需加6,且向高位有進(jìn)位

以模擬電壓2.483V為例,經(jīng)由AD轉(zhuǎn)換后得到數(shù)字電壓d_adc為10,111,111,查表1可知,高4位1,011對(duì)應(yīng)的ROM地址addr_h1為16,H、addr_h2為17,H,其中存放的數(shù)據(jù)d_bcdh為2,288,H;低4位1,111對(duì)應(yīng)的ROM地址addr_l1為3E,H、addr_l2為3F,H,其中存放的數(shù)據(jù)d_bcdl為0,195,H.對(duì)這2個(gè)BCD碼進(jìn)行加法運(yùn)算,最終得到BCD碼2,483,H與模擬電壓值完全一致,只是在最高位后面缺小數(shù)點(diǎn),這個(gè)問題只需在數(shù)碼管顯示控制模塊seg7中不僅點(diǎn)亮相應(yīng)數(shù)字的段,而且點(diǎn)亮最高位數(shù)碼管的點(diǎn)即可解決.

5 硬件測(cè)試

數(shù)字電壓表的硬件測(cè)試在合眾達(dá)SEED-XDTK FPGA教學(xué)實(shí)驗(yàn)平臺(tái)上進(jìn)行,所用FPGA器件為Xilinx公司的XC4VSX25.在Xilinx集成開發(fā)環(huán)境ISE10.1中對(duì)工程進(jìn)行綜合、實(shí)現(xiàn)、產(chǎn)生可編程文件后下載(配置目標(biāo)器件)到實(shí)驗(yàn)平臺(tái)上.用萬(wàn)用表(倍思特?cái)?shù)字萬(wàn)用表DT–9205,20V檔,精確到小數(shù)點(diǎn)后2位)和本設(shè)計(jì)實(shí)現(xiàn)的數(shù)字電壓表(精確到小數(shù)點(diǎn)后3位)檢測(cè)并顯示實(shí)驗(yàn)平臺(tái)上6個(gè)測(cè)試點(diǎn)的電壓值,結(jié)果見表2.測(cè)量的相對(duì)誤差小于3%.

VHDL Programming and Hardware Realization of the Digital Voltmeter

LI Yajun,XU Shichao,HUANG Jianmin,WANG Jie,MA Qiang

(College of Electronic Information and Automation,Tianjin University of Science & Technology,Tianjin 300222,China)

Combining FPGA with ADC TLV571,a digital voltmeter was designed. The analog voltage measurement,analog-digital conversion,computing and reading were realized with VHDL language. TLV571,was controlled by FPGA with a state machine. The digital voltage and BCD codes of analog voltage are in one-to-one correspondence with the ROM address and data. Using the look-up tables,the highest four bit BCD codes and the lowest four bit BCD codes can be read from corresponding ROM addresses and then the analog voltage can be computed through the addition operation of the two BCD codes. Experiments with experimental platform confirmed the validity of the digital voltmeter’s design.

FPGA;VHDL;ADC;BCD code

TP332.1

A

1672-6510(2014)01-0065-04

10.13364/j.issn.1672-6510.2014.01.013

2013–08–21;

2013–11–04

天津市教育科學(xué)“十二五”規(guī)劃課題(HEYP6021);天津科技大學(xué)實(shí)驗(yàn)室開放基金資助項(xiàng)目(1202A301)

李亞峻(1973—),女,內(nèi)蒙古包頭人,講師,lyj_2872@sohu.com.