FPGA上抗側信道攻擊的密碼算法實現*

王 松,陳 曼,韓煉冰,段俊紅,劉鴻博

(中國電子科技集團公司第三十研究所,四川成都610041)

FPGA上抗側信道攻擊的密碼算法實現*

王 松,陳 曼,韓煉冰,段俊紅,劉鴻博

(中國電子科技集團公司第三十研究所,四川成都610041)

密碼算法在運行時可能會受到側信道攻擊,抗側信道攻擊的FPGA密碼算法實現是目前研究的一個熱點。通過隨機數保護關鍵數據的S盒移位掩碼法被認為是一種有效的防御手段。采用該方式實現的密碼算法在提高運行安全性的同時,可能會帶來硬件資源開銷的增加及加解密速度的降低。通過對SM4算法的實現表明,采用合適的實現方式時S盒移位掩碼法抗側信道攻擊實現對算法硬件資源開銷及加解密速度影響不是太大,具有一定的實用價值。

側信道密碼分析 FPGA 實現

0 引 言

密碼算法是信息安全的關鍵技術之一,成熟的密碼算法在數學理論上都具有很強的安全性,然而在密碼算法實際運行時,硬件電路會泄漏出與邏輯0和邏輯1相關的電磁輻射、功耗波動等側信道信息。密碼算法的側信道攻擊就是指利用這些泄露出來的側信道信息,再利用密碼學、統計學原理,分析和破譯密鑰信息[1]。國內外對側信道攻擊技術的研究已經取得非常大的進展,發展出了一系列的分析方式,如功耗分析,電磁分析和時間分析等,其中比較成熟有效的側信道分析方式是功耗分析技術,主要有簡單功耗分析(SPA,Simple Power Analysis)和差分功耗分析(DPA,Differential Power Analysis)以及高階功耗分析((Ho-DPA,High order Differential Power Analysis)[2]。

隨著密碼算法側信道攻擊技術的提高,對應的抗側信道攻擊技術也在與時俱進的發展。目前基于FPGA抗側信道攻擊密碼算法實現的方法有時鐘擾亂法、高頻電路法、寬總線查表法和掩碼法等。掩碼法又分為S盒計算掩碼法和S盒移位掩碼法。

時鐘擾亂法通過時鐘頻率的隨機變化來對功耗進行擾亂,使得攻擊者無法將時鐘信號和功耗曲線對準,隱藏密碼算法運行的內部信息,達到抗側信道攻擊的目的。高頻電路法的原理是通過提高芯片的工作頻率使得攻擊者準確找到注入點進行側信道分析的難度加大。寬總線設計法通過增加S盒輸入輸出位寬使得攻擊者遍歷密鑰比特串的復雜度呈指數增長。S盒計算掩碼法要求S盒是由有限域上的求逆運算或仿射變換等方式構成,其原理是在S盒求逆等運算中加入保護措施。S盒移位掩碼法通過加入隨機數掩碼并改變S盒中數據的存儲順序使得側信道攻擊時對功耗曲線的分析困難,從而達到抗側信道攻擊的目的。

隨著示波器等能量分析設備精度提高,時鐘擾亂法、高頻電路法已經不再安全。寬總線查表法的安全性依賴于計算的復雜度,然而隨著計算機性能的提升,寬總線查表法也越來越不安全。S盒計算法要求S盒是由某種運算產生,其應用場景受限。S盒移位掩碼法目前還沒有特別明顯的缺陷,是當前的一個研究熱點。本文以分組密碼算法SM4的實現為例比較了S盒移位掩碼法與傳統不具有抗側信道攻擊能力的實現方法在資源開銷和加解密速度方面的差異,并分析了S盒移位掩碼法在工程實現上的實用性。

1 盒移位掩碼法

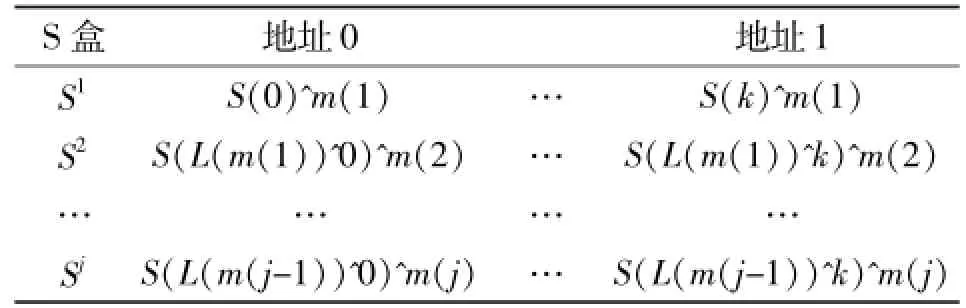

在分組密碼算法中,其加解密或密鑰擴展輪函數Y=R(x)總能表示成Y=L(S(x))的形式,其中L(.)表示密碼算法輪函數中的線性運算部分,S(.)表示密碼算法輪函數中的非線性運算部分,即通常說的S盒。S盒的設計直接決定了密碼算法的抗側信道攻擊能力[3]。S盒移位掩碼法通過對S盒中原始數據與掩蓋隨機數m進行異或掩蓋,并隨機化S盒的存儲位置來保護S盒查表輸出結果,使得側信道攻擊者無法直接得到S盒中的原始數據,能有效的阻止對密碼算法運行時的側信道攻擊[4]。假設一個分組密碼算法中S盒中有k個數據,輪運算次數為j,Si為第i輪的S盒,表1描述了該S盒采用S盒移位掩碼法實現后的結果。

表1 S盒移位掩碼法的實現Table 1 One way of masking schemes

從表1中可以看出,密碼算法每輪運算使用的S盒都被不同的隨機數掩蓋保護,使得運行時每輪運算產生的電磁輻射或功耗等側信道信息都不相同,增加了分析的復雜度。即使攻擊者解析出了中間某一輪運算數據,也不能直接得到其它運算輪次的輸出信息。

在FPGA平臺上采用傳統不具有抗側信道攻擊能力的方法實現密碼算法時,S盒中的數據一般按照S(0),S(1)…S(k-2)S(k-1)的方式順序從低地址到高地址依次存放。采用S盒掩碼法實現時,S盒中的數據被掩蓋隨機數m掩蓋并改變存儲順序,第i(i≠0)輪從低地址到高地址的存儲順序變為S(L(m(i-1))^0),S(L(m(i-1))^1)…S(L(m(i-1))^(k-1))。

2 具體實現方式

在FPGA中采用傳統不具備抗側信道攻擊能力的方式實現密碼算法時,一般會復用密碼算法的輪運算單元,資源占用開銷與算法的運算輪數沒有太大關系。

采用S盒掩碼法實現時,由于每輪運算的S盒數據被不同的隨機數掩蓋且存儲順序不同,輪運算模塊不能直接復用。具體實現時可以有以下三種實現方式。

方式一、每輪運算完成時,對S盒中的數據采用下一輪的掩蓋隨機數重新掩蓋并按照新的順序存儲到存儲塊中,再開始下一輪的運算。

方式二、設計兩倍的S盒存儲塊,一份存儲塊存儲當前正在使用的S盒,另一份存儲塊存儲下一輪將要使用的S盒。算法運行時兩份存儲塊采用乒乓操作實現S盒的使用和更新,即算法在使用其中一份存儲塊中的S盒進行加解密運算時,另一份存儲塊中的S盒可以同時進行數據的更新,為下一輪的運算做準備。

方式三、按照密碼算法的運算輪數實現多個輪運算模塊。算法初始化時,每個輪運算模塊中的S盒分別使用對應的隨機數進行掩蓋。算法運行時直接使用已經掩蓋好的S盒。采用該方式實現的S盒只有在更換掩蓋隨機數或更新S盒參數時才需要對S盒重新初始化。

密碼算法實現時,S盒一般由FPGA內部的雙口RAM實現,設S盒的數據位寬為n,存儲塊完成一次數據更新至少需要2n/2個時鐘周期。比如位寬為8位的S盒,完成一次更新至少需要28/2=128個時鐘周期。

方式一實現的密碼算法每輪運算完成后需要消耗2n/2個時鐘周期進行S盒數據更新,密碼算法的加解密速度將嚴重下降,在實際工程實現中不具有實用性。

方式二實現的密碼算法由于采用了乒乓操作,密碼算法輪運算和下一輪的S盒數據更新可以同時進行,然而通常情況下密碼算法的輪運算僅需要幾個時鐘即可完成運算,算法運行的瓶頸還是在數據更新上。每輪運算依然至少需要2n/2個時鐘周期,該方法依然不具有實用性。

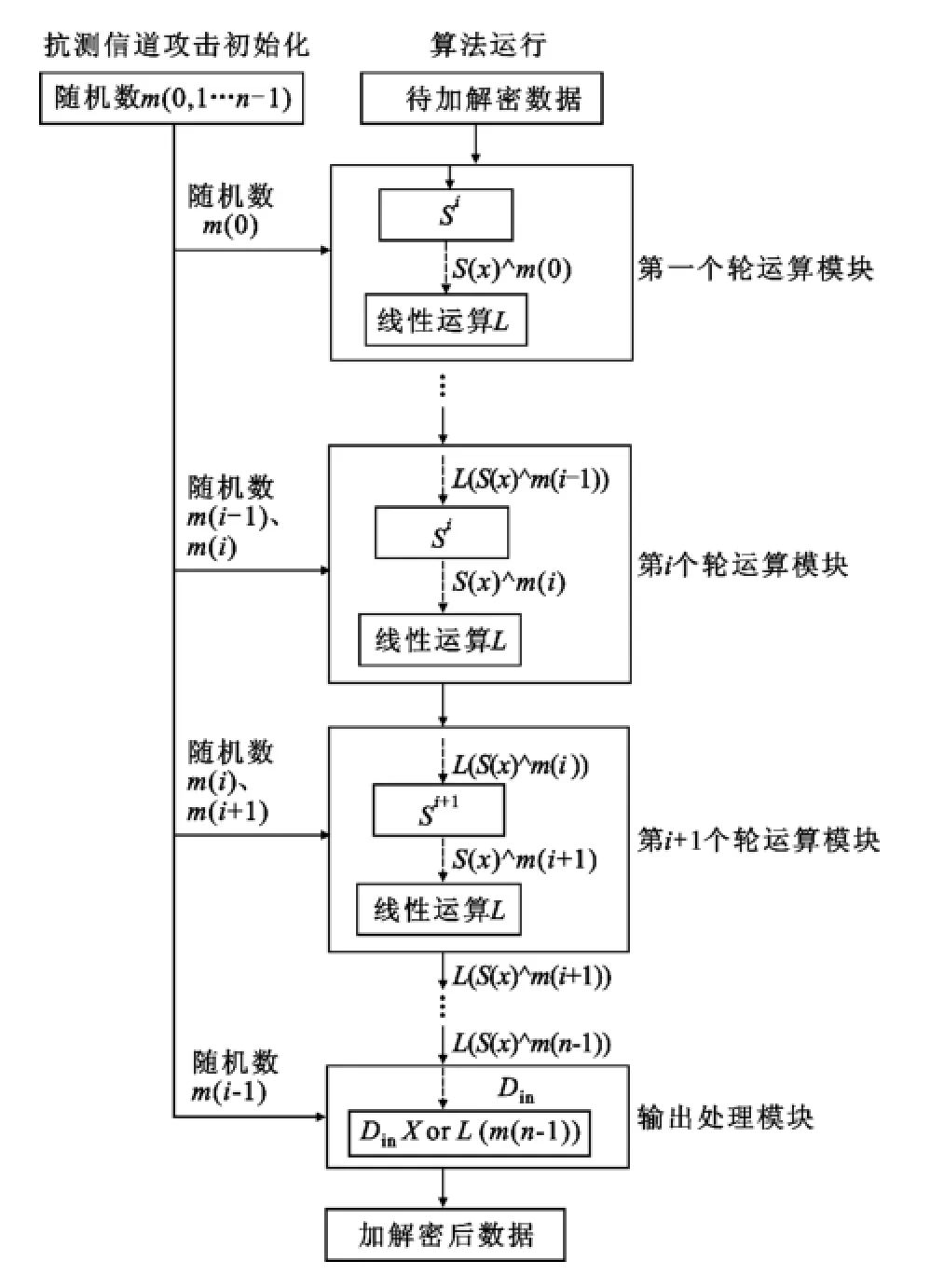

方式三將每個輪運算模塊的S盒在算法初始化時預先一次性置入。采用這種方式實現的密碼算法由于在運行時不再需要更新S盒中的數據,不會增加時鐘開銷。在資源開銷方面,由于了輪運算模塊被實現了多份,FPGA中寄存器、查找表和存儲塊等硬件資源的開銷會與算法輪數成正比增加。假設待實現的密碼算法有n次輪運算,采用方式三實現時硬件電路原理圖如圖1所示。

圖1 采用方式三實現的硬件電路原理Fig.1 Schematic circuit diagram in method three

從圖1中可以看到,采用方式三實現的硬件電路中每個輪運算模塊完成一次輪運算的處理,上一個輪運算模塊的輸出結果直接進入到下一個輪運算模塊中繼續處理,直到完成所有的輪運算。最后一個輪運算模塊的輸出結果由輸出處理模塊做一次去掩碼處理后即可得到加解密的結果。

3 SM4算法的實現

SM4抗側信道攻擊實現選用的FPGA芯片型號為Atera公司的EP3SE50F484C4,編譯器及版本為Quartus II 11.1(32-Bit),仿真軟件及版本為Modelsim SE 6.5。

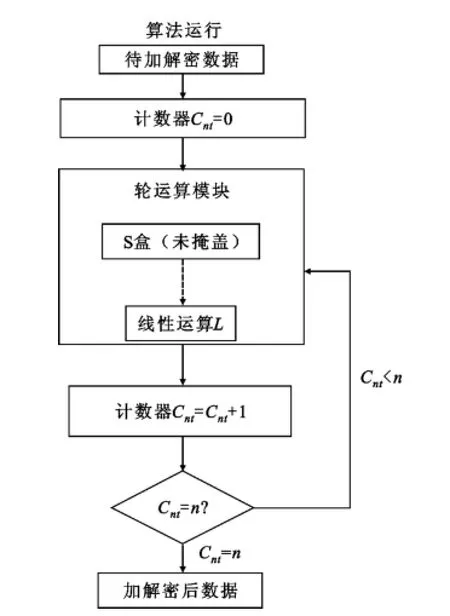

作為比對樣本的常規實現方式電路在硬件設計上僅實現一個輪運算單元,其硬件電路原理圖如圖2所示。

圖2 采用常規方式實現的硬件電路原理Fig.2 Schematic circuit diagram in customarily

圖2所示中硬件電路加解密數據時,算法核循環調用輪運算模塊,并通過計數器對輪運算的次數進行計數,當完成指定次數的輪運算后,輸出加解密后的數據。

FPGA中算法運行的理論最大處理速度可用公式V=(W/N)×F計算。F為算法在FPGA中運行的理論最高工作頻率,N為待加解密數據從輸入算法核到完成加解密后輸出算法核所消耗的時鐘周期數,W為每次運算處理的分組長度[5]。算法的硬件資源消耗及理論最高工作頻率情況由編譯器給出。實驗結果如表2所示。

表2 實驗結果Table 2 Experiment result

表2中各項數據后面百分比指的是該資源消耗量占芯片中此類資源總量的比例。從測試數據可以看出采用方式三實現的密碼算法對算法的加解密速度影響不大。查找表和存儲資源開銷較大,主要是由于采用方式三實現密碼算法時將硬件電路進行了展開從而增加了資源開銷,但從占芯片資源總量百分比來看,占整個芯片資源的總量比例并不高。

此外,采用方式三實現的硬件電路在處理ECB模式的密碼算法時還可以按照流水的方式處理,進一步提高算法的加解密性能。

4 結 語

抗側信道攻擊的密碼算法實現是今后密碼算法實現的一個趨勢。采用抗側信道攻擊方式實現的密碼算法在滿足抗側信道攻擊的同時,在硬件開銷和加解密性能上還必須具有可用性。對SM4算法的實驗表明采用圖1方式實現的S盒移位掩碼法抗側信道攻擊實現方式合理,對算法的加解密速度沒有太大影響。硬件資源的開銷與傳統不具有抗側信道攻擊能力的算法實現方式相比有較大增加,但占整個芯片資源的總量比例并不大,當芯片資源較富余時具有較大的實用價值。

[1] 成為,谷大武,郭箏,等.一種針對RSA-CRT的功耗分析攻擊方法[J].通信技術,2011,44(06):123-125, 128.

CHENG Wei,GU Da-wu,GUO Zheng,ZHANG Lei.A Power Analysis Attack Against RSA-CRT[J].Communications Technology,2011(06):123-125,128.

[2] 陳廷定.密碼芯片的側信道安全性分析和量化評估[D].濟南:山東大學,2010.

CHEN Yan-ding.Analysis and Quantitative Evaluation of Side Channel Security on Crypto Chips[D].Jinan:Shandong university,2010.

[3] 常小龍,丁國良,武翠霞,等.抗電磁側信道攻擊的AESS盒設計[J].計算機工程,2011(17):93-95.

CHANG Xiao-long,DING Guo-liang,WU Cui-xia,et al.Design of AES S-box Against Electromagnetic Sidechannel Attacks[J].Computer Engineering,2011(17): 93-95.

[4] 彭濤,王栓杰,席偉,等.FPGA密碼芯片改進掩碼防護方法研究[J].信息技術,2011(11):31-33.

PENG Tao,WANG Shuanjie,XI Wei,et al.Research on Improved Masking Technique based on FPGA Cryptographic chip[J].Information Technology,2011(11):31-33.

[5] 王松,韓煉冰,段俊紅.布爾函數法實現S盒在FPGA中的應用[J].信息安全與通信保密,2013(09):90-91.

WANG Song,HAN Lian-bing,DUAN Jun-hong.Application of Implement S Box in FPGA Based on Boolean Function[J].Information Security and Communications Privacy,2013(9):90-91.

WANG Song(1985-),male,B.Sci.,engineer,majoring in embedded system and communications security technology.

陳 曼(1988—),女,碩士,工程師,主要研究方向為信息安全;

CHEN Man(1988-),female,M.Sci.,engineer,majoring in information security.

韓煉冰(1984—),男,學士,工程師,主要研究方向為嵌入式系統、通信安全技術;

HAN Lian-bing(1984-),male,B.Sci.,engineer,majoring in embedded system,and communications security technology.

段俊紅(1984—),男,學士,工程師,主要研究方向為嵌入式系統、通信安全技術;

DUAN Jun-hong(1984-),male,B.Sci.,engineer,majoring in embedded system,and communications security technology.

劉鴻博(1981—),女,學士,工程師,主要研究方向為信息安全。

LIU Hong-bo(1981-),female,B.Sci.,engineer,majoring in information security.

Side-Channel Resistance Implementation for FPGA

WANG Song,CHEN Man,HAN Lian-bing,DUAN Jun-hong,LIU Hong-bo

(NO.30 Institute of CETC,Chengdu Sichuan 610041,China)

As the cryptographic algorithm is vulnerable to side-channel analysis during its operation,sidechannel resistance implementation for FPGA now becomes a hotspot of study.To counter this analysis, masking scheme in randomizing key-dependent data by addition of one or several random value(s)(the masks)is usually involved.This method may increase the hardware overhead and reduce the work efficiency while improving the security.SM4 implemented on an Altera FPGA by using certain masking scheme with location randomization indicates that the masking scheme does have certain influence on hardware overhead and work efficiency,but this is acceptable when area cost is not strictly limited.Experiment indicates that this masking scheme is of practical value in implementing crypto algorithm.

side-channel cryptanalysis;FPGA;implementation

TN791

A

1002-0802(2014)09-1100-04

10.3969/j.issn.1002-0802.2014.09.025

王 松(1985—),男,學士,工程師,主要研究方向為嵌入式系統、通信安全技術;

2014-06-11;

2014-07-28 Received date:2014-06-11;Revised date:2014-07-28